FPGA系统中线缆连接的自动装配方法、电子设备和介质与流程

本发明涉及芯片,尤其涉及一种fpga系统中线缆连接的自动装配方法、电子设备和介质。

背景技术:

1、现场可编程门阵列(field-programmablegatearray,简称fpga)系统中通常提供有默认的线缆装配方案,该方案均衡使用了fpga之间的线缆连接资源。然而,不同的芯片设计方案具有各种各样的特性和风格,各个fpga之间的连接线缆的类型和数量,用户设计的顶层端口在fpga上的管脚分配等需求可能各不相同。而默认的线缆装配方案往往不能达到最佳的性能,降低了fpga系统的运行效率。由此可知,如何实现fpga系统中的线缆连接的合理装配,提高fpga系统的运行效率成为亟待解决的技术问题。

技术实现思路

1、本发明目的在于,提供一种fpga系统中线缆连接的自动装配方法、电子设备和介质,实现fpga系统中的线缆连接的合理装配,提高了fpga系统的运行效率。

2、根据本发明第一方面,提供了一种fpga系统中线缆连接的自动装配方法,所述fpga系统包括k个具有互联关系的fpga对(fi,fj),fi为fpga系统中的第i个fpga,fj为fpga系统中的第j个fpga,i和j的取值范围均为1到n,n为fpga系统中fpga的总数,i≠j;

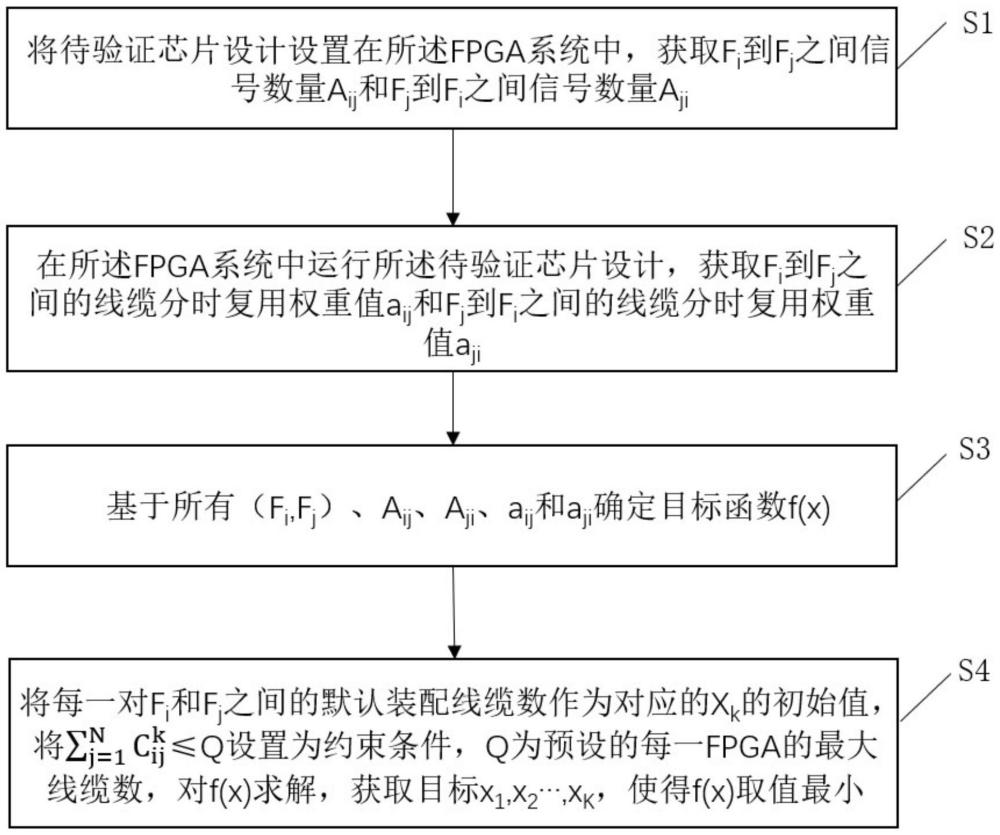

3、所述方法包括:

4、步骤s1、将待验证芯片设计设置在所述fpga系统中,获取fi到fj之间信号数量aij和fj到fi之间信号数量aji;

5、步骤s2、在所述fpga系统中运行所述待验证芯片设计,获取fi到fj之间的线缆分时复用权重值aij和fj到fi之间的线缆分时复用权重值aji;

6、步骤s3、基于所有(fi,fj)、aij、aji、aij和aji确定目标函数f(x):

7、

8、其中,mk为第k对(fi,fj)对应的线缆分时复用参数,xk为第k对(fi,fj)对应的装配线缆数cijk,k的取值范围为1到k,k为所述fpga系统中具有互联关系的fpga对的总数,,为第k对(fi,fj)对应的线缆时分复用率,mk=aijk*aijk+ajik*ajik,aijk为第k对(fi,fj)对应的aij,aijk为第k对(fi,fj)对应的aij,ajik为第k对(fi,fj)对应的aji,ajik为第k对(fi,fj)对应的aji;

9、步骤s4、将每一对fi和fj之间的默认装配线缆数作为对应的xk的初始值,将设置为约束条件,q为预设的每一fpga的最大线缆数,对f(x)求解,获取目标x1,x2…,xk,使得f(x)取值最小。

10、根据本发明第二方面,提供一种电子设备,包括:至少一个处理器;以及,与所述至少一个处理器通信连接的存储器;其中,所述存储器存储有可被所述至少一个处理器执行的指令,所述指令被设置为用于执行本发明第一方面所述的方法。

11、根据本发明第三方面,提供一种计算机可读存储介质,所述计算机指令用于执行本发明第一方面所述的方法。

12、本发明与现有技术相比具有明显的优点和有益效果。借由上述技术方案,本发明提供的一种fpga系统中线缆连接的自动装配方法、电子设备和介质可达到相当的技术进步性及实用性,并具有产业上的广泛利用价值,其至少具有以下有益效果:

13、本发明能够基于待验证芯片设计本身实现fpga系统中的线缆连接的合理装配,提高了fpga系统的运行效率。

技术特征:

1.一种fpga系统中线缆连接的自动装配方法,其特征在于,

2.根据权利要求1所述的方法,其特征在于,

3.根据权利要求2所述的方法,其特征在于,

4.根据权利要求2所述的方法,其特征在于,

5.根据权利要求1所述的方法,其特征在于,

6.根据权利要求5所述的方法,其特征在于,

7.根据权利要求6所述的方法,其特征在于,

8.一种电子设备,其特征在于,包括:

9.一种计算机可读存储介质,其特征在于,存储有计算机可执行指令,所述计算机可执行指令用于执行前述权利要求1-7中任一项所述的方法。

技术总结

本发明涉及芯片技术领域,尤其涉及一种FPGA系统中线缆连接的自动装配方法、电子设备和介质,方法包括:步骤S1、将待验证芯片设计设置在FPGA系统中,获取F<subgt;i</subgt;到F<subgt;j</subgt;之间信号数量A<subgt;ij</subgt;和F<subgt;j</subgt;到F<subgt;i</subgt;之间信号数量A<subgt;ji</subgt;;步骤S2、在FPGA系统中运行待验证芯片设计,获取线缆分时复用权重值a<subgt;ij</subgt;和a<subgt;ji</subgt;;步骤S3、确定目标函数f(x);步骤S4、将每一对F<subgt;i</subgt;和F<subgt;j</subgt;之间的默认装配线缆数作为对应的X<subgt;k</subgt;的初始值,将设置为约束条件,对f(x)求解,获取目标x<subgt;1</subgt;,x<subgt;2</subgt;…,x<subgt;K</subgt;,使得f(x)取值最小。实现FPGA系统中的线缆连接的合理装配,提高了FPGA系统的运行效率。

技术研发人员:柯宪明,宋宇,黄建锋

受保护的技术使用者:上海合见工业软件集团有限公司

技术研发日:

技术公布日:2024/11/14

- 还没有人留言评论。精彩留言会获得点赞!