基于全电子联锁系统的二乘二取二平台的同步方法与流程

本发明涉及电子联锁系统的,尤其涉及一种基于全电子联锁系统的二乘二取二平台的同步方法。

背景技术:

1、计算机全电子联锁系统二乘二取二系统由两系组成,两系以热备方式运行,每系采用双 cpu 运行系统软件,在硬件上完全实现了比较和冗余,提高了系统的安全性和可靠性。虽然二乘二取二系统在系统的可靠性和安全性都相比双机热备系统有了很大程度的提高,然而作为计算机全电子联锁系统核心的联锁软件仍是采用单套软件,系统每系的两个cpu 同时运行相同的联锁软件进行同步输出比较。

2、计算机全电子联锁系统的二取二冗余结构大多采用的是同构模式,即两个 cpu软件完成的功能完全相同,这样的冗余结构符合失效-安全原则,且只有当两个单元取得一致时才能够执行规定的功能,否则导向安全状态,可以排除同样差错结构的多重非共因故障,其中单系二取二结构参照图 1,但是此结构可能对部分共因故障无法消除。

3、为了能够排除共因故障,异构模式的二取二模式被提出,即两个 cpu 运行联锁模式不同,通过多样性提高软件的安全性,异构结构参照图2。但是此结构仍然存在一些缺点:异构性增加了开发成本和周期,提高了研发验证的难度,对结构的同步性也提出了很高的要求。

4、为此,本发明的设计者有鉴于上述缺陷,通过潜心研究和设计,综合长期多年从事相关产业的经验和成果,研究设计出一种基于全电子联锁系统的二乘二取二平台的同步方法,以克服上述缺陷。

技术实现思路

1、本发明的目的在于提供一种基于全电子联锁系统的二乘二取二平台的同步方法,能有效克服现有技术的缺陷,保证了在异构模式的情况下,有效保证联锁二乘二取二的同步机制正常运行,从而从最大程度上确保运行过程中,影响系统安全的故障被识别而同步失败导致的误判被降低。

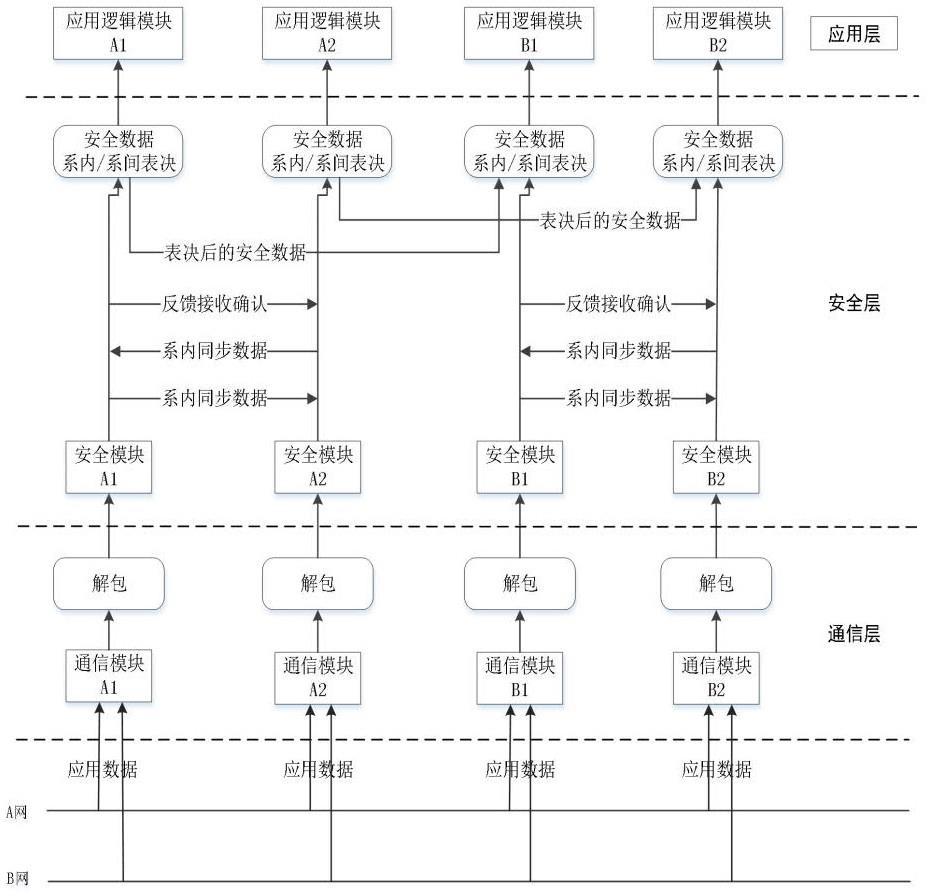

2、为实现上述目的,本发明公开了一种基于全电子联锁系统的二乘二取二平台的同步方法,设有四个cpu模块,两两为一组,其中一组为主系cpu,另一组为备系cpu,该同步方法包含输入步骤和输出步骤,其特征在于:所述输入步骤包括以下步骤:

3、步骤一:在各cpu的通信层的通信模块收到下位机状态或上位机指令等输入信息包时,分别将输入信息包送至解包模块进行解包;

4、步骤二:解包后的输入信息包分别送至cpu的安全层进行同步表决;

5、步骤三:主系的两cpu的安全层和备系的两cpu的安全层分别将解包后输入信息包发送给各自的应用逻辑层的应用逻辑模块进行具体操作;

6、其中所述输出步骤包括以下步骤:

7、步骤一:在收到安全层给出的运算指令和执行周期性运算工作时,各cpu的逻辑应用层的应用逻辑模块需要形成输出数据包,以将输出下位机操作指令和周期性输出设备状态指令进行输出;

8、步骤二:将输出信息包分别送至cpu的安全层进行同步表决;

9、步骤三:主系的两cpu的安全层和备系的两cpu的安全层分别将输出信息包发送给通信层,通信层进行组包后通过通信模块进行输出。

10、其中:输入和输出步骤的同步表决包含如下子步骤:

11、步骤2.1进行加密,准备进行同步表决,即主系的两cpu的安全层之间和备系的cpu的安全层之间采用加密码方式准备进行输入信息包的数据同步表决,各安全层根据输入信息包进行加密,分别形成加密数据包;

12、步骤2.2系内进行同步表决,主系的两cpu的安全层之间和备系的cpu的安全层之间对加密数据包进行比对,若主系的加密数据包对应后说明主系同步表决成功,同时备系的加密数据包对应后说明备系同步表决也成功,进入步骤2.5;若主系同步表决不成功和/或备系同步表决不成功,则进入步骤2.3;

13、步骤2.3在表决不成功的主系和/或备系的两cpu的安全层之间通过选择性表决来进行进一步表决,若选择性表决后主系和备选均同步成功则进入步骤2.5,若主系同步成功而备系同步不成功则进入步骤2.4,若主系同步不成功而备系同步成功则系间互换,即备系的两cpu转为主系,原主系的两cpu转为备系,进入步骤2.4,若主系和备系均数据同步不成功则直接退出,结束整个任务;

14、步骤2.4用主系数据重构备系数据后进入步骤三;

15、步骤2.5判断主备系之间状态是否同步,即主系cpu1a1和主系cpu2a2以及备系cpu1b1和备系cpu2b2之间是否同步,同步则进入步骤三,如果不同步,进入步骤2.4。

16、其中:加密数据包的字节固定且数值不同,能有效降低数据同步表决的时间,提高效率。

17、其中:加密数据包采用两个不同多项式的32位长crc。

18、其中:需要进行数据同步表决的数据可以表示为一个字节数组,对此数组的数据用两个不同多项式进行crc32校验,分别得出一个8字节的校验和,系内两个cpu比较的数据是这两个8字节一共16字节的校验和,这样,无论比较的字节数组的长度是多少个字节,在网络上传输的比较数据都将只是这16字节的校验和,极大的提高了安全性能。

19、其中:所述选择性表决为:允许对收到同一个通信过程中来的多帧数据进行选择性表决,表决时暂存多个周期的数据进行交叉比较并获取比较成功的最新数据,得到系内共有数据中比较成功部分。

20、其中:交叉比较时,系内两个cpu分别包含最新3个周期的数据,先用其中一个的第一条数据,去比较另一个的三条数据,如存在相同的数据,则比较成功,如不成功,继续用其中一个的第二条数据去比较,如不成功,则继续用其中一个第三条数据去比较,如果均不成功,则认为数据同步表决失败,如表决成功,则认为数据同步成功。

21、其中:其中主系数据重构备系数据具体为:首先由主系发起同步,主系cpu1向备系cpu1发送同步数据,主系cpu2向备系cpu2发送同步数据,各备系cpu对接收到的数据进行同步表决,如果不成功,发起重构申请,当主系cpu均收到备系重构请求后,主系cpu1和主系cpu2分别向备系cpu1和备系cpu2发送重构数据,备系cpu1和cpu2收到重构数据后,重构自身数据。

22、通过上述内容可知,本发明的基于全电子联锁系统的二乘二取二平台的同步方法具有如下效果:

23、1、采用加密码方式进行数据同步表决,无论数据长短,,将表决内容固定在16个字节加密码字节固定且数值不同,有效降低数据同步表决的时间,提高效率。

24、2、采用多种方式在多线程中同步比较数据,对于异步情况下,使用选择性比较,降低了系统的误判,挺高了软件的可用性。

25、3、采用的系间重构方式是在不正确时重构,区别于传统的周期同步,降低cpu运算负荷,挺高网络带宽利用率。

26、4、采用的双crc校验,保证漏检差错概率约等于0。

27、5、采用的选择性表决机制,保证了临界变化时,正确状态的输出。

28、本发明的详细内容可通过后述的说明及所附图而得到。

技术特征:

1.一种基于全电子联锁系统的二乘二取二平台的同步方法,设有四个cpu模块,两两为一组,其中一组为主系cpu,另一组为备系cpu,该同步方法包含输入步骤和输出步骤,其特征在于:所述输入步骤包括以下步骤:

2.如权利要求1所述的基于全电子联锁系统的二乘二取二平台的同步方法,其特征在于:输入和输出步骤的同步表决包含如下子步骤:

3.如权利要求2所述的基于全电子联锁系统的二乘二取二平台的同步方法,其特征在于:加密数据包的字节固定且数值不同,能有效降低数据同步表决的时间,提高效率。

4.如权利要求2所述的基于全电子联锁系统的二乘二取二平台的同步方法,其特征在于:加密数据包采用两个不同多项式的32位长crc。

5.如权利要求3或4所述的基于全电子联锁系统的二乘二取二平台的同步方法,其特征在于:需要进行数据同步表决的数据可以表示为一个字节数组,对此数组的数据用两个不同多项式进行crc32校验,分别得出一个8字节的校验和,系内两个cpu比较的数据是这两个8字节一共16字节的校验和,这样,无论比较的字节数组的长度是多少个字节,在网络上传输的比较数据都将只是这16字节的校验和,极大的提高了安全性能。

6.如权利要求2所述的基于全电子联锁系统的二乘二取二平台的同步方法,其特征在于:所述选择性表决为:允许对收到同一个通信过程中来的多帧数据进行选择性表决,表决时暂存多个周期的数据进行交叉比较并获取比较成功的最新数据,得到系内共有数据中比较成功部分。

7.如权利要求6所述的基于全电子联锁系统的二乘二取二平台的同步方法,其特征在于:交叉比较时,系内两个cpu分别包含最新3个周期的数据,先用其中一个的第一条数据,去比较另一个的三条数据,如存在相同的数据,则比较成功,如不成功,继续用其中一个的第二条数据去比较,如不成功,则继续用其中一个第三条数据去比较,如果均不成功,则认为数据同步表决失败,如表决成功,则认为数据同步成功。

8.如权利要求2所述的基于全电子联锁系统的二乘二取二平台的同步方法,其特征在于:其中主系数据重构备系数据具体为:首先由主系发起同步,主系cpu1向备系cpu1发送同步数据,主系cpu2向备系cpu2发送同步数据,各备系cpu对接收到的数据进行同步表决,如果不成功,发起重构申请,当主系cpu均收到备系重构请求后,主系cpu1和主系cpu2分别向备系cpu1和备系cpu2发送重构数据,备系cpu1和cpu2收到重构数据后,重构自身数据。

技术总结

一种基于全电子联锁系统的二乘二取二平台的同步方法,采用加密码方式进行数据同步表决,无论数据长短,将表决内容固定在16个字节加密码字节固定且数值不同,有效降低数据同步表决的时间,提高效率,其采用多种方式在多线程中同步比较数据,对于异步情况下,使用选择性比较,降低了系统的误判,挺高了软件的可用性;由此,本发明有效克服现有技术的缺陷,保证了在异构模式的情况下,有效保证联锁二乘二取二的同步机制正常运行,从而从最大程度上确保运行过程中,影响系统安全的故障被识别而同步失败导致的误判被降低。

技术研发人员:吴正中,张辉,王乐之,张占林,邓能文,姜子旺,武涛

受保护的技术使用者:北京城建智控科技股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!