一种硬件加速电路及芯片的制作方法

本发明涉及芯片设计与应用,特别是涉及一种硬件加速电路及芯片。

背景技术:

1、在芯片内部,处理器通过总线将寄存器配置发送给总线挂载的各个设备,但是设备的寄存器配置在总线上为串行下发,下发的过程通常是由软件基于业务的先后顺序进行配置调度,而软件的执行速度受制于处理器、内存等因素,在对系统时延要求严格、设备执行顺序及设备执行时刻有严格要求的系统中,现有的串行下发很难满足上述需求,通常的做法是在设备之间加入额外的同步处理操作,但是加入同步的方式使各个设备之间很难解耦,极大地限制了使用场景,同时增加了系统的复杂度。

2、应该注意,上面对技术背景的介绍只是为了方便对本申请的技术方案进行清楚、完整的说明,并方便本领域技术人员的理解而阐述的。不能仅仅因为这些方案在本申请的背景技术部分进行了阐述而认为上述技术方案为本领域技术人员所公知。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种硬件加速电路及芯片,用于解决现有技术中如何在互相解耦的要求下,对芯片内部设备进行配置调度实现起来较为困难的问题。

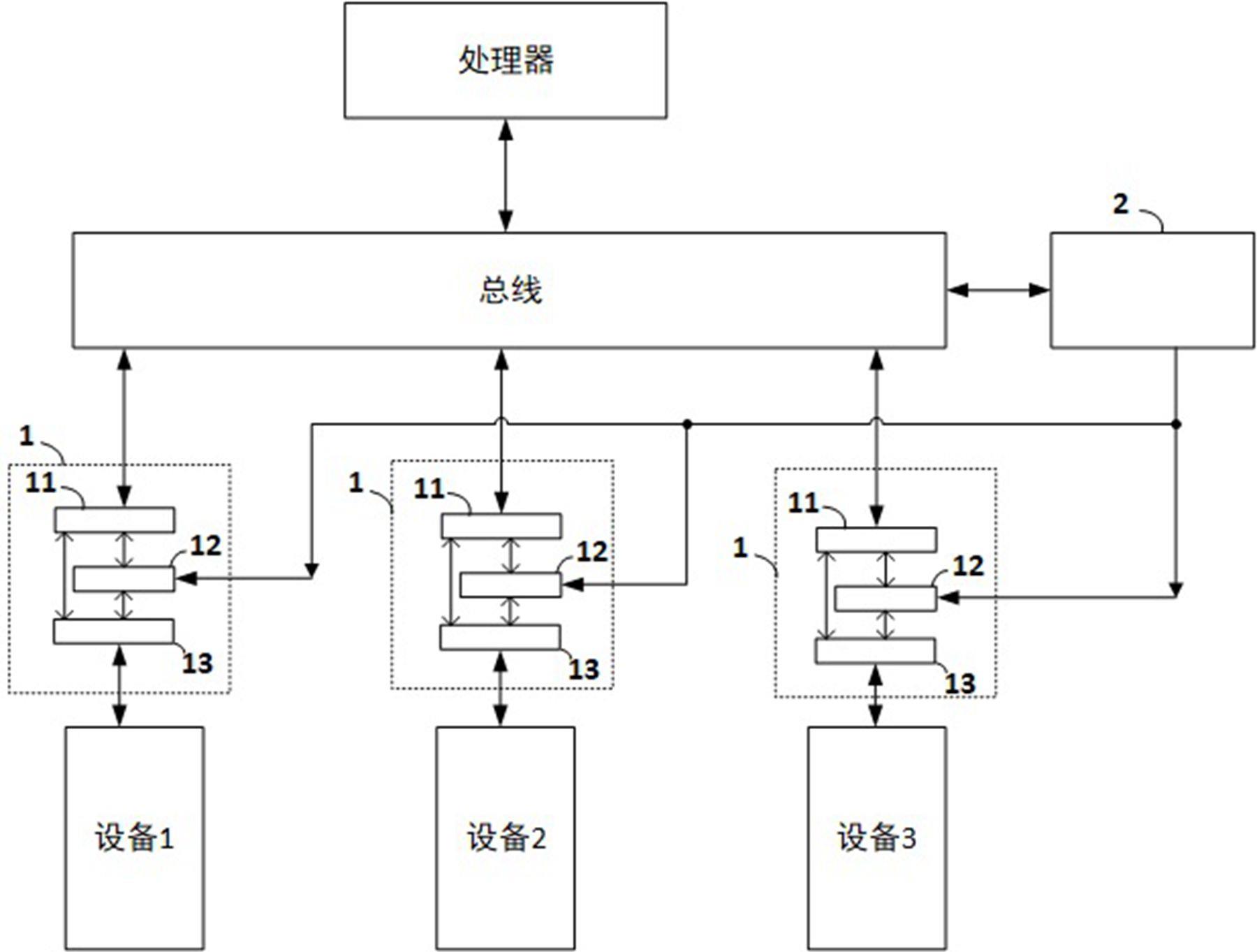

2、为实现上述目的,本发明提供一种硬件加速电路,用于对芯片内部挂载在总线上的设备进行配置调度,所述硬件加速电路包括:前级接口模块、主控模块及后级接口模块,其中:

3、所述前级接口模块与总线连接,用于对输入的访问设备的读操作指令与加速设备的写操作指令进行自定义编译与配置;

4、所述主控模块与所述前级接口模块连接,基于芯片所提供的时间基准在生效的时刻之前,对写操作指令执行对应操作,并将与写操作指令对应的编译与配置信息传输至下级模块,其中,时间基准由芯片内部的时间模块提供;

5、所述后级接口模块与所述前级接口模块及所述主控模块连接,基于传输读操作指令用于设备访问,并基于接收到的编译与配置信息对设备进行调度;

6、其中,执行调度的设备在对应的所述硬件加速电路作用下,彼此之间互相解耦。

7、可选地,所述时间模块包括计数器,其中,所述计数器在芯片复位生效后以恒定频率进行循环计数。

8、可选地,所述前级接口模块包括:地址译码单元、加速操作寄存器、头部内存单元及数据内存单元,其中:

9、所述地址译码单元与总线连接,对输入的指令按照地址进行转换分发;

10、所述加速操作寄存器与所述地址译码单元连接,通过配置映射至对应的设备寄存器;

11、所述头部内存单元与所述地址译码单元连接,用于映射指令的头部信息;

12、所述数据内存单元与所述地址译码单元连接,用于映射指令的数据信息。

13、可选地,所述头部内存单元与所述数据内存单元在同一所述硬件加速电路中深度一致。

14、可选地,所述主控模块包括:排序单元、状态机控制单元、预处理与执行单元及释放单元,其中:所述排序单元、所述预处理与执行单元及所述释放单元均与所述状态机控制单元连接,所述状态机控制单元基于写操作指令控制所述排序单元、所述预处理与执行单元及所述释放单元以执行对应操作,其中,在芯片复位后,所述状态机控制单元执行空闲状态;在设备寄存器被映射后,所述状态机控制单元基于生效的时刻通过所述排序单元对指令进行排序;在设备产生启动信号后,所述状态机控制单元通过所述预处理与执行单元,在生效的时刻之前将写操作指令的头部信息与数据信息传输至所述后级接口模块;在所述预处理与执行单元将一条指令传输至所述后级接口模块的同时,所述预处理与执行单元输出完成信号,使所述状态机控制单元通过所述释放单元进入释放状态,所述状态机控制单元继续执行下一条指令,当执行到最后一条指令,所述状态机控制单元通过释放单元返回空闲状态。

15、可选地,进行排序的过程包括:触发排序后,先清空排序结果,然后对所有有效的指令按照头部信息的生效时刻进行排序;所述预处理与执行单元基于排序的结果在生效的时刻之前将写操作指令的头部信息与数据信息传输至所述后级接口模块。

16、可选地,将指令的生效时刻与时间基准进行对比;在生效时刻之前提前k个时钟周期,将该指令中写操作的头部信息与数据信息传输至所述后级接口模块,其中,k个时钟周期等于所述后级接口模块的工作耗时,k的数量由总线与设备之间的通信协议确定。

17、可选地,所述后级接口模块包括读写操作转换单元及输出控制单元,其中,所述读写操作转换单元与所述前级接口模块及所述主控模块连接,其中,所述读写操作转换单元用于使总线与设备的通信协议保持一致;所述输出控制单元与所述读写操作转换单元连接。

18、为实现上述目的,本发明提供一种芯片,所述芯片包括至少一个所述硬件加速电路,用于对芯片内部挂载在总线上的设备进行配置调度,其中,所述硬件加速电路与设备一一对应。

19、如上所述,本发明的一种硬件加速电路及芯片,具有以下有益效果:

20、本发明的硬件加速电路及芯片,通过所述前级接口模块的自定义编译与配置操作对设备寄存器提前缓存,通过主控模块执行对应操作节约芯片的计算资源,使设备能够在精准的生效时刻进行配置调度,且设备之间互相解耦,具有广泛的应用场景。

技术特征:

1.一种硬件加速电路,用于对芯片内部挂载在总线上的设备进行配置调度,其特征在于,所述硬件加速电路包括:前级接口模块、主控模块及后级接口模块,其中:

2.根据权利要求1所述的硬件加速电路,其特征在于:所述时间模块包括计数器,其中,所述计数器在芯片复位生效后以恒定频率进行循环计数。

3.根据权利要求1所述的硬件加速电路,其特征在于:所述前级接口模块包括:地址译码单元、加速操作寄存器、头部内存单元及数据内存单元,其中:

4.根据权利要求3所述的硬件加速电路,其特征在于:所述头部内存单元与所述数据内存单元在同一所述硬件加速电路中深度一致。

5.根据权利要求4所述的硬件加速电路,其特征在于:所述主控模块包括:排序单元、状态机控制单元、预处理与执行单元及释放单元,其中:所述排序单元、所述预处理与执行单元及所述释放单元均与所述状态机控制单元连接,所述状态机控制单元基于写操作指令控制所述排序单元、所述预处理与执行单元及所述释放单元以执行对应操作,其中,在芯片复位后,所述状态机控制单元执行空闲状态;在设备寄存器被映射后,所述状态机控制单元基于生效的时刻通过所述排序单元对指令进行排序;在设备产生启动信号后,所述状态机控制单元通过所述预处理与执行单元,在生效的时刻之前将写操作指令的头部信息与数据信息传输至所述后级接口模块;在所述预处理与执行单元将一条指令传输至所述后级接口模块的同时,所述预处理与执行单元输出完成信号,使所述状态机控制单元通过所述释放单元进入释放状态,所述状态机控制单元继续执行下一条指令,当执行到最后一条指令,所述状态机控制单元通过释放单元返回空闲状态。

6.根据权利要求5所述的硬件加速电路,其特征在于:进行排序的过程包括:触发排序后,先清空排序结果,然后对所有有效的指令按照头部信息的生效时刻进行排序;所述预处理与执行单元基于排序的结果在生效的时刻之前将写操作指令的头部信息与数据信息传输至所述后级接口模块。

7.根据权利要求5所述的硬件加速电路,其特征在于:所述预处理与执行单元进行的操作包括:将指令的生效时刻与时间基准进行对比;在生效时刻之前提前k个时钟周期,将该指令中写操作的头部信息与数据信息传输至所述后级接口模块,其中,k个时钟周期等于所述后级接口模块的工作耗时,k的数量由总线与设备之间的通信协议确定。

8.根据权利要求1所述的硬件加速电路,其特征在于:所述后级接口模块包括读写操作转换单元及输出控制单元,其中,所述读写操作转换单元与所述前级接口模块及所述主控模块连接,其中,所述读写操作转换单元用于使总线与设备的通信协议保持一致;所述输出控制单元与所述读写操作转换单元连接。

9.一种芯片,其特征在于:所述芯片包括至少一个如权利要求1-8任意一项所述的硬件加速电路,用于对芯片内部挂载在总线上的设备进行配置调度,其中,所述硬件加速电路与设备一一对应。

技术总结

本发明提供一种硬件加速电路及芯片,用于对芯片内部挂载在总线上的设备进行一对一加速操作,前级接口模块与总线连接,用于对输入的访问设备的读操作指令与加速设备的写操作指令进行自定义编译与配置;主控模块基于芯片所提供的时间基准在生效的时刻之前,对写操作指令执行对应操作,并将与写操作指令对应的编译与配置信息传输至下级模块;后级接口模块基于传输读操作指令用于设备访问,并基于接收到的编译与配置信息对设备进行调度;通过所述前级接口模块的自定义编译与配置操作对设备寄存器提前缓存,通过主控模块执行对应操作节约芯片的计算资源,使设备能够在精准的生效时刻进行调度,且设备之间互相解耦,具有广泛的应用场景。

技术研发人员:邓炯麟,梅平,王吉,尹棋烽

受保护的技术使用者:无锡麟聚半导体科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!