芯片设计的设计规则检查方法及相关设备与流程

本申请涉及芯片,尤其涉及一种芯片设计的设计规则检查方法及相关设备。

背景技术:

1、电子设计自动化(electronic design automation,简称eda),是指利用计算机辅助设计(cad)软件,来完成超大规模集成电路(vlsi)芯片的功能设计、综合、验证、物理设计(包括布局、布线、版图、设计规则检查等)等流程的设计方式。

2、在数字芯片设计流程中,设计规则检查(design rule check,drc)是重要的一环,设计规则检查是在设计过程中对版图是否符合限制条件进行的检查的过程。在检查过程中每个设计都可能对应多条规则,需要确定该设计满足所有对应规则的要求,在相关技术中,每个设计都要进行多次反复的测量及检测。

3、因此,如何在这个检查的过程中节省检查时间,提高整体效率,是一个亟待解决的问题。

技术实现思路

1、有鉴于此,本申请提出一种芯片设计的设计规则检查方法及相关设备,以解决或部分解决上述问题。

2、本申请第一方面,提供了一种芯片设计的设计规则检查方法,包括:

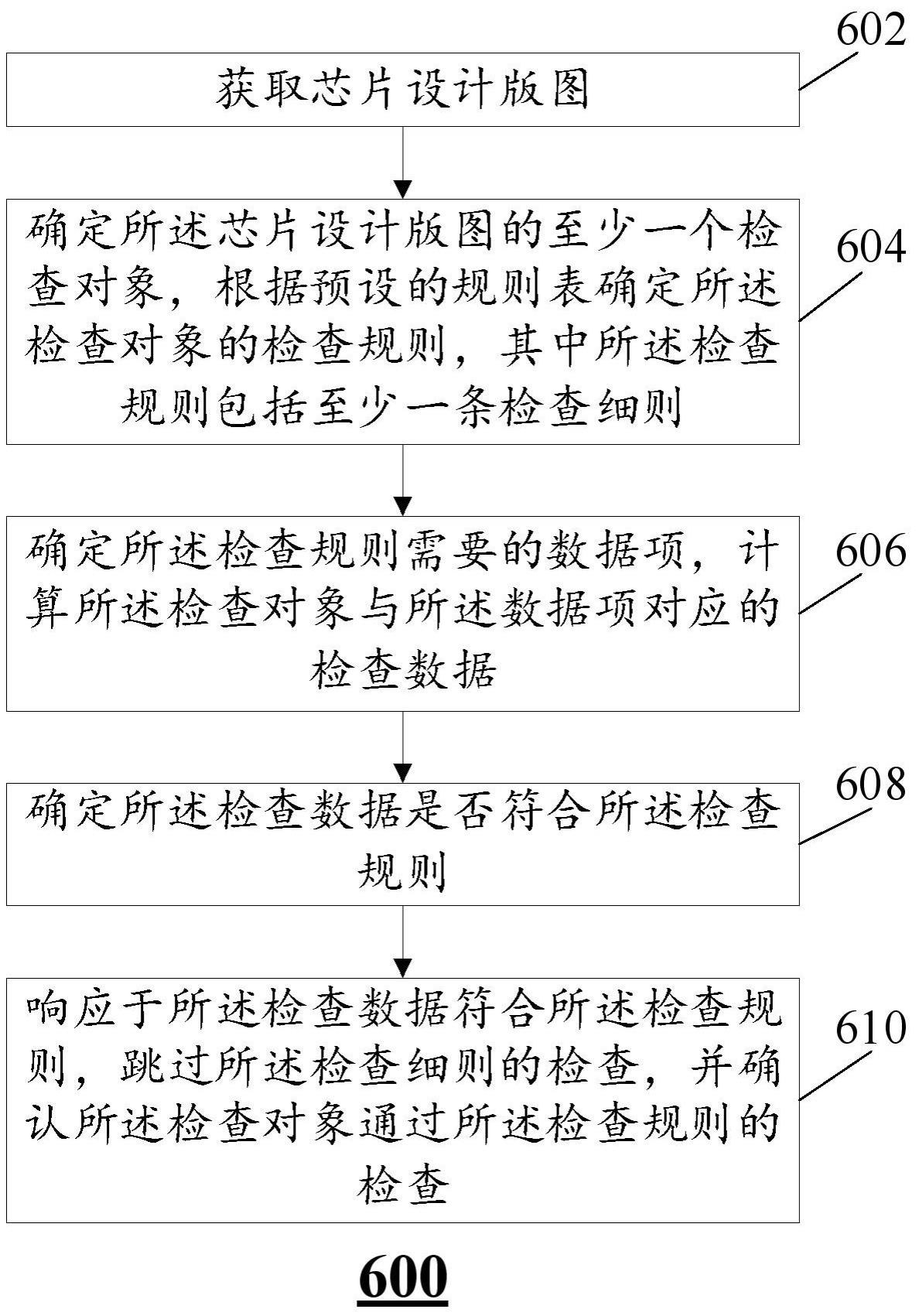

3、获取芯片设计版图;

4、确定所述芯片设计版图的至少一个检查对象,根据预设的规则表确定所述检查对象的检查规则,其中所述检查规则包括至少一条检查细则;

5、确定所述检查规则需要的数据项,计算所述检查对象与所述数据项对应的检查数据;

6、确定所述检查数据是否符合所述检查规则;

7、响应于所述检查数据符合所述检查规则,跳过所述检查细则的检查,并确认所述检查对象通过所述检查规则的检查。

8、本申请第二方面,提供了一种计算机设备,包括一个或者多个处理器、存储器;和一个或多个程序,其中所述一个或多个程序被存储在所述存储器中,并且被所述一个或多个处理器执行,所述程序包括用于执行根据第一方面所述的方法的指令。

9、本申请第三方面,提供了一种包含计算机程序的非易失性计算机可读存储介质,当所述计算机程序被一个或多个处理器执行时,使得所述处理器执行第一方面所述的方法。

10、本申请提供的一种芯片设计的设计规则检查方法及相关设备,通过设定芯片设计版图中每个要检查的检查对象的检查规则所要检查的数据项,在检查对象满足这些数据项的要求时,直接认定该检查对象符合相应的检查规则,从而跳过较为繁琐的检查细则的检查,减少了重复搜索、检查等过程,提高了芯片设计的整体效率。

技术特征:

1.一种芯片设计的设计规则检查方法,包括:

2.如权利要求1所述的方法,其中,确定所述检查数据是否符合所述检查规则,还包括:

3.如权利要求2所述的方法,其中,逐条判断所述检查数据是否符合所述检查对象对应的所有所述检查细则,还包括:

4.如权利要求3所述的方法,其中,确认所述检查对象没有通过所述检查规则的检查之后,所述方法还包括:

5.如权利要求3所述的方法,其中,确认所述检查对象没有通过所述检查规则的检查之后,所述方法还包括:

6.如权利要求1所述的方法,其中,确定所述检查规则需要的数据项,包括:

7.如权利要求1所述的方法,其中,确定所述检查数据是否符合所述检查规则,包括:

8.如权利要求7所述的方法,其中,基于全部所述合规区间生成所述检查规则对应的检测标准,包括:

9.如权利要求1所述的方法,其中,计算所述检查对象与所述数据项对应的检查数据之后,所述方法还包括:

10.如权利要求1所述的方法,其中,所述检查对象至少包括:所述芯片设计版图中的通道过孔;所述检查规则至少包括:所述通道过孔两端的层级金属的覆盖,所述通道过孔与其他通道过孔之间的距离,以及所述芯片设计版图中与所述通道过孔不相交的走线与所述通道过孔之间的距离。

11.一种计算机设备,包括一个或者多个处理器、存储器;和一个或多个程序,其中所述一个或多个程序被存储在所述存储器中,并且被所述一个或多个处理器执行,所述程序包括用于执行根据权利要求1至10任意一项所述的方法的指令。

12.一种包含计算机程序的非易失性计算机可读存储介质,当所述计算机程序被一个或多个处理器执行时,使得所述处理器执行权利要求1至10中任一项所述的方法。

技术总结

本申请提供一种芯片设计的设计规则检查方法及相关设备。该方法,包括:获取芯片设计版图;确定所述芯片设计版图的至少一个检查对象,根据预设的规则表确定所述检查对象的检查规则,其中所述检查规则包括至少一条检查细则;确定所述检查规则需要的数据项,计算所述检查对象与所述数据项对应的检查数据;确定所述检查数据是否符合所述检查规则;响应于所述检查数据符合所述检查规则,跳过所述检查细则的检查,并确认所述检查对象通过所述检查规则的检查。

技术研发人员:罗二海,周亮,郭晓华,谭胜昔,潘家兴

受保护的技术使用者:芯行纪科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!