一种走线阻抗检测方法、系统、电子设备及可读存储介质与流程

本申请涉及pcb设计领域,特别涉及一种走线阻抗检测方法、系统、电子设备及可读存储介质。

背景技术:

1、随着高速电路的普及,电路板设计密度越来越大,对于通讯行业、服务器、以及工控、军工领域对高速电路需求较多性能要求较高的地方,pcb(printed circuit board,印制电路板)的布线阻抗成了一个关注的重点。可以理解,在整个信号系统的传输链路里面,pcb板级的设计中会有较多的情况造成阻抗不连续或者突变,比如布线线宽的改变、过孔、锐角走线、厚度的不一致、参考平面的改变以及不完整跨分割区域等,这些阻抗不连续或者改变会对传输的信号质量造成较大的影响。

2、目前,在pcb布线处理完成后使用si9000等阻抗设计软件自带的阻抗分析工具对pcb走线阻抗进行分析,但是现有的阻抗分析工具的功能并不完善,只能计算分析如下几个因素:布线线宽、锐角走线、走线厚度、参考平面,无法精确分析链路中铜片和过孔对阻抗的影响,因此,无法完全规避设计缺陷,可能在对pcb板功能测试时才能发现相应的设计问题,影响项目进度,造成成本资源浪费。

3、因此,如何提供一种解决上述技术问题的方案是本领域技术人员目前需要解决的问题。

技术实现思路

1、本申请的目的是提供一种走线阻抗检测方法、系统、电子设备及可读存储介质,考虑了铜片和过孔线对走线阻抗的影响,能够提升阻抗分析精度,避免了高速链路中间的异常设计导致的阻抗异常,从而避免走线阻抗突变、反射等影响信号质量,规避印刷电路板设计缺陷。

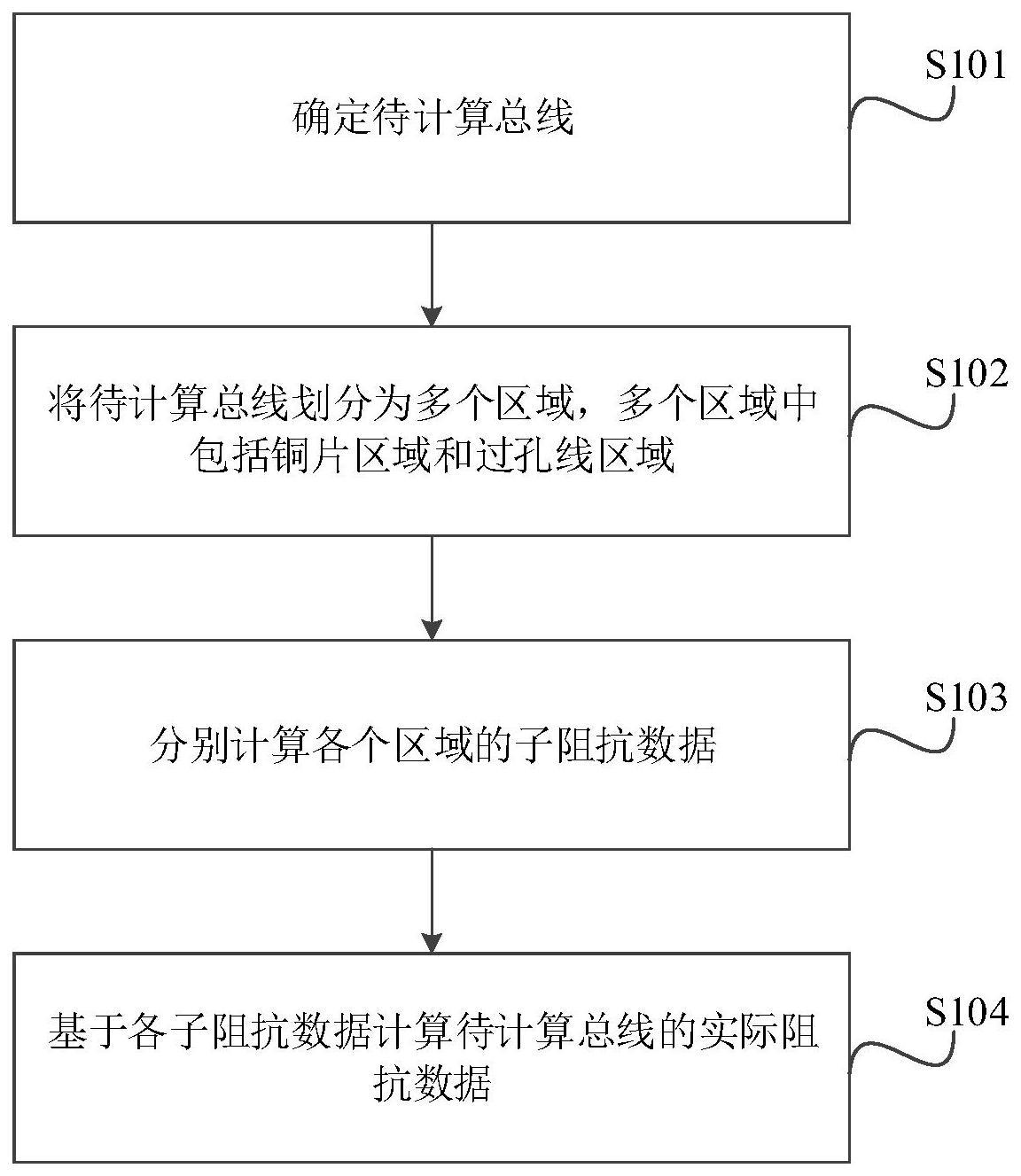

2、为解决上述技术问题,本申请提供了一种走线阻抗检测方法,包括:

3、确定待计算总线;

4、将所述待计算总线划分为多个区域,多个所述区域中包括铜片区域和过孔线区域;

5、分别计算各个所述区域的子阻抗数据;

6、基于各所述子阻抗数据计算所述待计算总线的实际阻抗数据。

7、可选的,将所述待计算总线划分为多个区域的过程包括:

8、将所述待计算总线划分为多个区域,多个所述区域包括扇出线段区域、主干线区域、引入线区域、所述铜片区域和所述过孔线区域。

9、可选的,所述分别计算各个所述区域的子阻抗数据之后,该总线阻抗检测方法还包括:

10、将各所述子阻抗数据进行一致性分析,基于一致性分析结果得到阻抗检测结果。

11、可选的,将各所述子阻抗数据进行一致性分析的过程包括:

12、分别计算每一所述子阻抗数据与目标阻抗数据的差值;

13、判断所有所述差值是否处于预设范围内;

14、若是,得到第一分析结果;

15、若否,得到第二分析结果;

16、其中,所述一致性分析结果为所述第一分析结果或所述第二分析结果。

17、可选的,所述分别计算各个所述区域的子阻抗数据之后,所述总线阻抗检测方法还包括:

18、基于各个所述子阻抗数据生成阻抗列表和阻抗分布图;

19、提示与所述阻抗列表和所述阻抗分布图对应的信息。

20、可选的,所述分别计算各个所述区域的子阻抗数据的过程包括:

21、根据阻抗计算参数分别计算各个所述区域的子阻抗数据;

22、其中,所述阻抗计算参数包括介质的厚度、走线的宽度、走线的厚度、参考平面参数、叠层选取的材质的介电常数。

23、可选的,根据阻抗计算参数分别计算各个所述区域的子阻抗数据的过程包括:

24、预先根据所述阻抗计算参数构建计算关系式;

25、通过所述计算关系式分别计算各个所述区域的子阻抗数据;

26、所述计算关系式为:

27、z0=87/sqrt(εr+1.41)×ln[(5.98h)/(0.8w+t)];

28、其中,z0为所述走线的阻抗,εr为叠层选取的材质的介电常数,h为所述走线与基准面之间的介质厚度,w为所述走线的宽度,t为所述走线的厚度。

29、为解决上述技术问题,本申请还提供了一种走线阻抗检测系统,包括:

30、确定模块,用于确定待计算总线;

31、划分模块,用于将所述待计算总线划分为多个区域,多个所述区域中包括铜片区域和过孔线区域;

32、第一计算模块,用于分别计算各个所述区域的子阻抗数据;

33、第二计算模块,用于基于各所述子阻抗数据计算所述待计算总线的实际阻抗数据。

34、为解决上述技术问题,本申请还提供了一种电子设备,包括:

35、存储器,用于存储计算机程序;

36、处理器,用于执行所述计算机程序时实现如上文任意一项所述的走线阻抗检测方法的步骤。

37、为解决上述技术问题,本申请还提供了一种计算机可读存储介质,所述计算机可读存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现如上文任意一项所述的走线阻抗检测方法的步骤。

38、本申请提供的一种走线阻抗检测方法的有益效果如下:

39、将待计算总线划分成独立的区域,区域中包括铜片区域和过孔线区域,分别计算各个区域对应的子阻抗数据,然后根据所有子阻抗数据计算待计算总线的实际阻抗数据,本申请考虑了铜片和过孔线对走线阻抗的影响,提升阻抗分析精度,同时本申请先将待计算总线分拆离散后进行分析,再整合检查分析,避免了高速链路中间的异常设计导致的阻抗异常,从而避免走线阻抗突变、反射等影响信号质量,规避印刷电路板设计缺陷。

40、本申请还提供了一种走线阻抗检测系统、电子设备及计算机可读存储介质,具有和上述走线阻抗检测方法相同的有益效果。

技术特征:

1.一种走线阻抗检测方法,其特征在于,包括:

2.根据权利要求1所述的总线阻抗检测方法,其特征在于,将所述待计算总线划分为多个区域的过程包括:

3.根据权利要求1所述的总线阻抗检测方法,其特征在于,所述分别计算各个所述区域的子阻抗数据之后,该总线阻抗检测方法还包括:

4.根据权利要求3所述的总线阻抗检测方法,其特征在于,将各所述子阻抗数据进行一致性分析的过程包括:

5.根据权利要求1所述的总线阻抗检测方法,其特征在于,所述分别计算各个所述区域的子阻抗数据之后,所述总线阻抗检测方法还包括:

6.根据权利要求1-5任意一项所述的总线阻抗检测方法,其特征在于,所述分别计算各个所述区域的子阻抗数据的过程包括:

7.根据权利要求6所述的总线阻抗检测方法,其特征在于,根据阻抗计算参数分别计算各个所述区域的子阻抗数据的过程包括:

8.一种走线阻抗检测系统,其特征在于,包括:

9.一种电子设备,其特征在于,包括:

10.一种计算机可读存储介质,其特征在于,所述计算机可读存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现如权利要求1-7任意一项所述的走线阻抗检测方法的步骤。

技术总结

本申请公开了一种走线阻抗检测方法、系统、电子设备及可读存储介质,涉及PCB设计领域,该走线阻抗检测方法包括:确定待计算总线将待计算总线划分为多个区域,多个区域中包括铜片区域和过孔线区域;分别计算各个区域的子阻抗数据;基于各子阻抗数据计算待计算总线的实际阻抗数据。本申请考虑了铜片和过孔线对走线阻抗的影响,能够提升阻抗分析精度,同时先将待计算总线分拆离散后进行分析,再整合检查分析,避免了高速链路中间的异常设计导致的阻抗异常,从而避免走线阻抗突变、反射等影响信号质量,规避印刷电路板设计缺陷。

技术研发人员:林少玲,荣世立

受保护的技术使用者:浪潮(山东)计算机科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!