一种大面阵芯片及其制作方法与流程

本发明涉及集成电路设计,尤其涉及一种大面阵芯片及其制作方法。

背景技术:

1、目前,大面阵芯片一般用作制作图像传感器芯片,大面阵芯片的数据输出需要很大的带宽,一般采用多路并行i/o传输,芯片与后续信号处理系统对接时,需要保证不同通道之间信号对齐,实现信号对齐的方式有:在信号处理端加入通道歪斜校准功能,这种信号对齐模式的前提是需要和阵列芯片之间约定好校准机制,同时阵列芯片需要在有效信号数据输出前插入一段训练信号,训练信号用于辅助信号处理系统的通道歪斜校准。由此可见,该方法会导致有效信号带宽的损失。另外,受限于硅片制造单次光刻的面积限制,对于尺寸很大的阵列芯片,传统方式需要进行多次光刻实现芯片图形的制作,但多次光刻意味着需要多套掩膜版,成本较高。

2、为此,本发明提供一种新的大面阵芯片的时钟同步设计方案以改善上述问题。

技术实现思路

1、本发明实施例提供一种大面阵芯片及其制作方法,用以降低接收端的信号同步复杂程度和芯片面积成本。

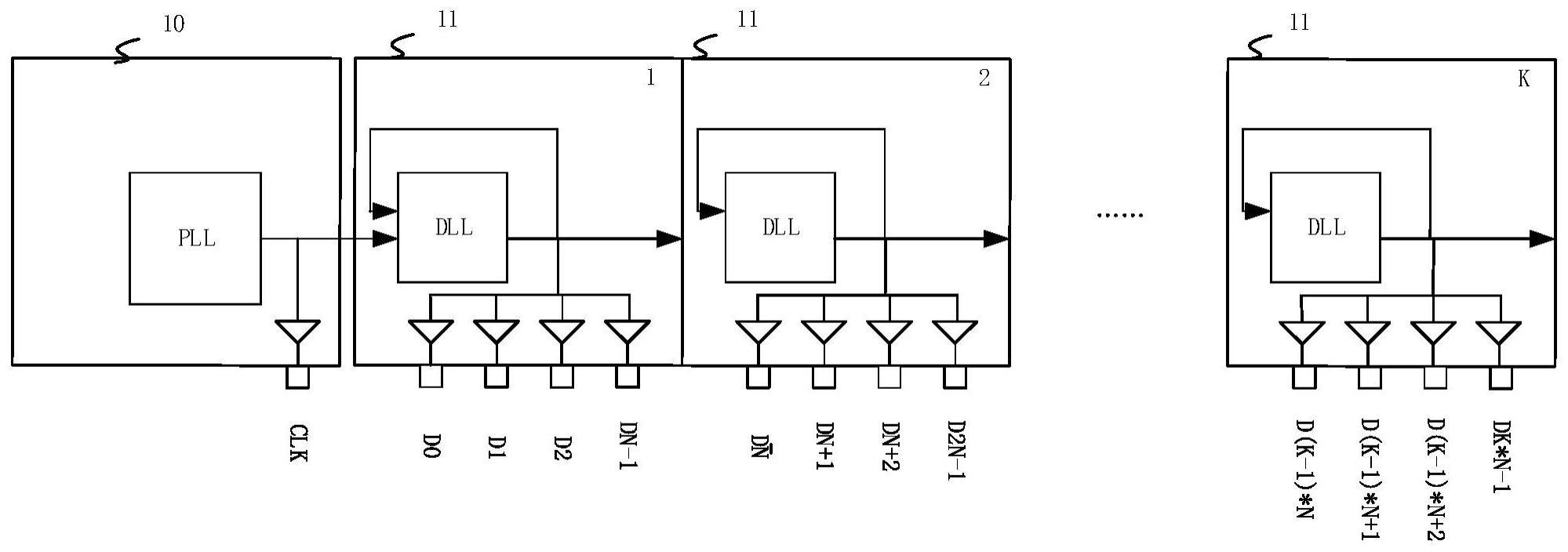

2、本发明提供一种大面阵芯片及其制作方法,所述大面阵芯片由规则拼接单元和不规则拼接单元拼接形成。其中,不规则拼接单元包括普通锁相环,所述普通锁相环用于向所连接的规则拼接单元提供时钟信号;规则拼接单元包括延迟锁相环,所述延迟锁相环用于使得规则拼接单元内的输入端口至输出端口的时钟同步,其中规则拼接单元在流片过程中使用同一套掩膜版进行曝光,不规则拼接单元在流片过程中使用不同掩膜版进行曝光。

3、本发明提供的大面阵芯片的有益效果在于:在规则拼接单元内设置一个延迟锁相环,使规则拼接单元内输入端口到输出端口的时钟同步,实现了多个规则拼接单元拼接时,所有重复规则拼接单元内的时钟同步,进而实现了大面阵芯片的阵列数据同步。基于这样的同步,大面阵芯片与后置信号处理芯片互联时,可只发送一路同步时钟,就能在信号处理芯片内同步采样所有阵列数据通道,而不需要对每个数据通道分别做相位校准,从系统模块上来说,降低了接收端的信号同步复杂程度和芯片面积成本,从信号处理时间上来说,也降低了系统的数据处理延时,提高了io的有效信号发送效率,另外,规则拼接单元内的掩膜版是一致的,从而在流片过程中,用同一套掩膜版在硅片上进行多次曝光就能实现规则拼接单元的拼接扩展,节省成本。

4、在一种可能的实现方案中,所述延迟锁相环包括相位比较器、低通滤波器、控制延迟单元和延迟匹配单元;所述相位比较器包括第一输入端和第二输入端,所述第一输入端的输入信号为时钟信号,所述第二输入端的输入信号为所述延迟匹配单元的输出信号,所述相位比较器用于比较时钟信号和所述延迟匹配单元的输出信号之间的相位差,根据比较结果生成输出信号;所述低通滤波器,用于对所述相位比较器的输出信号进行滤波。

5、所述控制延迟单元用于调整输入到输出的延迟时间;所述控制延迟单元的输出端通过延迟匹配单元连接到所述相位比较器,形成所述相位比较器的负反馈通路,所述负反馈通路用于实现所述相位比较器的第一输入端和第二输入端的相位同步。

6、在一种可能的实现方案中,所述规则拼接单元包括与阵列数量匹配的读出电路、信号处理电路和输出驱动电路。

7、在一种可能的实现方案中,所述规则拼接单元还包括时钟树,所述时钟树用于利用二叉树方式同步到达规则拼接单元内的并行数据,实现所有数据io的同步。

8、在一种可能的实现方案中,所述时钟信号到达相位比较器输入端的延迟时间为t1,从延迟锁相环的时钟输出端口到达相位比较器的第二输入端的延迟时间为t2,从延迟锁相环的输出端到达规则拼接单元的输出端的延迟时间为t3,其中,t1+t3=t2。

9、在一种可能的实现方案中,所述控制延迟单元为电压控制延迟单元,所述电压控制延迟单元包括多级电压控制缓冲器,用于当电压升高时,调整输入到输出的延迟时间变长,当电压降低时,调整输入到输出的延迟时间变短。

10、在一种可能的实现方案中,所述控制延迟单元为数字控制延迟单元,所述数字控制延迟单元通过数字控制逻辑选择调整从输入到输出经过的缓冲器级数,从而调整输入到输出的延迟时间。

11、在一种可能的实现方案中,所述不规则拼接单元内包括偏置产生电路、时钟产生电路和电源管理电路,且电路模块的数量与阵列大小无关。

12、在一种可能的实现方案中,所述低通滤波器是由电阻和电容构成。

13、第二方面,本发明还提供一种大面阵芯片及其制作方法,包括:在流片过程中使用同一套掩膜版进行曝光制作规则拼接单元,在流片过程中使用不同掩膜版进行曝光制作不规则拼接单元;其中,不规则拼接单元包括普通锁相环,所述普通锁相环用于向所连接的规则拼接单元提供时钟信号;规则拼接单元包括延迟锁相环,所述延迟锁相环用于使得规则拼接单元内的输入端口至输出端口的时钟同步。有益效果可以参见上述实施例。

技术特征:

1.一种大面阵芯片及其制作方法,其特征在于,由规则拼接单元和不规则拼接单元拼接形成;其中,不规则拼接单元包括普通锁相环,所述普通锁相环用于向所连接的规则拼接单元提供时钟信号;规则拼接单元包括延迟锁相环,所述延迟锁相环用于使得规则拼接单元内的输入端口至输出端口的时钟同步。

2.根据权利要求1所述的大面阵芯片,其特征在于,所述延迟锁相环包括相位比较器、低通滤波器、控制延迟单元和延迟匹配单元;

3.根据权利要求1所述的大面阵芯片,其特征在于,所述规则拼接单元包括与阵列数量匹配的读出电路、信号处理电路和输出驱动电路。

4.根据权利要求1至3任一项所述的大面阵芯片,其特征在于,所述规则拼接单元还包括时钟树,所述时钟树用于利用二叉树方式同步到达规则拼接单元内的并行数据。

5.根据权利要求2所述的大面阵芯片,其特征在于,所述时钟信号到达相位比较器输入端的延迟时间为t1,从延迟锁相环的时钟输出端口到达相位比较器的第二输入端的延迟时间为t2,从延迟锁相环的输出端到达规则拼接单元的输出端的延迟时间为t3,其中,t1+t3=t2。

6.根据权利要求2所述的大面阵芯片,其特征在于,所述控制延迟单元为电压控制延迟单元,所述电压控制延迟单元包括多级电压控制缓冲器,用于当电压升高时,调整输入到输出的延迟时间变长,当电压降低时,调整输入到输出的延迟时间变短。

7.根据权利要求2所述的大面阵芯片,其特征在于,所述控制延迟单元为数字控制延迟单元,所述数字控制延迟单元通过数字控制逻辑选择调整从输入到输出经过的缓冲器级数,从而调整输入到输出的延迟时间。

8.根据权利要求1所述的大面阵芯片,其特征在于,所述不规则拼接单元内包括偏置产生电路、时钟产生电路和电源管理电路,且电路模块的数量与阵列大小无关。

9.根据权利要求2所述的大面阵芯片,其特征在于,所述低通滤波器是由电阻和电容级联构成。

10.一种大面阵芯片及其制作方法,其特征在于,包括:

技术总结

本发明公开了一种大面阵芯片及其制作方法,所述大面阵芯片由规则拼接单元和不规则拼接单元拼接形成。其中,不规则拼接单元包括普通锁相环,所述普通锁相环用于向所连接的规则拼接单元提供时钟信号;规则拼接单元包括延迟锁相环,所述延迟锁相环用于使得规则拼接单元内的输入端口至输出端口的时钟同步。该大面阵芯片用以降低接收端的信号同步复杂程度和芯片面积成本。

技术研发人员:杨海玲,韩素贞

受保护的技术使用者:上海微阱电子科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!