一种基于近似4-2压缩器的单比特全数字存内计算单元的制作方法

本发明属于,具体涉及一种基于近似4-2压缩器的单比特全数字存内计算单元。

背景技术:

1、在人工智能发展迅猛的今天,传统的冯诺依曼架构针对数据密集型的神经网络本身存在“存储墙”和“功耗墙”的问题,而存内计算架构通过将存储单元和计算电路结合,从根本上解决了冯诺依曼瓶颈。

2、而主流的模拟密集型电路的抗干扰能力又较弱,相比较之下数字型的全数字存内计算架构的鲁棒性便展出了优势。但是数字存内计算结构中又因为额外乘法和加法树电路的叠加导致功耗和面积损耗,难以应用。

技术实现思路

1、本发明的目的在于克服现有技术中的不足,提供一种基于近似4-2压缩器的单比特全数字存内计算单元,具有更高的稳定性和准确度,受外界干扰较小。

2、为达到上述目的,本发明是采用下述技术方案实现的:

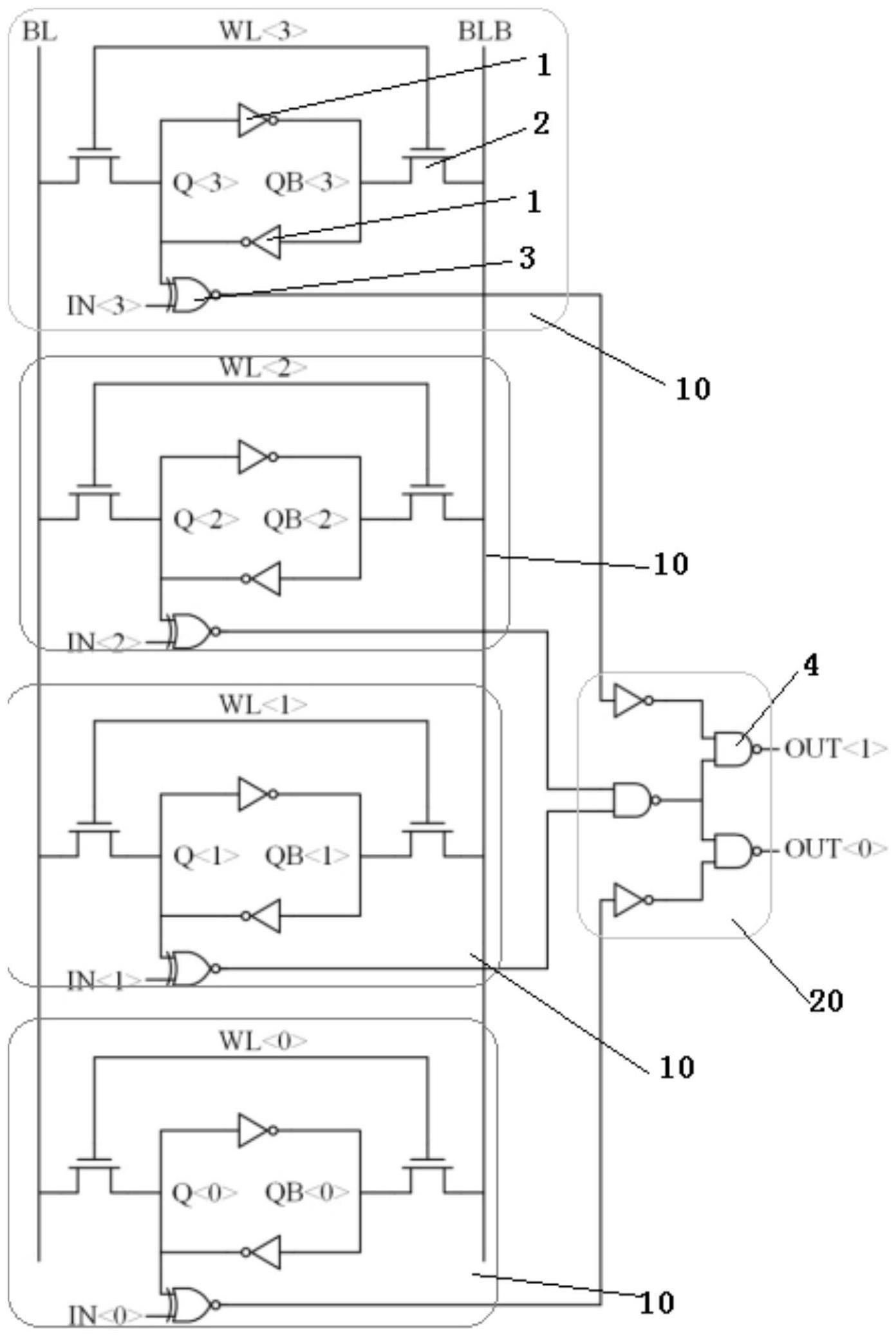

3、第一方面,本发明提供一种基于近似4-2压缩器的单比特全数字存内计算单元,包括至少一个近似4-2压缩器和与所述近似4-2压缩器连接的一组存储单元;

4、一组存储单位包括四个存储单元;

5、每个所述存储单元存储1bit权重信息,并均通过一个同或门连接所述近似4-2压缩器;

6、所述近似4-2压缩器包括第一级电路和第二级电路;

7、所述第一级电路包括两个反向器和一个与非门,所述第二级电路包括两个与非门;第一级电路的两个反向器和一个与非门分别与所述第二级电路的两个与非门连接;

8、四个存储单元中,两个存储单元分别通过同或门连接所述第一级电路的两个反相器,两个存储单元分别通过同或门连接所述第一级电路的同一个与非门;

9、所述第一级电路的两个反相器用于将两个存储单元输入的乘累加结果反向输出到第二级电路的与非门中;

10、所述第一级电路的与非门用于将另外两个存储单元输入的按位乘法结果输出到第二级电路的与非门中;

11、第二级电路的与非门用于输出作为近似结果。

12、进一步的,所述存储单元包括数据锁存结构以及两个导通的n管;

13、进一步的,所述数据锁存结构包括首尾相接的两个反相器;

14、进一步的,所述存储单元的两个n管的栅极由同一字线wl控制,两个n管的源漏接位线bl、blb和反相器;

15、进一步的,同一列的存储单元使用同一位线进行连接。

16、进一步的,每个存储单元的q端均与其按位乘法结构中的同或门输入端进行连接,同或门输入的另一端连接输入激励in,输出作为按位乘法结果进入到近似4-2压缩器中。

17、进一步的,所述近似4-2压缩器为多个,每个近似4-2压缩器连接一组存储单元。

18、第二方面,本发明提供一种基于近似4-2压缩器的单比特全数字存内计算方法,基于第一方面所述的单比特全数字存内计算单元,包括:

19、将一组中四个存储单元的单比特的按位乘法结果输入近似4-2压缩器中,进行乘累加,将单比特的乘累加结果进行乘累加,将4个1bit的数据进行乘累加,得到乘累加结果。

20、进一步的,所述存储单元包括数据锁存结构以及两个导通的n管;

21、所述方法还包括:

22、在存储模式中,该存内计算单元进行正常的sram写入操作,当字线信号高电平到来后,开启两个n型晶体管,将位线上预加载的权重数据写入到存储单元中,写入后的权重数据以1bit的形式存储在sram中。

23、与现有技术相比,本发明所达到的有益效果:

24、1、和模拟密集型的存内计算单元以充放电完成乘累加相比,本申请的数字域的门电路具有更高的稳定性和准确度,受外界干扰较小;

25、2、与传统的数字存内计算结构中加法器阵列的高功耗相比,该结构通过引入一种新型的近似4-2压缩器,传统的做法是使用全加器和半加器进行相加,而这种做法会产生较大的功耗浪费。这里采用近似4-2压缩器进行相加,在产生可接受的误差情况下降低了功耗,降低了加法器阵列部分的功耗消耗,从而可以降低整体数字存内计算结构的功耗浪费;

26、3、本结构支持神经网络中的二值化的输入激励和权重进行乘累加,其中二值化网络中存在“+1”和“-1”两个值,在电路中采用电压vdd代表“+1”,电压vss代表“-1”,vdd为电源电压,vss为接地的零电压。对于最终的乘累加结果,可以看做是将其中“+1”的数量进行相加,即按照数字电路的高低电平进行相加,得到乘累加结果。每列的4个sram单元作为一个单元共用一个近似4-2压缩器,得到最终的2bit近似乘累加结果。

技术特征:

1.一种基于近似4-2压缩器的单比特全数字存内计算单元,其特征在于,包括至少一个近似4-2压缩器和与所述近似4-2压缩器连接的一组存储单元;

2.根据权利要求1所述的的单比特全数字存内计算单元,其特征在于,所述存储单元包括数据锁存结构以及两个导通的n管。

3.根据权利要求2所述的的单比特全数字存内计算单元,其特征在于,所述数据锁存结构包括首尾相接的两个反相器。

4.根据权利要求3所述的的单比特全数字存内计算单元,其特征在于,所述存储单元的两个n管的栅极由同一字线wl控制,两个n管的源漏接位线bl、blb和反相器。

5.根据权利要求4所述的的单比特全数字存内计算单元,其特征在于,同一列的存储单元使用同一位线进行连接。

6.根据权利要求1所述的的单比特全数字存内计算单元,其特征在于,每个存储单元的q端均与其同或门输入端进行连接,同或门的输入的另一端连接输入激励in,同或门的输出作为按位乘法结果进入到近似4-2压缩器中。

7.根据权利要求1所述的的单比特全数字存内计算单元,其特征在于,所述近似4-2压缩器为多个,每个近似4-2压缩器连接一组存储单元。

8.一种基于近似4-2压缩器的单比特全数字存内计算方法,其特征在于,基于权利要求1-7任一项所述的单比特全数字存内计算单元,包括:

9.根据权利要求8所述的基于近似4-2压缩器的单比特全数字存内计算方法,其特征在于,所述存储单元包括数据锁存结构以及两个导通的n管;

技术总结

本申请为一种基于近似4‑2压缩器的单比特全数字存内计算单元,该结构支持神经网络中的二值化的输入激励和权重进行乘累加,其中二值化网络中存在“+1”和“‑1”两个值,在电路中采用电压VDD代表“+1”,电压VSS代表“‑1”,VDD为电源电压,VSS为接地的零电压。对于最终的乘累加结果,可以看做是将其中“+1”的数量进行相加,即按照数字电路的高低电平进行相加,得到乘累加结果。每列的4个SRAM单元作为一个单元共用一个近似4‑2压缩器,得到最终的2bit近似乘累加结果。

技术研发人员:乔树山,曹景楠,游恒,尚德龙,周玉梅

受保护的技术使用者:中科南京智能技术研究院

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!