一种获取待执行指令的方法及系统与流程

本申请涉及计算机,更具体地涉及一种获取待执行指令的方法及系统。

背景技术:

1、本部分旨在为权利要求书中陈述的本申请的实施方式提供背景或上下文。此处的描述不因为包括在本部分中就承认是已被公开的现有技术。

2、随着工艺的演进,处理器的速度越来越快,由此带来内存墙的问题,即:存储器的速度赶不上处理器的速度,存储器的性能限制了处理器的性能发挥。对嵌入式系统来说,存在同样的问题,内部的非挥发存储器的速度比处理器的速度慢好几倍,每次读取一条指令,处理器需要等待多个周期。但是可以将内部的非挥发存储器的位宽增加到多条指令的宽度,使之存储器的数据吞吐量大于或等于处理器的吞吐量。

技术实现思路

1、本申请的目的在于提供一种获取待执行指令的方法,利用小容量的缓存区,可以提升存储器提取指令的性能,加快提取速度,减少处理器需要等待的周期。

2、本申请公开了一种获取待执行指令的方法,包括:

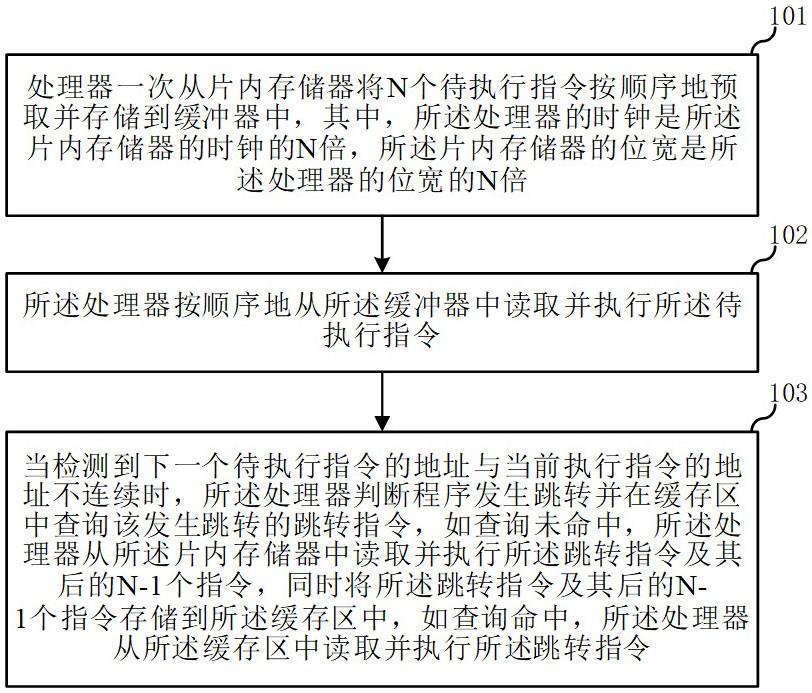

3、处理器一次从片内存储器将n个待执行指令按顺序地预取并存储到缓冲器中,其中,所述处理器的时钟是所述片内存储器的时钟的n倍,所述片内存储器的位宽是所述处理器的位宽的n倍;

4、所述处理器按顺序地从所述缓冲器中读取并执行所述待执行指令;以及

5、当检测到下一个待执行指令的地址与当前执行指令的地址不连续时,所述处理器判断程序发生跳转并在缓存区中查询该发生跳转的跳转指令,如查询未命中,所述处理器从所述片内存储器中读取并执行所述跳转指令及其后的n-1个指令,同时将所述跳转指令及其后的n-1个指令存储到所述缓存区中,如查询命中,所述处理器从所述缓存区中读取并执行所述跳转指令。

6、在一个优选例中,所述缓冲器包括第一缓冲器和第二缓冲器,所述第一缓冲器和所述第二缓冲器分别存储n个待执行指令,所述方法还包括:所述处理器一次从片内存储器将n个待执行指令按顺序地预取并依次交替地存储到所述第一缓冲器和所述第二缓冲器中。

7、在一个优选例中,所述处理器依次交替地从所述第一缓冲器和所述第二缓冲器中读取并执行存储其中的待执行指令。

8、在一个优选例中,所述处理器的时钟为100mhz,所述处理器的位宽为16位,所述片内存储器的时钟为25mhz,所述片内存储器的位宽为64位,所述n为4。

9、在一个优选例中,所述缓存区的容量为1kb~4kb。

10、在一个优选例中,所述缓存区包括多条缓存行,每条缓存行保存n个待执行指令,每条缓存行包括有效位、地址信息栏和n个待执行指令的指令信息。

11、在一个优选例中,还包括:从所述片内存储器预取位于所述跳转指令后的待执行指令并存储到所述缓冲器中。

12、本申请还公开了一种获取待执行指令的系统,包括:处理器、与所述处理器通信连接的片内存储器、缓冲器、缓存区,其中,所述处理器的时钟是所述片内存储器的时钟的n倍,所述片内存储器的位宽是所述处理器的位宽的n倍;其中,所述缓冲器中按顺序地存储有从所述片内存储器预取的n个待执行指令,所述缓存区中存储有跳转指令及每个跳转指令后的n-1个待执行指令;

13、其中,所述处理器按顺序地从所述缓冲器中读取并执行所述n个待执行指令,当检测到下一个待执行指令的地址与当前执行指令的地址不连续时,所述处理器判断程序发生跳转并在所述缓存区查询所述发生跳转的跳转指令,如查询未命中,所述处理器从所述片内存储器中读取并执行所述跳转指令及其后的n-1个指令,同时将所述跳转指令及其后的n-1个指令存储到所述缓存区中,如查询命中,所述处理器从所述缓存区中读取并执行所述跳转指令。

14、在一个优选例中,所述缓冲器包括第一缓冲器和第二缓冲器,所述第一缓冲器和所述第二缓冲器分别存储n个待执行指令,所述处理器一次从片内存储器将n个待执行指令按顺序地预取并依次交替地存储到所述第一缓冲器和所述第二缓冲器中。

15、本申请还公开了一种计算机可读存储介质,所述计算机可读存储介质中存储有计算机可执行指令,所述计算机可执行指令被处理器执行时实现如前文描述的方法中的步骤。

16、本申请实施方式与现有技术相比,主要区别及其效果在于:

17、本申请实施方式中,缓冲器中按顺序地存储有从片内存储器预取的多个待执行指令,缓存区中存储有跳转指令。当程序跳转时,处理器在缓存区查询跳转指令,如查询未命中,处理器从片内存储器中读取并执行跳转指令,同时将跳转指令存储到缓存区中,如查询命中,处理器从缓存区中读取并执行跳转指令。本申请利用小容量的缓存区可以提升存储器提取指令的性能,加快提取速度,减少处理器需要等待的周期,硬件开销小,可以在低成本的情况下达到和大容量缓存区相同的性能。

18、本申请的说明书中记载了大量的技术特征,分布在各个技术方案中,如果要罗列出本申请所有可能的技术特征的组合(即技术方案)的话,会使得说明书过于冗长。为了避免这个问题,本申请上述

技术实现要素:

中公开的各个技术特征、在下文各个实施方式和例子中公开的各技术特征、以及附图中公开的各个技术特征,都可以自由地互相组合,从而构成各种新的技术方案(这些技术方案均应该视为在本说明书中已经记载),除非这种技术特征的组合在技术上是不可行的。例如,在一个例子中公开了特征a+b+c,在另一个例子中公开了特征a+b+d+e,而特征c和d是起到相同作用的等同技术手段,技术上只要择一使用即可,不可能同时采用,特征e技术上可以与特征c相组合,则,a+b+c+d的方案因技术不可行而应当不被视为已经记载,而a+b+c+e的方案应当视为已经被记载。

技术特征:

1.一种获取待执行指令的方法,其特征在于,包括:

2.根据权利要求1所述的方法,其特征在于,所述缓冲器包括第一缓冲器和第二缓冲器,所述第一缓冲器和所述第二缓冲器分别存储n个待执行指令,所述方法还包括:所述处理器一次从片内存储器将n个待执行指令按顺序地预取并依次交替地存储到所述第一缓冲器和所述第二缓冲器中。

3.根据权利要求2所述的方法,其特征在于,所述处理器依次交替地从所述第一缓冲器和所述第二缓冲器中读取并执行存储其中的待执行指令。

4.根据权利要求1所述的方法,其特征在于,所述处理器的时钟为100mhz,所述处理器的位宽为16位,所述片内存储器的时钟为25mhz,所述片内存储器的位宽为64位,所述n为4。

5.根据权利要求1所述的方法,其特征在于,所述缓存区的容量为1kb~4kb。

6.根据权利要求1所述的方法,其特征在于,所述缓存区包括多条缓存行,每条缓存行保存n个待执行指令,每条缓存行包括有效位、地址信息栏和n个待执行指令的指令信息。

7.根据权利要求1所述的方法,其特征在于,还包括:从所述片内存储器预取位于所述跳转指令后的待执行指令并存储到所述缓冲器中。

8.一种获取待执行指令的系统,其特征在于,包括:处理器、与所述处理器通信连接的片内存储器、缓冲器、以及缓存区,其中,所述处理器的时钟是所述片内存储器的时钟的n倍,所述片内存储器的位宽是所述处理器的位宽的n倍;其中,所述缓冲器中按顺序地存储有从所述片内存储器预取的n个待执行指令,所述缓存区中存储有跳转指令及每个跳转指令后的n-1个待执行指令;

9.根据权利要求8所述的系统,其特征在于,所述缓冲器包括第一缓冲器和第二缓冲器,所述第一缓冲器和所述第二缓冲器分别存储n个待执行指令,所述处理器一次从片内存储器将n个待执行指令按顺序地预取并依次交替地存储到所述第一缓冲器和所述第二缓冲器中。

10.一种计算机可读存储介质,其特征在于,所述计算机可读存储介质中存储有计算机可执行指令,所述计算机可执行指令被处理器执行时实现如权利要求1至7中任意一项所述的方法中的步骤。

技术总结

本申请涉及计算机技术领域,公开一种获取待执行指令的方法及系统,所述方法包括:处理器一次从片内存储器将N个待执行指令按顺序地预取并存储到缓冲器中,处理器的时钟是片内存储器的N倍,片内存储器的位宽是处理器的N倍;处理器按顺序地从缓冲器中读取并执行待执行指令;当检测到下一个待执行指令的地址与当前执行指令不连续时,判断程序跳转并在缓存区中查询跳转指令,如查询未命中,处理器从片内存储器中读取并执行跳转指令及其后的N‑1个指令,同时将跳转指令及其后的N‑1个指令存储到缓存区中,如查询命中,处理器从缓存区中读取并执行跳转指令。本申请利用小容量的缓存区,可以在低成本的情况下达到和大容量缓存区相同的性能。

技术研发人员:请求不公布姓名

受保护的技术使用者:上海灵动微电子股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!