一种ARM芯片cache命中率的测试方法与流程

一种arm芯片cache命中率的测试方法,属于通信及计算机领域。

背景技术:

1、在arm架构下,cache是一种高速缓存,用于临时存储数据和指令,缓存常常作为系统的数据缓冲,将频繁访问的数据放入缓存中,避免多次到数据库,或者文件系统,以提高内存访问速度。在缓存系统中的一个核心指标为命中率(hit rate),命中率等于读取请求返回存在的次数/总共的读取次数。其中,命中是指读取某一数据时,假若该数据存在,则是命中;非命中(miss)是指读取某一数据时,假若该数据不存在,则是非命中。缓存命中率的高低与用户的使用逻辑关系密切。当命中率低时,是不能提升系统的性能的,所以命中率的高低直接影响系统的响应时间和整体吞吐量。然而,由于cache容量有限,命中率的高低会直接影响系统的性能和效率。因此需要准确测试arm芯片cache的命中率。

2、在现有技术中,arm芯片cache命中率的测试通常有两种方法:模拟器模拟和实际部署测试。其中,模拟器模拟是通过模拟不同负载和运行环境下的性能指标来测试cache命中率,但由于是虚拟的测试环境,测试结果可能与实际情况不同。并且模拟器模拟还存在如下缺陷:测试结果不够准确:由于采用的是软件模拟器,不能完全模拟真实的硬件环境,因此测试结果可能与实际情况存在偏差。(2)测试成本高:为实现准确的测试结果,需要用到高性能的软件模拟器,这样往往需要消耗大量的计算资源。

3、而实际部署测试是通过在实际硬件上运行程序来测试cache命中率,但该方法需要大量的时间和资源,并且在实际应用中不便实现,同时实际部署测试还存在如下缺陷:(1)测试周期长:需要在实际环境中部署测试程序,需要花费大量的时间来收集和分析测试结果。(2)测试成本高:需要大量的硬件资源,如arm芯片、开发板等,并且需要熟悉arm芯片的架构和编程方法,才能进行测试。(3)不方便实现:需要对硬件进行改动和部署。

4、因此设计一种简单易行的arm芯片cache命中率的测试方法,成为本领域亟待解决的问题。

技术实现思路

1、本发明要解决的技术问题是:克服现有技术的不足,提供一种采用了基于引用计数的cache分析方法,通过记录cache的命中次数和访问次数,可以准确测量cache的访问时间和命中率,为优化arm芯片的cache提供基础数据的arm芯片cache命中率的测试方法。

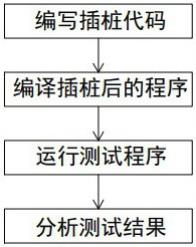

2、本发明解决其技术问题所采用的技术方案是:该arm芯片cache命中率的测试方法,其特征在于:包括如下步骤:

3、步骤a,根据需要测试的测试程序的编程语言和目标平台,编写插桩代码;

4、步骤b,将步骤a中编译的插桩代码和测试程序进行合并,并进行编译和链接,生成带有插桩代码的二进制可执行文件;

5、步骤c,在目标平台上运行测试程序;

6、步骤d,分析测试结果,根据插桩代码记录的cache的命中次数和访问次数,计算出cache当前测试的命中率,并与前次测试的命中率进行比较。

7、优选的,步骤c包括如下步骤:

8、步骤c-1,确定测试的硬件环境;

9、步骤c-2,搭建测试的软件环境;

10、步骤c-3,启动测试程序。

11、优选的,步骤c-3包括如下步骤:

12、步骤c-3-1,运行测试程序,运行测试程序,并确保测试程序正确地访问arm芯片的cache;

13、步骤c-3-2,对cache的命中次数和访问次数进行记录和追踪;

14、步骤c-3-3,测试程序运行时间的记录:记录测试程序的运行时间。

15、优选的,在步骤a中,使用系统调用或者cpu周期计数器记录cache的访问次数和命中次数。

16、与现有技术相比,本发明所具有的有益效果是:

17、1、在本arm芯片cache命中率的测试方法中,采用了基于引用计数的cache分析方法,通过记录cache的命中次数和访问次数,可以准确测量cache的访问时间和命中率,为优化arm芯片的cache提供基础数据。

18、2、本arm芯片cache命中率的测试方法,可以准确测试arm芯片的cache命中率和其他性能指标,避免了因参数误差等原因造成的测试偏差和结果不准确的情况。

19、3、通过引用计数的cache分析方法,可以避免擦除cache数据、清空cache等影响测试结果的情况,得到更加准确和实际的测试数据。

20、4、本arm芯片cache命中率的测试方法,简单易行、成本低廉,可以广泛应用于arm芯片的性能测试和调优工作。

21、5、测试程序采用汇编语言编写,能够提高程序的执行效率和稳定性,确保测试结果的准确性和可靠性。

技术特征:

1.一种arm芯片cache命中率的测试方法,其特征在于:包括如下步骤:

2.根据权利要求1所述的arm芯片cache命中率的测试方法,其特征在于:步骤c包括如下步骤:

3.根据权利要求2所述的arm芯片cache命中率的测试方法,其特征在于:步骤c-3包括如下步骤:

4.根据权利要求1所述的arm芯片cache命中率的测试方法,其特征在于:在步骤a中,使用系统调用或者cpu周期计数器记录cache的访问次数和命中次数。

技术总结

一种ARM芯片cache命中率的测试方法,属于通信及计算机领域。ARM芯片cache命中率的测试方法,其特征在于:包括如下步骤:步骤a,根据需要测试的测试程序的编程语言和目标平台,编写插桩代码;步骤b,将步骤a中编译的插桩代码和测试程序进行合并,并进行编译和链接,生成带有插桩代码的二进制可执行文件;步骤c,在目标平台上运行测试程序;步骤d,分析测试结果,根据插桩代码记录的Cache的命中次数和访问次数,计算出cache当前测试的命中率,并与前次测试的命中率进行比较。在本ARM芯片cache命中率的测试方法中,采用了基于引用计数的Cache分析方法,通过记录Cache的命中次数和访问次数,可以准确测量Cache的访问时间和命中率,为优化ARM芯片的Cache提供基础数据。

技术研发人员:张弘毅

受保护的技术使用者:上海磐易科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!