一种利用备份回溯克服单粒子翻转失效的存算架构FPGA的制作方法

本申请涉及fpga,尤其是一种利用备份回溯克服单粒子翻转失效的存算架构fpga。

背景技术:

1、随着物联网、云计算和人工智能等高新技术的发展,依托于硬件平台实现的各类数据密集型应用也急剧增长。fpga(field programmable gate array,可编程阵列逻辑)因具有并行性和可重构性的优势,是目前常用的硬件平台。

2、现有的fpga与大多数传统的硬件平台一样,都采用冯诺依曼架构,fpga内部包含大量的诸如clb、dsp和bram之类的资源模块,这些资源模块之间通过高度可配置的互连线连接起来,形成为fpga中的计算单元和存储单元。bram作为片上重要的存储单元,片上数据主要存储在bram中,而计算时又要将片上数据传输到计算单元中。

3、因此现有的fpga与其他采用冯诺依曼架构的硬件平台一样,在执行各种计算任务的过程中,需要在存储单元和计算单元之间反复传输大量的数据,频繁且大量的数据搬移不仅会消耗大量的布线资源和互连资源,还会导致巨大的延迟和能量损耗,从而限制了fpga的数据处理效率。

技术实现思路

1、本申请人针对上述问题及技术需求,提出了一种利用备份回溯克服单粒子翻转失效的存算架构fpga,本申请的技术方案如下:

2、一种利用备份回溯克服单粒子翻转失效的存算架构fpga,该存算架构fpga内部包括按照预定结构排列的若干个资源模块、环于资源模块设置的互连资源以及额外的硬件资源实现的全局读写通道,位于同一个子区域内的资源模块通过存算架构fpga内部的互连资源相连以实现一个存算单元,每个存算单元包括处理器和本地存储单元,每个存算单元的本地存储单元用于存储存算单元的指令和数据,每个存算单元中的处理器经由互连资源连接同一个存算单元中的本地存储单元并按照本地存储单元存储的指令和数据运算;多个不同的子区域内的资源模块对应实现多个存算单元,且每个存算单元中的本地存储单元通过全局读写通道与存算架构fpga的片外进行数据传输;

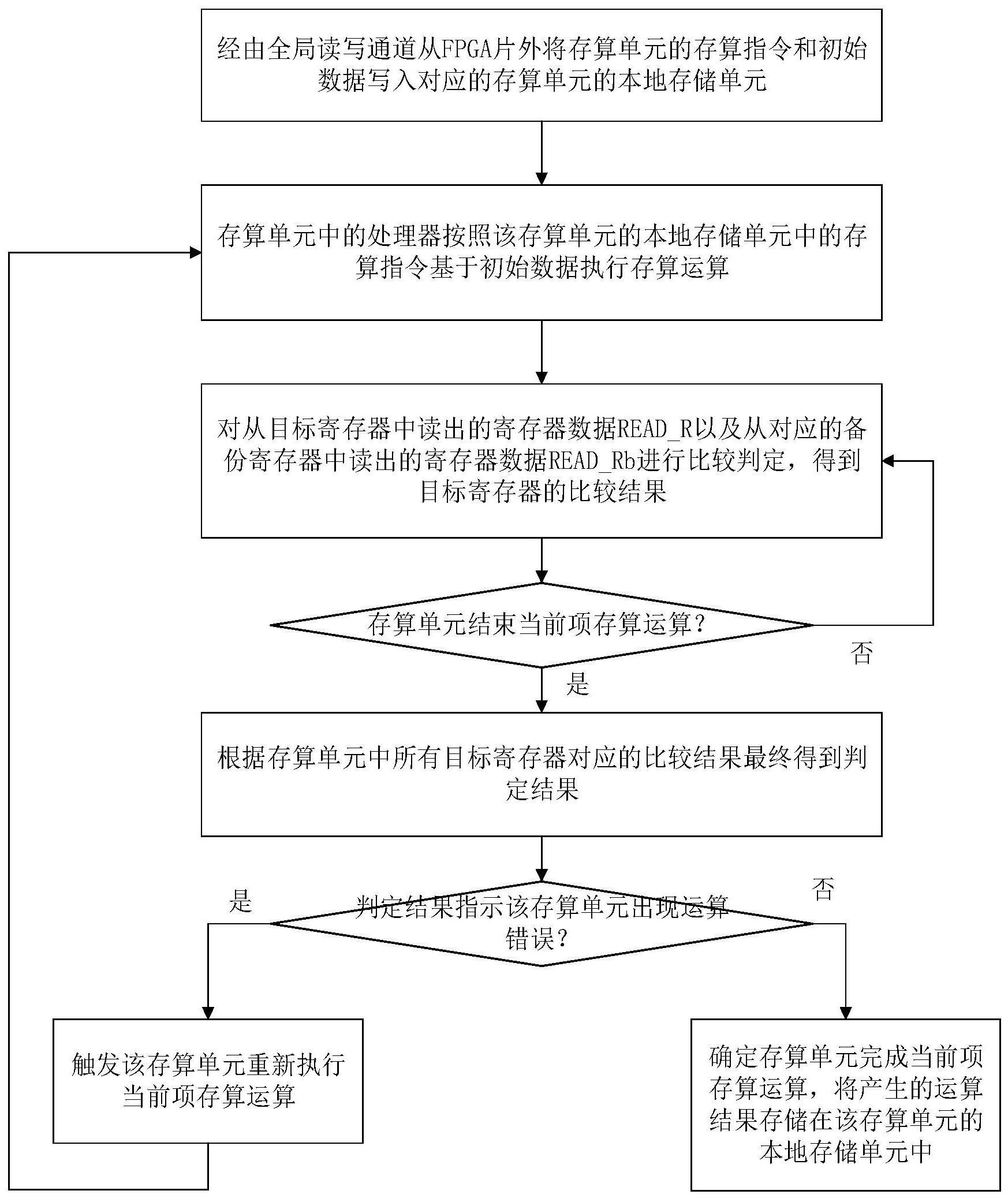

3、存在至少一个存算单元包含目标寄存器对应的备份寄存器以及判定电路,目标寄存器是存算单元中会受到单粒子翻转影响的寄存器,在存算单元执行一项存算运算的过程中,每个目标寄存器对应的备份寄存器用于备份存储写入目标寄存器中的寄存器数据,判定电路对从目标寄存器及其对应的备份寄存器中分别读出的寄存器数据进行比较判定,并在存算单元结束当前项存算运算时得到判定结果,当判定电路得到的判定结果指示存算单元出现运算错误时,触发存算单元重新执行当前项存算运算,否则确定存算单元完成当前项存算运算。

4、其进一步的技术方案为,当判定电路比较确定一个目标寄存器及其对应的备份寄存器中分别读出的寄存器数据一致时,确定目标寄存器对应的比较结果为寄存器数据正确,否则确定目标寄存器对应的比较结果为寄存器数据错误;当存算单元结束当前项存算运算时,根据存算单元中所有目标寄存器对应的比较结果得到判定结果。

5、其进一步的技术方案为,当存算单元中比较结果为寄存器数据错误的目标寄存器的数量达到预定阈值时,得到指示存算单元出现运算错误的判定结果。

6、其进一步的技术方案为,判定电路包括比较器和计数器,比较器用于对目标寄存器及其对应的备份寄存器进行比较,计数器用于对比较结果为寄存器数据错误的目标寄存器的数量进行计数。

7、其进一步的技术方案为,判定电路包括比较器,比较器用于对目标寄存器及其对应的备份寄存器进行比较,存算单元中的处理器内部的状态单元的状态寄存器用于对比较结果为寄存器数据错误的目标寄存器的数量进行计数。

8、其进一步的技术方案为,读取存算单元中的处理器内部的状态单元的状态寄存器的预定位数,得到比较结果为寄存器数据错误的目标寄存器的数量。

9、其进一步的技术方案为,预定阈值可调,且存算架构fpga对存算单元执行存算运算得到的运算结果的准确性要求越高,预定阈值越小。

10、其进一步的技术方案为,触发存算单元重新执行当前项存算运算,包括:

11、在确定判定结果指示存算单元出现运算错误后,延时预定时长后,触发存算单元重新执行当前项存算运算。

12、其进一步的技术方案为,存算单元在执行一项存算运算时,存算指令和初始数据经由全局读写通道写入存算单元的本地存储单元,存算单元中的处理器按照存算指令基于初始数据执行存算运算,且在执行存算运算的过程中,本地存储单元中储存的存算指令和初始数据保持不变;

13、存算单元重新执行当前存算运算包括:存算单元中的处理器重新按照存算指令基于初始数据执行存算运算。

14、本申请的有益技术效果是:

15、本申请公开了一种利用备份回溯克服单粒子翻转失效的存算架构fpga,该存算架构fpga中位于同一个子区域内的资源模块通过fpga内部的互连资源相连以实现一个存算单元,另外针对单粒子翻转密集的应用场景,该存算架构fpga中的存算单元为会受到单粒子翻转影响的目标寄存器添加对应的备份寄存器,在执行存算运算的过程中,对从目标寄存器及其对应的备份寄存器中分别读出的寄存器数据进行比较判定,并在存算单元结束当前项存算运算时确定是否保存运算结果或者触发重新执行存算运算,可以避免在单粒子翻转密集的应用场景中由于单粒子翻转失效带来的瞬态错误而导致的运算错误,从而可以在通过多存算单元实现并行的多核存算运算时提高运行可靠性,具有突出的数据处理效率、运算速度和运行可靠性。

16、本申请存算架构fpga主要适用于单粒子翻转密集的应用场景,在存算单元完成一项存算运算后判定是否触发重新执行,避免由于单粒子翻转密集出现而影响存算运算正常执行过程的现象。

17、fpga内部形成的每个存算单元中的处理器和本地数据存储都在同一个子区域内,处理器在执行时只需读写邻近的本地数据存储中的数据,减少了处理器和本地数据存储之间传输数据所消耗的布线资源和互连资源,减少了数据传输延迟和能量损耗,提高了fpga的数据处理效率。另外fpga可以通过多个存算单元实现多核并行的存算运算,各个存算单元的处理器彼此间不会造成冲突,各个存算单元可以各自全速执行运算,不受存储带宽的影响,可以进一步提升fpga整体数据处理效率和运算速度。

技术特征:

1.一种利用备份回溯克服单粒子翻转失效的存算架构fpga,其特征在于,所述存算架构fpga内部包括按照预定结构排列的若干个资源模块、环于资源模块设置的互连资源以及额外的硬件资源实现的全局读写通道,位于同一个子区域内的资源模块通过所述存算架构fpga内部的互连资源相连以实现一个存算单元,每个存算单元包括处理器和本地存储单元,每个存算单元的本地存储单元用于存储所述存算单元的指令和数据,每个存算单元中的处理器经由互连资源连接同一个存算单元中的本地存储单元并按照所述本地存储单元存储的指令和数据运算;多个不同的子区域内的资源模块对应实现多个存算单元,且每个存算单元中的本地存储单元通过全局读写通道与所述存算架构fpga的片外进行数据传输;

2.根据权利要求1所述的存算架构fpga,其特征在于,

3.根据权利要求2所述的存算架构fpga,其特征在于,

4.根据权利要求3所述的存算架构fpga,其特征在于,所述判定电路包括比较器和计数器,所述比较器用于对目标寄存器及其对应的备份寄存器进行比较,所述计数器用于对比较结果为寄存器数据错误的目标寄存器的数量进行计数。

5.根据权利要求3所述的存算架构fpga,其特征在于,所述判定电路包括比较器,所述比较器用于对目标寄存器及其对应的备份寄存器进行比较,所述存算单元中的处理器内部的状态单元的状态寄存器用于对比较结果为寄存器数据错误的目标寄存器的数量进行计数。

6.根据权利要求5所述的存算架构fpga,其特征在于,读取所述存算单元中的处理器内部的状态单元的状态寄存器的预定位数,得到比较结果为寄存器数据错误的目标寄存器的数量。

7.根据权利要求3所述的存算架构fpga,其特征在于,所述预定阈值可调,且所述存算架构fpga对存算单元执行存算运算得到的运算结果的准确性要求越高,所述预定阈值越小。

8.根据权利要求1所述的存算架构fpga,其特征在于,所述触发所述存算单元重新执行当前项存算运算,包括:

9.根据权利要求8所述的存算架构fpga,其特征在于,所述存算单元在执行一项存算运算时,存算指令和初始数据经由所述全局读写通道写入所述存算单元的本地存储单元,所述存算单元中的处理器按照所述存算指令基于所述初始数据执行存算运算,且在执行存算运算的过程中,所述本地存储单元中储存的存算指令和初始数据保持不变;

技术总结

本申请公开了一种利用备份回溯克服单粒子翻转失效的存算架构FPGA,涉及FPGA领域,该存算架构FPGA内部实现多个存算单元,另外针对单粒子翻转密集的应用场景,存算单元中会受到单粒子翻转影响的目标寄存器有对应的备份寄存器,在执行存算运算的过程中,对从目标寄存器及其对应的备份寄存器中分别读出的寄存器数据进行比较判定,并在存算单元结束当前项存算运算时确定是否保存运算结果或者触发重新执行存算运算,可以避免在单粒子翻转密集的应用场景中由于单粒子翻转失效带来的瞬态错误而导致的运算错误,从而可以在通过多存算单元实现并行的多核存算运算时提高运行可靠性。

技术研发人员:单悦尔,徐彦峰,季振凯

受保护的技术使用者:无锡中微亿芯有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!