一种FPGA在线调试方法及支持在线调试的FPGA与流程

本发明涉及电数字数据处理领域,具体涉及一种fpga(field-programmable gatearray,现场可编程门阵列)在线调试方法及支持在线调试的fpga。

背景技术:

1、随着ai(artificial intelligence,人工智能)技术不断探索,fpga应用技术被推到前所未有的高点。板级仿真验证调试作为fpga开发流程中最后的一个环节,是评价fpga设计是否成功、评价fpga eda(electronic design automation,电子设计自动化)工具以及fpga芯片的关键手段。

2、现有技术中,板级仿真验证调试需要用到fpga软件的在线逻辑分析仪,并配合外部的逻辑分析仪或示波器等仪器设备,来监控和分析芯片的工作状态,以检查设计是否有功能错误。其中,在线逻辑分析仪采用在线逻辑分析ip(intellectual property)+用户应用设计同时进行布局布线的方式,可以灵活的查看fpga应用的内部信号。

3、但是,在线逻辑分析ip会占用fpga内部逻辑资源,尤其是随着要调试的用户应用设计信号的增多,资源占用就更多;一方面会抢占用户的设计资源,另一方面当使用在线逻辑分析ip的用户设计变化较大时,布局布线的结果就发生大的变化,在临界条件下,例如软件报告的最大系统时钟跟用户应用时钟相近的条件下,会降低用户设计调试的有效性。

技术实现思路

1、为了解决现有技术中所存在的上述问题,本发明提供了一种fpga在线调试方法及支持在线调试的fpga。

2、本发明要解决的技术问题通过以下技术方案实现:

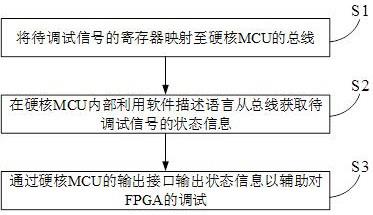

3、一种fpga在线调试方法,应用于fpga,所述fpga内嵌硬核mcu,所述方法包括:

4、将待调试信号的寄存器映射至所述硬核mcu(microcontroller unit,微控制单元)的总线;

5、在所述硬核mcu内部利用软件描述语言从所述总线获取所述待调试信号的状态信息;

6、通过所述硬核mcu的输出接口输出所述状态信息以辅助对所述fpga的调试。

7、优选地,所述方法还包括:

8、在所述硬核mcu内部利用软件描述语言对所述待调试信号进行逻辑组合,并基于所获取的状态信息得到对应的逻辑组合结果;

9、通过所述硬核mcu的输出接口输出所述逻辑组合结果以进一步辅助对所述fpga的调试。

10、优选地,所述将待调试信号的寄存器映射至所述硬核mcu的总线,包括:

11、预先将所述硬核mcu的总线根据地址进行拆分;

12、将不同的待调试信号分别映射至所述总线的不同地址上。

13、优选地,所述将不同的待调试信号分别映射至所述总线的不同地址上,包括:

14、采用硬件描述语言定义的连接线,将不同的待调试信号与所述总线的不同地址分别进行关联。

15、优选地,所述将待调试信号的寄存器映射至所述硬核mcu的总线的操作占用fpga资源。

16、优选地,通过所述硬核mcu的uart接口或jtag接口输出所述状态信息,通过所述硬核mcu的gpio接口输出所述逻辑组合结果。

17、优选地,所述总线包括:amba总线或wishbone总线。

18、本发明还提供了一种支持在线调试的fpga,所述fpga包括:用户设计模块、总线映射模块以及内嵌的硬核mcu;

19、所述用户设计模块中包含待调试信号;

20、所述总线映射模块,用于将所述待调试信号的寄存器映射至所述硬核mcu的总线;

21、所述硬核mcu,用于利用软件描述语言从所述总线获取所述待调试信号的状态信息,并通过自身的输出接口输出所述状态信息以辅助对所述fpga的调试。

22、优选地,所述硬核mcu,还用于:

23、利用软件描述语言对所述待调试信号进行逻辑组合,并基于所获取的状态信息得到对应的逻辑组合结果;

24、通过所述输出接口输出所述逻辑组合结果以进一步辅助对所述fpga的调试。

25、优选地,所述总线映射模块,具体用于:

26、采用硬件描述语言定义的连接线,将不同的待调试信号与所述总线的不同地址分别进行关联。

27、本发明提供的fpga在线调试方法,在硬核mcu+fpga架构的基础上,将需要调试的用户设计的内部信号通过硬核mcu的总线读入,然后通过硬核mcu的输出接口进行输出以辅助对fpga的调试。由于硬核mcu不占用fpga资源,因此相较于在线逻辑分析ip占用fpga资源的调试方式来说,本发明减少了对fpga内部资源的利用,使得在线调试的设计更贴近用户设计本身,从而增加了临界条件下的调试效率。

28、以下将结合附图及对本发明做进一步详细说明。

技术特征:

1.一种fpga在线调试方法,其特征在于,应用于fpga,所述fpga内嵌硬核mcu,所述方法包括:

2.根据权利要求1所述的fpga在线调试方法,其特征在于,所述方法还包括:

3.根据权利要求1所述的fpga在线调试方法,其特征在于,所述将待调试信号的寄存器映射至所述硬核mcu的总线,包括:

4.根据权利要求3所述的fpga在线调试方法,其特征在于,所述将不同的待调试信号分别映射至所述总线的不同地址上,包括:

5.根据权利要求2所述的fpga在线调试方法,其特征在于,通过所述硬核mcu的uart接口或jtag接口输出所述状态信息,通过所述硬核mcu的gpio接口输出所述逻辑组合结果。

6.根据权利要求1所述的fpga在线调试方法,其特征在于,所述总线包括:amba总线或wishbone总线。

7.一种支持在线调试的fpga,其特征在于,所述fpga包括:用户设计模块、总线映射模块以及内嵌的硬核mcu;

8.根据权利要求7所述的支持在线调试的fpga,其特征在于,所述硬核mcu,还用于:

9.根据权利要求7所述的支持在线调试的fpga,其特征在于,所述总线映射模块,具体用于:

技术总结

本发明公开了一种FPGA在线调试方法,应用于FPGA,所述FPGA内嵌硬核MCU,所述方法包括:将待调试信号的寄存器映射至所述硬核MCU的总线;在所述硬核MCU内部利用软件描述语言从所述总线获取所述待调试信号的状态信息;通过所述硬核MCU的输出接口输出所述状态信息以辅助对所述FPGA的调试。本发明减少了对FPGA内部资源的利用,使得在线调试的设计更贴近用户设计本身,从而增加了临界条件下的调试效率。

技术研发人员:崔明章,贾红,韦嶔,张红荣

受保护的技术使用者:西安智多晶微电子有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!