两模冗余系统以及FPGA实现两模冗余仲裁机制的方法与流程

本发明涉及计算机数据处理应用,特别涉及一种两模冗余系统以及fpga实现两模冗余仲裁机制的方法。

背景技术:

1、冗余计算机系统需要多台计算机设备之间,或者同一计算机设备中的多块主板之间进行冗余备份,目前主流的实现方案为软件进行冗余仲裁,随着cpu处理数据量增加、设备间数据传输速率提高,该方案不能满足应用需求。

技术实现思路

1、本发明提供了一种两模冗余系统以及fpga实现两模冗余仲裁机制的方法,以解决通过软件进行冗余仲裁不能满足应用需求的技术问题。

2、为达到上述目的,本发明的技术方案是这样实现的:

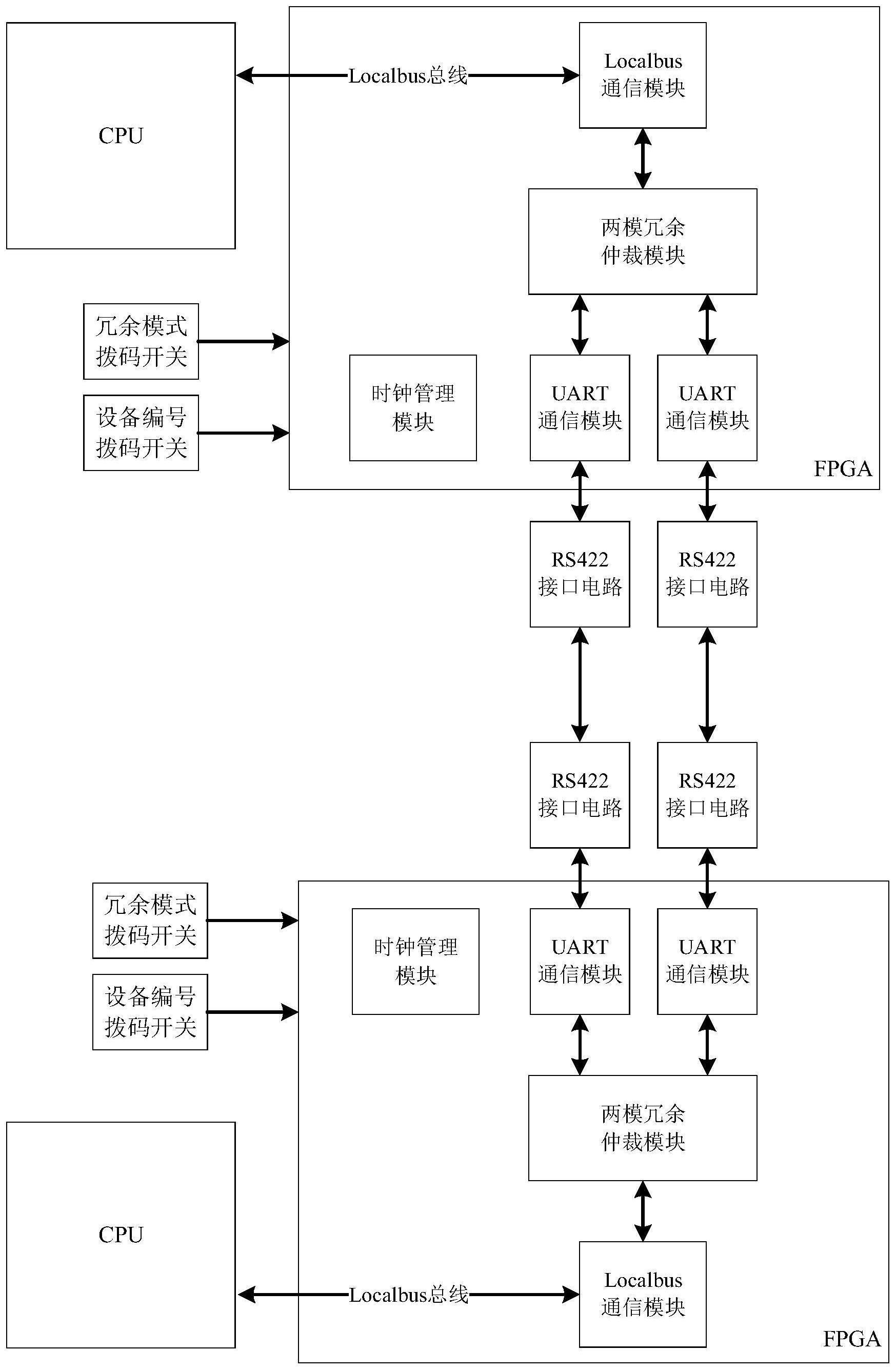

3、本发明一方面提供了一种两模冗余系统,包括第一设备端和第二设备端;

4、第一设备端和第二设备端均包括cpu、现场可编程门阵列、拨码开关组件和若干接口电路;第一设备端上的若干接口电路和第二设备端上的若干接口电路分别通过串口电连接;

5、cpu通过总线与现场可编程门阵列电连接,用于与现场可编程门阵列进行通信,通过总线向现场可编程门阵列写入cpu的心跳信号,以表征cpu当前正在工作或发生宕机;并向现场可编程门阵列写入主从切换指令,进行设备主从状态切换;拨码开关组件和若干接口电路均与现场可编程门阵列电连接,第一设备端上的若干接口电路和第二设备端上的若干接口电路分别通过串口电连接。

6、进一步地,现场可编程门阵列包括局部总线通信模块、两模冗余仲裁模块、时钟管理模块和若干个串口通信模块;

7、局部总线通信模块的一端与cpu通过总线连接,另一端通过与两模冗余仲裁模块电连接;局部总线通信模块用于与cpu进行通信,接收cpu的心跳信号,以表征cpu当前正在工作或发生宕机;

8、两模冗余仲裁模块通过若干个串口通信模块分别与若干接口电路电连接;两模冗余仲裁模块用于实现两模冗余仲裁机制,根据当前设备编号、局部总线通信模块发送的cpu心跳信号和cpu的主从切换指令、以及通过若干接口电路接收的冗余状态数据包,进行冗余状态实时切换;同时产生冗余状态数据包,并通过串口通信模块向第一设备端或者第二设备端发送数据包;

9、时钟管理模块用于产生现场可编程门阵列工作主时钟,以及给cpu的总线产生工作主时钟。

10、进一步地,第一设备端和第二设备端上接口电路的数量均设置有两个;现场可编程门阵列中的串口通信模块的数量设置为两个。

11、进一步地,所述拨码开关组件包括冗余模式拨码开关和设备编号拨码开关;

12、冗余模式拨码开关和设备编号拨码开关均与现场可编程门阵列电连接,冗余模式拨码开关用于设置第一设备端或者第二设备端的冗余模式;设备编号拨码开关用于设置第一设备端或者第二设备端的设备编号。

13、进一步地,所述接口电路选用nsi83086芯片。

14、进一步地,所述现场可编程门阵列集成有pll核,用于产生多路不同频率的时钟输出。

15、本发明另一方面还提供一种fpga实现两模冗余仲裁机制的方法,现场可编程门阵列在以上所述的两模冗余系统中实现两模冗余仲裁机制,具体包括如下步骤:

16、s2、时钟管理模块启动,并向自身的现场可编程门阵列产生工作主时钟,以及给自身的cpu的总线产生工作主时钟;第一设备端和第二设备端分别通过各自的时钟管理模块进行时间同步;

17、s3、局部总线通信模块将接收的cpu发送的数据发送给自身的两模冗余仲裁模块,同时将两模冗余仲裁模块产生的自身冗余状态数据包和接口电路接收的冗余状态数据包发送给cpu;

18、s4、两模冗余仲裁模块根据接收的cpu发送的数据、自身冗余状态数据包以及接收的冗余状态数据包,进行冗余状态实时切换;

19、进一步地,所述s3中的cpu发送的数据包括cpu心跳信号以及cpu的主从切换指令。

20、进一步地,所述s4具体包含如下步骤:

21、s41、两模冗余仲裁模块产生第一设备端或者第二设备端自身的冗余状态数据包用于发送给自身的串口通信模块和自身的局部总线通信模块;

22、s42、串口通信模块将自身冗余状态数据包通过自身的接口电路传输给第二设备端或者第一设备端的现场可编程门阵列中;

23、s43、自身的局部总线通信模块将自身的冗余状态数据包传输给自身的cpu,cpu根据自身的冗余状态数据包形成cpu的主从切换指令,并通过局部总线通信模块传输给自身的两模冗余仲裁模块;

24、s44、两模冗余仲裁模块根据接收的cpu发送的数据、自身冗余状态数据包以及接收的冗余状态数据包,进行冗余状态实时切换。

25、进一步地,在s2之前还包括s1;

26、s1、通过第一设备端和第二设备端上的拨码开关组件分别设置第一设备端和第二设备端的冗余模式以及设备编号。

27、本发明的有益效果:

28、本发明采用现场可编程门阵列实现两模冗余仲裁机制,提高了冗余仲裁的实时性和灵敏度,同时可释放cpu性能用于业务数据处理。

技术特征:

1.两模冗余系统,其特征在于:包括第一设备端和第二设备端;

2.根据权利要求1所述的两模冗余系统,其特征在于,现场可编程门阵列包括局部总线通信模块、两模冗余仲裁模块、时钟管理模块和若干个串口通信模块;

3.根据权利要求2所述的两模冗余系统,其特征在于,第一设备端和第二设备端上接口电路的数量均设置有两个;现场可编程门阵列中的串口通信模块的数量设置为两个。

4.根据权利要求1所述的两模冗余系统,其特征在于,所述拨码开关组件包括冗余模式拨码开关和设备编号拨码开关;

5.根据权利要求1所述的两模冗余系统,其特征在于,所述接口电路选用nsi83086芯片。

6.fpga实现两模冗余仲裁机制的方法,其特征在于,现场可编程门阵列在权利要求1所述的两模冗余系统中实现两模冗余仲裁机制,具体包括如下步骤:

7.根据权利要求6所述的fpga实现两模冗余仲裁机制的方法,其特征在于,所述s3中的cpu发送的数据包括cpu心跳信号以及cpu的主从切换指令。

8.根据权利要求6所述的fpga实现两模冗余仲裁机制的方法,其特征在于,所述s4具体包含如下步骤:

9.根据权利要求6所述的fpga实现两模冗余仲裁机制的方法,其特征在于,在s2之前还包括s1;

技术总结

本发明涉及计算机数据处理应用领域,具体为一种两模冗余系统,包括第一设备端和第二设备端;第一设备端和第二设备端均包括CPU、现场可编程门阵列、拨码开关组件和若干接口电路;第一设备端上的若干接口电路和第二设备端上的若干接口电路分别通过串口电连接;CPU通过总线与现场可编程门阵列电连接;拨码开关组件和若干接口电路均与现场可编程门阵列电连接,第一设备端上的若干接口电路和第二设备端上的若干接口电路分别通过串口电连接。本发明采用现场可编程门阵列实现两模冗余仲裁机制,提高了冗余仲裁的实时性和灵敏度,同时可释放CPU性能用于业务数据处理。

技术研发人员:陈龙,李明,龙玉湘,金广涛

受保护的技术使用者:湖南航天捷诚电子装备有限责任公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!