一种基于理查森外推法的数字微分器及其优化结构的制作方法

本发明涉及数字信号处理,特别涉及一种基于理查森外推法的数字微分器及其优化结构。

背景技术:

1、数字微分器是数字信号处理领域应用较为广泛的一种电路结构,在图像识别、医疗工程、数字信号处理以及模数转换器校准领域都有不可或缺的作用。针对与斜率相关问题或者基于泰勒级数展开式来推导的问题,都会需要涉及信号的导数值,这就需要微分器的存在。对于一个数字信号输出:

2、其中为整个系统的采样周期,n为系统的采样点。若需要求数字信号在某个点的导数值,根据基于5点公式的拉格朗日插值多项式的一阶微分公式可以近似得到该信号的导数表达为:

3、将用泰勒级数展开式展开表示为:

4、

5、将分别带入上述表达式中化简就可以得到和理想导数之间的关系式为:

6、可以看出利用5点公式的拉格朗日插值多项式的一阶微分公式得到的导数值与理想导数值之间的截断误差为:

7、表示实际导数值与理想导数值之间的截断误差,可以看出两者之间的误差在五次项以上。利用5点公式的拉格朗日插值多项式的一阶微分公式所得到的电路结构如图1所示。该结构的精度偏低,如果从频域来观察可以发现,幅频响应曲线较为陡峭且随着频率的提高,衰减会极具恶化,对求导运算带来较大的偏差。

技术实现思路

1、本发明的目的在于提供一种基于理查森外推法的数字微分器及其优化结构,以解决背景技术中的问题。

2、为解决上述技术问题,本发明提供了一种基于理查森外推法的数字微分器及其优化结构,包括第一d触发器~第八d触发器、第一加法器~第六加法器、第一移位寄存器~第三移位寄存器以及第一乘法器~第三乘法器;

3、第一d触发器~第八d触发器依次串联;

4、第一加法器的负输入端接第一d触发器的输入端,正输入端接第八d触发器的输出端;第二加法器的负输入端接在第二d触发器的输出端和第三d触发器的输入端之间,正输入端接在第六d触发器的输出端和第七d触发器的输入端之间;第三加法器的负入端接在第三d触发器的输出端和第四d触发器的输入端之间,正输入端接在第五d触发器的输出端和第六d触发器的输入端之间;

5、第一加法器的输出端接第四加法器的第一正输入端,第三加法器的输出端通过第一移位寄存器与第五加法器的第二正输入端相连;第五加法器的第一正输入端通过第二移位寄存器与第四加法器的第二正输入端相连;第二加法器的输出端接在第五加法器的第一正输入端和第二移位寄存器之间;

6、第四加法器的输出端接第一乘法器的输入端,第五加法器的输出端接第二乘法器的输入端;第一乘法器的输出端通过第三移位寄存器与第六加法器的正输入端相连,第二乘法器的输出端接第六加法器的负输入端;

7、第六加法器的输出端连接第三乘法器,第三乘法器输出微分值。

8、在一种实施方式中,所述第一移位寄存器和所述第二移位寄存器均是实现左移3位的寄存器,所述第三移位寄存器是实现左移4位的寄存器。

9、在一种实施方式中,所述第一乘法器和所述第二乘法器均是系数为1/12的乘法器,所述第三乘法器是系数为1/15的乘法器。

10、在一种实施方式中,所述基于理查森外推法的数字微分器拆分成两部分,分别表示用采样间隔为和的基于5点公式的拉格朗日插值多项式的一阶微分值:

11、利用不同步长的一阶中心差分公式表达式,通过消元得到二阶中心差分公式:

12、

13、将利用泰勒级数展开得到:

14、

15、将泰勒级数展开式带入,计算利用理查森外推法得出的微分值与实际微分值之间的差值:

16、从中看出用一次理查森外推法能将截断误差精度从提升到。

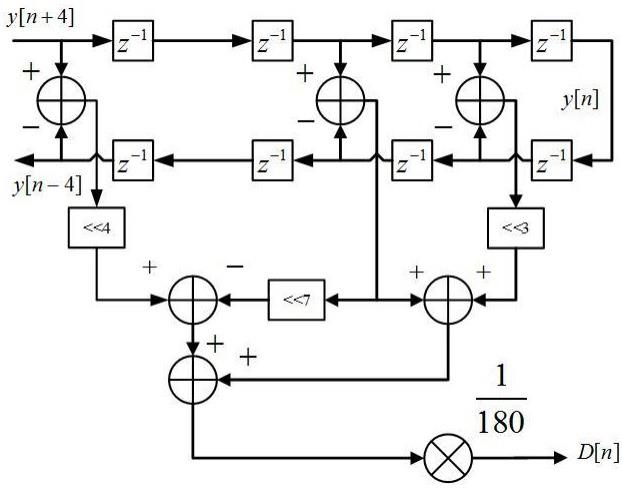

17、本发明还提供了一种基于理查森外推法的数字微分器的优化结构,包括第一d触发器~第八d触发器、第一加法器~第六加法器、第一移位寄存器~第三移位寄存器以及乘法器;

18、第一d触发器~第八d触发器依次串联;

19、第一加法器的正输入端接第一d触发器的输入端,负输入端接第八d触发器的输出端;第二加法器的正输入端接在第二d触发器的输出端和第三d触发器的输入端之间,负输入端接在第六d触发器的输出端和第七d触发器的输入端之间;第三加法器的正输入端接在第三d触发器的输出端和第四d触发器的输入端之间,负输入端接在第五d触发器的输出端和第六d触发器的输入端之间;

20、第一加法器的输出端通过第一移位寄存器与第四加法器的正输入端相连,第三加法器的输出端通过第二移位寄存器与第五加法器的第二正输入端相连,第五加法器的第一正输入端通过第三移位寄存器与第四加法器的负输入端相连;第二加法器的输出端接在第五加法器的第一正输入端和第三移位寄存器之间;第四加法器的输出端和第五加法器的输出端分别连接第六加法器的两个正输入端;第六加法器的输出端连接乘法器,乘法器输出微分值。

21、在一种实施方式中,所述第一移位寄存器是实现左移4位的寄存器,所述第二移位寄存器是实现左移3位的寄存器,所述第三移位寄存器是实现左移7位的寄存器。

22、在一种实施方式中,所述乘法器是系数为1/180的乘法器。

23、本发明提供的一种基于理查森外推法的数字微分器及其优化结构,具有以下有益效果:

24、(1)主要使用理查森外推法优化微分公式实现设计微分器电路,与传统的微分器相比实现了更高的精度要求;

25、(2)进一步完善了由基础公式推导得出的电路结构,减少微分器消耗的硬件面积,拟提出两种结构的微分器设计电路,实现的微分输出效果明显好于传统电路结构的效果;

26、(3)该电路主要运用在数字信号处理相关领域,其中针对时间交织型模数转换器的补偿架构应用较为广泛。

技术特征:

1.一种基于理查森外推法的数字微分器,其特征在于,包括第一d触发器~第八d触发器、第一加法器~第六加法器、第一移位寄存器~第三移位寄存器以及第一乘法器~第三乘法器;

2.如权利要求1所述的基于理查森外推法的数字微分器,其特征在于,所述第一移位寄存器和所述第二移位寄存器均是实现左移3位的寄存器,所述第三移位寄存器是实现左移4位的寄存器。

3.如权利要求1所述的基于理查森外推法的数字微分器,其特征在于,所述第一乘法器和所述第二乘法器均是系数为1/12的乘法器,所述第三乘法器是系数为1/15的乘法器。

4.如权利要求1所述的基于理查森外推法的数字微分器,其特征在于,所述基于理查森外推法的数字微分器拆分成两部分,分别表示用采样间隔为和的基于5点公式的拉格朗日插值多项式的一阶微分值:

5.一种基于理查森外推法的数字微分器的优化结构,其特征在于,包括第一d触发器~第八d触发器、第一加法器~第六加法器、第一移位寄存器~第三移位寄存器以及乘法器;

6.如权利要求5所述的基于理查森外推法的数字微分器的优化结构,其特征在于,所述第一移位寄存器是实现左移4位的寄存器,所述第二移位寄存器是实现左移3位的寄存器,所述第三移位寄存器是实现左移7位的寄存器。

7.如权利要求5所述的基于理查森外推法的数字微分器的优化结构,其特征在于,所述乘法器是系数为1/180的乘法器。

技术总结

本发明公开一种基于理查森外推法的数字微分器及其优化结构,属于数字信号处理领域,包括第一D触发器~第八D触发器、第一加法器~第六加法器、第一移位寄存器~第三移位寄存器以及第一乘法器~第三乘法器。本发明针对传统的五点数值微分公式来实现微分器提出改进,能实现更宽的有效频带以及更高的精度输出;另外针对外推出的求导公式进一步优化,运用移位寄存器和少量加法代替乘法器,从而减少硬件消耗。本发明大量减少微分器所需要的面积,只需要用到一个乘法器和三个移位寄存器以及少量加法器即可,有更少的硬件优化空间。在关键路径变短以后,在综合实现时时钟频率能做的更高,针对高速电路有更大的优势。

技术研发人员:吴旭凡

受保护的技术使用者:上海芯炽科技集团有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!