校正设计布局的方法、计算装置及制造半导体器件的方法与流程

本公开涉及一种校正半导体器件的设计布局的方法、一种执行该方法的计算装置、以及一种使用该计算装置来制造半导体器件的方法。

背景技术:

1、在设计集成电路时,可以产生电路的设计布局以在半导体基板上形成期望的电路,并且可以通过掩模(mask)将电路的设计布局转移到晶片(wafer)表面。随着半导体器件的集成度变得更高,电路设计会变得更复杂。如果在根据设计布局制造的半导体器件中发生错位(misalignment),则两个错位图案之间的间隙可以很窄,以致围绕两个图案的绝缘膜可能被破坏,或者在另一方面造成性能下降。

技术实现思路

1、为了校正设计布局中的错位,一些示例实施例可以提供一种校正半导体器件的设计布局的方法、一种执行该方法的计算装置、以及一种使用该计算装置来制造半导体器件的方法。

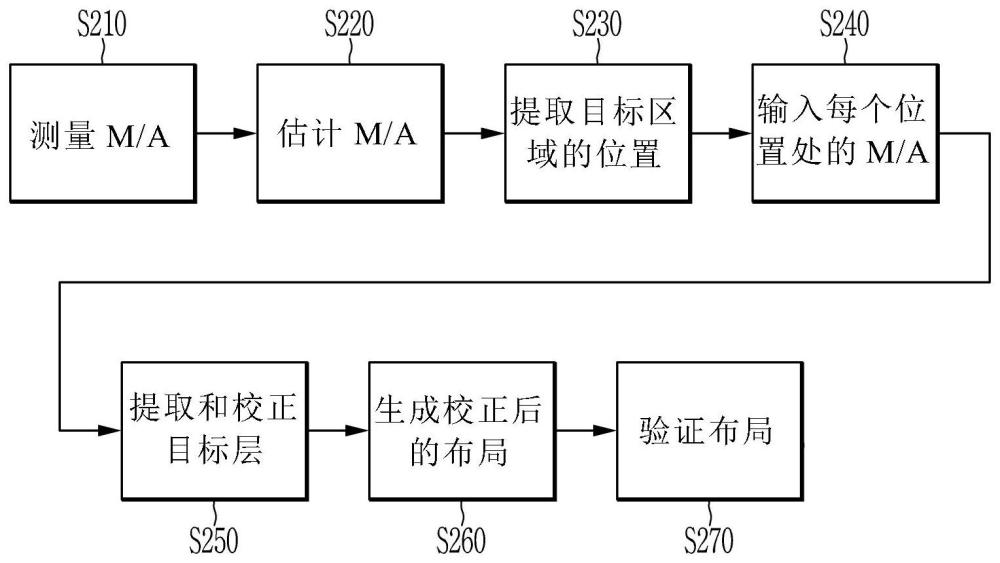

2、根据一些示例实施例,发明构思可以提供一种由计算装置执行的校正半导体器件的设计布局的方法。所述方法可以包括:从原始设计布局中分离出包括多个目标图案的第一目标层;通过基于所述第一目标层中的所述多个目标图案的相应位置处的错位值将所述多个目标图案移位,来生成第二目标层;以及将所述第二目标层与从中分离出所述第一目标层的所述原始设计布局组合,以生成校正后的设计布局。

3、根据一些示例实施例,发明构思可以提供一种计算装置,所述计算装置可以包括:存储器,所述存储器被配置为存储一个或更多个指令;以及一个或更多个处理器,所述一个或更多个处理器被配置为运行所述一个或更多个指令。所述一个或更多个处理器可以通过运行所述一个或更多个指令被配置为:从半导体器件的设计布局中分离出包括多个目标图案的目标层,基于所述目标层中的所述多个目标图案处的错位值将所述多个目标图案移位,并且将所述多个目标图案被移位的所述目标层与从中分离出所述目标层的所述设计布局组合,以生成校正后的设计布局。

4、根据一些示例实施例,发明构思可以提供一种制造半导体器件的方法。所述方法可以包括:加载原始设计布局;从所述原始设计布局中分离出包括多个目标图案的目标层;基于错位值将所述目标层中的所述多个目标图案移位;将所述多个目标图案被移位的所述目标层与从中分离出所述目标层的所述原始设计布局组合,以生成校正后的设计布局;基于所述校正后的设计布局制造掩模;以及基于所述掩模制造半导体器件。

技术特征:

1.一种由计算装置执行的校正半导体器件的设计布局的方法,所述方法包括:

2.根据权利要求1所述的方法,其中,分离出所述第一目标层包括:利用所述第一目标层生成第一半导体单元,并且

3.根据权利要求2所述的方法,其中,生成所述校正后的设计布局包括:将所述第二半导体单元设置在从中分离出所述第一目标层的所述原始设计布局的顶部单元中。

4.根据权利要求1所述的方法,其中,生成所述第二目标层包括:通过将所述多个目标图案在抵消错位的方向上移位校正值,来生成所述第二目标层,所述校正值是基于所述多个目标图案的所述相应位置处的所述错位值而确定的。

5.根据权利要求4所述的方法,所述方法还包括:

6.根据权利要求4所述的方法,所述方法还包括:

7.根据权利要求1所述的方法,所述方法还包括:

8.根据权利要求7所述的方法,其中,所述晶片是利用应用了所述原始设计布局的掩模流片的晶片。

9.根据权利要求7所述的方法,其中,所述晶片是与所述原始设计布局同代的产品的晶片。

10.根据权利要求7所述的方法,其中,获得所述错位值包括:

11.根据权利要求10所述的方法,其中,所述半导体器件包括存储器件,

12.根据权利要求10所述的方法,其中,估计所述其余区域中的错位值包括:

13.根据权利要求12所述的方法,其中,基于所述插值模型估计所述其余区域中的错位值包括:

14.根据权利要求1所述的方法,其中,所述半导体器件包括存储器件,并且

15.根据权利要求1所述的方法,所述方法还包括:

16.根据权利要求1所述的方法,所述方法还包括:

17.一种计算装置,所述计算装置包括:

18.根据权利要求17所述的计算装置,其中,所述一个或更多个处理器还被配置为:

19.根据权利要求17所述的计算装置,其中,所述一个或更多个处理器还被配置为:

20.一种制造半导体器件的方法,所述方法包括:

技术总结

提供了校正设计布局方法、计算装置及制造半导体器件的方法。所述计算装置从原始设计布局中分离出包括多个目标图案的第一目标层;基于所述第一目标层中的所述多个目标图案的位置处的错位值将所述多个目标图案移位,以生成第二目标层;以及将所述第二目标层与从中分离出所述第一目标层的所述原始设计布局组合,以生成校正后的设计布局。

技术研发人员:沈智昌,权五勋,权赫准,元福渊

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/6/18

- 还没有人留言评论。精彩留言会获得点赞!