内存装置、基于AMBA总线的SOC系统及其控制方法与流程

本发明涉及soc系统控制领域,特别是涉及一种内存装置、基于amba总线的soc系统及其控制方法。

背景技术:

1、由于内存读取速度的限制,内存速度与cpu速度的不匹配成为限制基于amba总线的soc系统性能的瓶颈。目前大多是采用加入cache来解决这一问题。但是cache替换算法的好坏以及cacheram的大小直接决定着命中率的高低,而且比较复杂。

技术实现思路

1、本发明的目的是提供一种内存装置、基于amba总线的soc系统及其控制方法,内存装置应用于基于amba总线的soc系统,通过设置多个内存模块即可提高基于amba总线的soc系统的cpu主频,进而优化soc系统的性能。

2、为实现上述目的,本发明提供了如下方案:

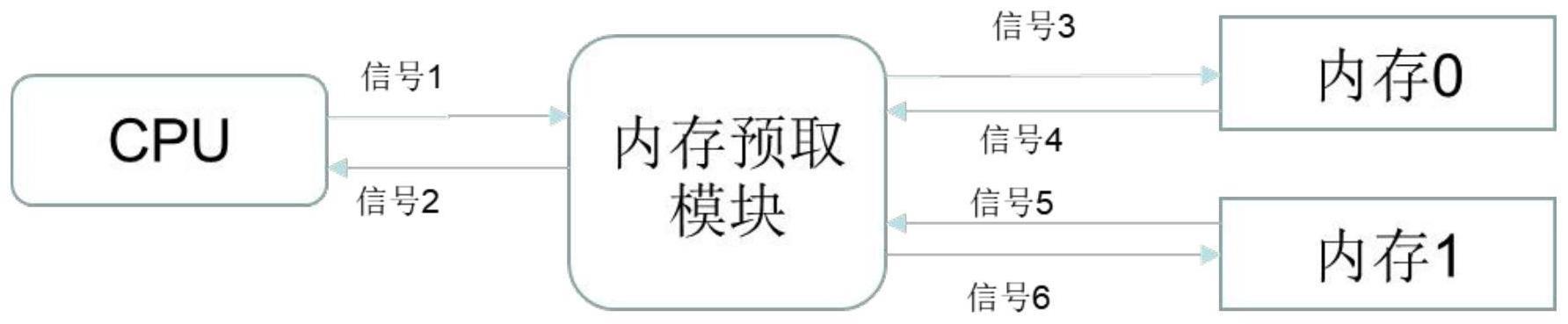

3、一种内存装置,所述内存装置应用于基于amba总线的soc系统,所述内存装置包括:

4、内存预取模块和多内存部;

5、所述内存预取模块分别与所述多内存部和基于amba总线的soc系统中的cpu连接;

6、所述内存预取模块用于获取第一信号,并保存第一信号的地址,根据所述第一信号不同时钟周期生成多个二级请求信号组,同时根据第一信号的地址和多个所述二级请求信号组调取多内存部中的数据并将调取的数据发送至所述cpu;所述时钟周期和所述二级请求信号组一一对应。

7、可选的,所述多内存部包括多个内存模块。

8、可选的,所述二级请求信号组包括多个二级请求信号;所述二级请求信号与所述多内存部中的内存模块一一对应。

9、可选的,所述多内存部包括第一内存模块和第二内存模块。

10、可选的,所述内存预取模块内设置有请求信号地址寄存器、第一内存信号地址寄存器、第二内存信号地址寄存器和控制器;

11、所述控制器分别与所述cpu、所述第一内存模块、所述第二内存模块、所述请求信号地址寄存器、所述第一内存信号地址寄存器和所述第二内存信号地址寄存器连接;

12、所述控制器用于获取所述第一信号并将所述第一信号的地址存储至所述请求信号地址寄存器;

13、所述控制器用于获取所述第一信号生成二级请求信号组;所述二级请求信号组包括第一二级请求信号和第二二级请求信号;

14、所述控制器用于将第一返回信号的地址存储至所述第一内存信号地址寄存器;第一返回信号为第一内存模块根据第一二级请求信号输出的数据;

15、所述控制器用于将第二返回信号的地址存储至所述第二内存信号地址寄存器;第二返回信号为第二内存模块根据第二二级请求信号输出的数据;

16、所述控制器用于接收实际请求信号,并根据实际请求信号调取多内存部中的数据发送至所述cpu。

17、一种基于amba总线的soc系统,所述soc系统应用所述的一种内存装置。

18、一种基于amba总线的soc系统的控制方法,所述控制方法应用于所述的一种基于amba总线的soc系统,所述控制方法包括:

19、用于获取第一信号和第一信号的地址;

20、根据所述第一信号不同时钟周期生成多个二级请求信号组,根据第一信号的地址和多个所述二级请求信号组调取多内存部中的数据并将调取的数据发送至所述cpu;所述时钟周期和所述二级请求信号组一一对应。

21、可选的,根据所述第一信号不同时钟周期生成多个二级请求信号组,根据第一信号的地址和多个所述二级请求信号组调取多内存部中的数据并将调取的数据发送至所述cpu,包括:

22、令时钟周期数i=1;

23、令第i+1个时钟周期内返回数据有效标志位为0;

24、根据第i个时钟周期内第一信号生成第i个时钟周期内第一二级请求信号和第i个时钟周期内第二二级请求信号;将第i个时钟周期内第一信号的地址存储到请求信号地址寄存器;

25、将第i个时钟周期内第一二级请求信号的地址存储至第一内存信号地址寄存器;第i+2个时钟周期内第一返回信号为第一内存模块根据第i个时钟周期内第一二级请求信号输出的数据;

26、将第i个时钟周期内第二二级请求信号的地址存储至第二内存信号地址寄存器;第i+2个时钟周期内第二返回信号为第二内存模块根据第i个时钟周期内第二二级请求信号输出的数据;

27、将第i+2个时钟周期内返回数据有效标志位的数值更新为1,判断所述第i个时钟周期内第一信号的地址和第i+2个时钟周期内第一返回信号的地址是否相等,得到第一判断结果;

28、若得到第一判断结果为是,则确定第一返回信号为实际请求数据,将第一返回信号发送至所述cpu,并令第i+2个时钟周期内第一返回信号的地址增加1,同时向第一内存单元发出二级请求信号;令i=i+1,将第i个时钟周期内第一信号地址存储到请求信号地址寄存器,返回步骤“将第i+2个时钟周期内返回数据有效标志位的数值更新为1,判断所述第i个时钟周期内第一信号的地址和第i+2个时钟周期内第一返回信号的地址是否相等,得到第一判断结果”;

29、若得到第一判断结果为否,则判断所述第i个时钟周期内第一信号的地址和第i+2个时钟周期内第二返回信号的地址是否相等,得到第二判断结果;

30、若得到第二判断结果为是,则确定第二返回信号为实际请求数据,并将第二返回信号发送至所述cpu,并令第i+2个时钟周期内第二返回信号的地址增加1,同时向第二内存单元发出二级请求信号;令i=i+1,返回步骤“将第i+2个时钟周期内返回数据有效标志位的数值更新为1,判断所述第i个时钟周期内第一信号的地址和第i+2个时钟周期内第一返回信号的地址是否相等,得到第一判断结果”;

31、若得到第二判断结果为否,则返回步骤“令时钟周期数i=1”。

32、可选的,所述第一返回信号的地址和所述第二返回信号的地址的均为二进制数;所述有效标志位为0或1。

33、根据本发明提供的具体实施例,本发明公开了以下技术效果:

34、本发明提供的内存装置、基于amba总线的soc系统及其控制方法,通过设置包括多个内存模块的多内存部提高基于amba总线的soc系统的cpu主频,进而优化soc系统的性能。

技术特征:

1.一种内存装置,其特征在于,所述内存装置应用于基于amba总线的soc系统,所述内存装置包括:

2.根据权利要求1所述的一种内存装置,其特征在于,所述多内存部包括多个内存模块。

3.根据权利要求2所述的一种内存装置,其特征在于,所述二级请求信号组包括多个二级请求信号;所述二级请求信号与所述多内存部中的内存模块一一对应。

4.根据权利要求1所述的一种内存装置,其特征在于,所述多内存部包括第一内存模块和第二内存模块。

5.根据权利要求4所述的一种内存装置,其特征在于,所述内存预取模块内设置有请求信号地址寄存器、第一内存信号地址寄存器、第二内存信号地址寄存器和控制器;

6.一种基于amba总线的soc系统,所述soc系统应用如权利要求1-5任一项所述的一种内存装置。

7.一种基于amba总线的soc系统的控制方法,所述控制方法应用于如权利要求6所述的一种基于amba总线的soc系统,所述控制方法包括:

8.根据权利要求7所述的一种基于amba总线的soc系统的控制方法,其特征在于,根据所述第一信号不同时钟周期生成多个二级请求信号组,根据第一信号的地址和多个所述二级请求信号组调取多内存部中的数据并将调取的数据发送至所述cpu,包括:

9.根据权利要求8所述的一种基于amba总线的soc系统的控制方法,其特征在于,所述第一返回信号的地址和所述第二返回信号的地址的均为二进制数;所述有效标志位为0或1。

技术总结

本发明公开了一种内存装置、基于AMBA总线的SOC系统及其控制方法,涉及SOC系统控制领域。本发明的内存装置包括:内存预取模块和多内存部;内存预取模块分别与多内存部和基于AMBA总线的SOC系统中的CPU连接;内存预取模块用于获取第一信号,并保存第一信号的地址,根据第一信号不同时钟周期生成多个二级请求信号组,同时根据第一信号的地址和多个二级请求信号组调取多内存部中的数据并将调取的数据发送至CPU;时钟周期和二级请求信号组一一对应。本发明通过设置多个内存模块即可提高基于AMBA总线的SOC系统的CPU主频,进而优化SOC系统的性能。

技术研发人员:周亚莉,王吉健,徐红如

受保护的技术使用者:南京英锐创电子科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!