一种支持任务并行处理的芯片模拟方法、装置和芯片模拟器与流程

本说明书涉及计算机系统结构领域,尤其涉及一种支持任务并行处理的芯片模拟方法、装置和芯片模拟器以及相应的电子设备和存储介质。

背景技术:

1、随着芯片不断出现的新硬件设计,具体芯片进行指令优化后适应性地优化芯片编译器仍是研发要解决的首要问题。但是,对人工智能芯片特别是神经网络芯片而言,芯片设计大多数会倾向于输入和输出的结果对比,即对于芯片的仿真结果更为关注,但是对芯片在执行具体指令的执行流程却缺少关注。芯片模拟器着重在于指令级别的仿真。因此,如何更好地适应对芯片模拟全面性和复杂性的更高要求,克服目前芯片模拟器采用指令串行方法实现的现状,提出支持任务并行处理的芯片模拟方案,是亟待解决的技术问题。

技术实现思路

1、本说明书实施例的目的是针对上述问题,提供一种支持任务并行处理的芯片模拟方法、装置和芯片模拟器以及相应的电子设备和存储介质。

2、为解决上述技术问题,本说明书实施例是这样实现的:

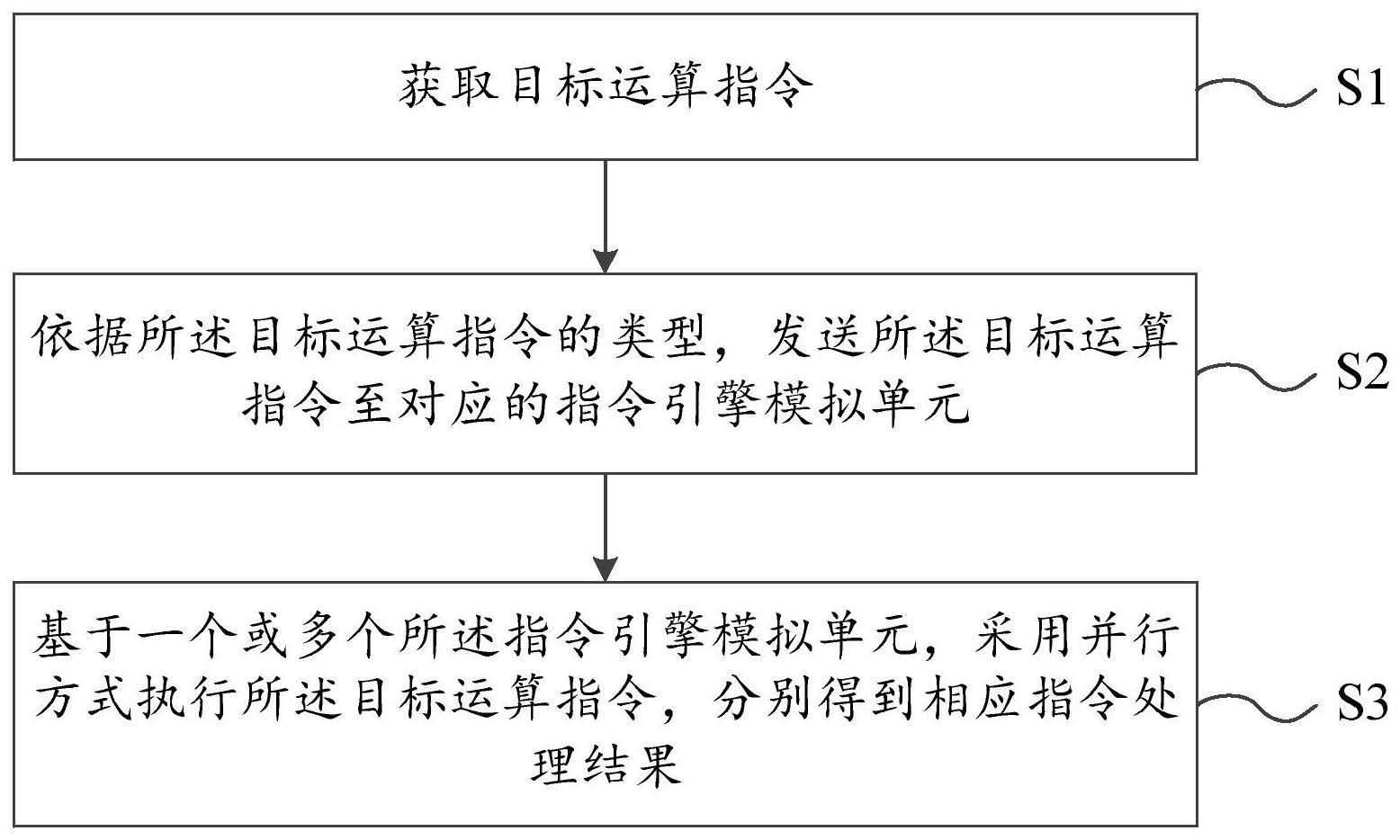

3、第一方面,提出了一种支持任务并行处理的芯片模拟方法,应用于芯片模拟器;所述方法包括:

4、获取目标运算指令;

5、依据所述目标运算指令的类型,发送所述目标运算指令至对应的指令引擎模拟单元;

6、基于一个或多个所述指令引擎模拟单元,采用并行方式执行所述目标运算指令,分别得到相应指令处理结果。

7、进一步地,所述获取目标运算指令,包括:由第一访问模拟单元依据所述目标运算指令中携带的存储地址从存储单元获取与所述目标运算指令对应的运算数据。

8、进一步地,发送所述目标运算指令,包括:由任务管理器依据所述目标运算指令的类型和所携带的数据,发送所述目标运算指令至对应的所述指令引擎模拟单元。

9、进一步地,所述目标运算指令,包括:携带神经网络运算数据的第一指令、携带非线性运算数据的第二指令以及携带矢量运算数据的第三指令。

10、进一步地,依据所述第一指令的类型和所携带的所述神经网络运算数据,发送所述第一指令至第一指令引擎模拟单元。

11、进一步地,依据所述第二指令的类型和所携带的所述非线性运算数据,发送所述第二指令至第二指令引擎模拟单元。

12、进一步地,依据所述第三指令的类型和所携带的所述矢量运算数据,发送所述第三指令至第三指令引擎模拟单元。

13、进一步地,还包括:调整一个或多个所述指令引擎模拟单元的一组或多组参数,以使所述指令引擎模拟单元能够输出对应于一组或多组所述参数的指令处理结果。

14、第二方面,提出一种支持任务并行处理的芯片模拟装置,应用于芯片模拟器;所述装置包括:

15、第一模块,能够获取目标运算指令;

16、第二模块,能够依据所述目标运算指令的类型,发送所述目标运算指令至对应的指令引擎模拟单元;

17、第三模块,能够基于一个或多个所述指令引擎模拟单元采用并行方式执行所述目标运算指令,得到相应数据处理结果。

18、进一步地,还包括:

19、第四模块,能够调整一个或多个所述指令引擎模拟单元的一组或多组参数,以使所述指令引擎模拟单元能够输出对应于一组或多组所述参数的指令处理结果。

20、第三方面,提出一种芯片模拟器,所述芯片模拟器能够执行第一方面所述的方法。

21、第四方面,提出一种芯片,所述芯片的运算指令由执行第一方面所述的方法的芯片模拟器模拟执行过程。

22、第五方面,提出了一种电子设备,包括:处理器;以及

23、被安排成存储计算机可执行指令的存储器,所述可执行指令在被执行时使得所述处理器执行第一方面所述的方法。

24、第六方面,提出了一种计算机可读存储介质,所述计算机可读存储介质存储一个或多个程序,所述一个或多个程序当被包括多个应用程序的电子设备执行时,使得所述电子设备执行第一方面所述的方法。

25、本说明书可以达到至少以下技术效果:

26、本发明方案能够模拟芯片的指令运算单元,通过采用并行执行的方式得到不同运算指令处理结果,同时可通过调整指令引擎模拟单元的不同参数,得到相应运算指令处理结果,能够有效辅助分析芯片的设计瓶颈和优化芯片编译器。

技术特征:

1.一种支持任务并行处理的芯片模拟方法,其特征在于,应用于芯片模拟器;所述方法包括:

2.根据权利要求1所述的方法,其特征在于,所述获取目标运算指令,包括:由第一存储访问单元依据所述目标运算指令中携带的存储地址从存储单元获取与所述目标运算指令对应的运算数据。

3.根据权利要求1所述的方法,其特征在于,发送所述目标运算指令,包括:由任务管理器依据所述目标运算指令的类型和所携带的数据,发送所述目标运算指令至对应的所述指令引擎模拟单元。

4.根据权利要求1至3任一项所述的方法,其特征在于,所述目标运算指令,包括:携带神经网络运算数据的第一指令、携带非线性运算数据的第二指令以及携带矢量运算数据的第三指令。

5.根据权利要求4所述的方法,其特征在于,依据所述第一指令的类型和所携带的所述神经网络运算数据,发送所述第一指令至第一指令引擎模拟单元。

6.根据权利要求4所述的方法,其特征在于,依据所述第二指令的类型和所携带的所述非线性运算数据,发送所述第二指令至第二指令引擎模拟单元。

7.根据权利要求4所述的方法,其特征在于,依据所述第三指令的类型和所携带的所述矢量运算数据,发送所述第三指令至第三指令引擎模拟单元。

8.根据权利要求1所述的方法,其特征在于,还包括:调整一个或多个所述指令引擎模拟单元的一组或多组参数,以使所述指令引擎模拟单元能够输出对应于一组或多组所述参数的指令处理结果。

9.一种支持任务并行处理的芯片模拟装置,其特征在于,应用于芯片模拟器;所述装置包括:

10.根据权利要求9所述的装置,其特征在于,还包括:

11.一种芯片模拟器,其特征在于,所述芯片模拟器能够执行权利要求1至8任一项所述的方法。

12.一种芯片,其特征在于,所述芯片的运算指令由执行权利要求1至8任一项所述的方法的芯片模拟器模拟执行过程。

13.一种电子设备,其特征在于,包括:

14.一种计算机可读存储介质,其特征在于,所述计算机可读存储介质存储一个或多个程序,所述一个或多个程序当被包括多个应用程序的电子设备执行时,使得所述电子设备执行权利要求1至8任一项所述的方法。

技术总结

本说明书实施例公开了一种支持任务并行处理的芯片模拟方法、装置和芯片模拟器;其中所述芯片模拟方法应用于芯片模拟器,包括:获取目标运算指令;依据所述目标运算指令的类型,发送所述目标运算指令至对应的指令引擎模拟单元;基于一个或多个所述指令引擎模拟单元采用并行方式执行所述目标运算指令,得到相应数据处理结果。本发明方案能够模拟芯片的指令运算单元,通过采用并行执行的方式得到不同运算指令处理结果,同时可通过调整指令引擎模拟单元的不同参数,得到对应运算指令处理结果,能够有效辅助分析芯片的设计瓶颈和优化芯片编译器。

技术研发人员:程光侠

受保护的技术使用者:九识(苏州)智能科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!