一种高空间利用率的组合型CAN控制器存储配置方法

本发明属于can控制器领域,具体涉及一种高空间利用率的组合型can控制器存储配置方法。

背景技术:

1、can总线协议(controller area network),即控制器局域网总线,是德国bosch(博世)公司研发的一种串行通讯协议总线,它可以使用双绞线来传输信号,是世界上应用最广泛的现场总线之一。can总线采用双线串行通讯协议,基于非破坏性仲裁技术、分布式实时控制、可靠的错误处理和检测机制使can总线有很高的安全性。can总线具有通信速率高、可靠性高、连接方便和性价比高等诸多特点。

2、目前通用mcu(microcontroller unit,微控制单元)支持can总线协议的方式主要分为组合型can总线控制器和外挂独立的can控制器两种。其中外挂型can控制器由于使用独立的sram(static random-access memory,静态随机存取存储器)存储单元,且一般空间较大、功能丰富,无需担心多模块对sram使用的竞争风险。而组合型can总线控制器一般用于mcu,为减少存储器的设计,往往存在多个外设共用一个sram的情况。如在工业控制中使用极为广泛的stm32系列中,usb模块和can模块就采用了共用一组1mb的sram存储单元的设计,而这种设计导致了在实际使用中usb模块和can模块存在仅能开启一个的限制,从而降低了can模块的适用性。

3、同时,为了适应更加多变的工程应用场景,can模块在设计中往往采用了预设可容纳大量识别码寄存器和输入输出寄存器的设计,这种设计方案进一步加大了对sram的容量需求。而在实际使用中,根据使用需求的变化及工程网络大小的区别,常常并不需要那么多的识别码,或者并不需要大量的输入输出存储区。由于识别码数量和输入输出存储区数量是在芯片前端设计时便已预先确定的,无法根据实际工程使用需要在后期进行修改,所以往往会出现大量存储区闲置的问题。

4、以常见的stm32系列芯片为例,该款芯片的can模块和usb模块共用了一块sram芯片,具有14组过滤器,每个过滤器占用两组32位寄存器,3组输出fifo,每个输出fifo使用四个32位寄存器,两组深度为3的输入fifo,即六个输入fifo,每个输入fifo使用四个32位寄存器,总计占用512kb存储空间。但是,由于其采用can和usb共用一块sram的模式,因此两个外设只能同时开启一个,两者无法同时收发信息。当需要使用can模块时,需提前关闭usb模块;当需要使用usb模块时,需提前关闭can模块。同时由于采用固定地址设计,过滤器数量及输入输出fifo数量均无法根据工程实际应用变化而更改。

技术实现思路

1、为了解决现有技术中存在的上述问题,本发明提供了一种高空间利用率的组合型can控制器存储配置方法。本发明要解决的技术问题通过以下技术方案实现:

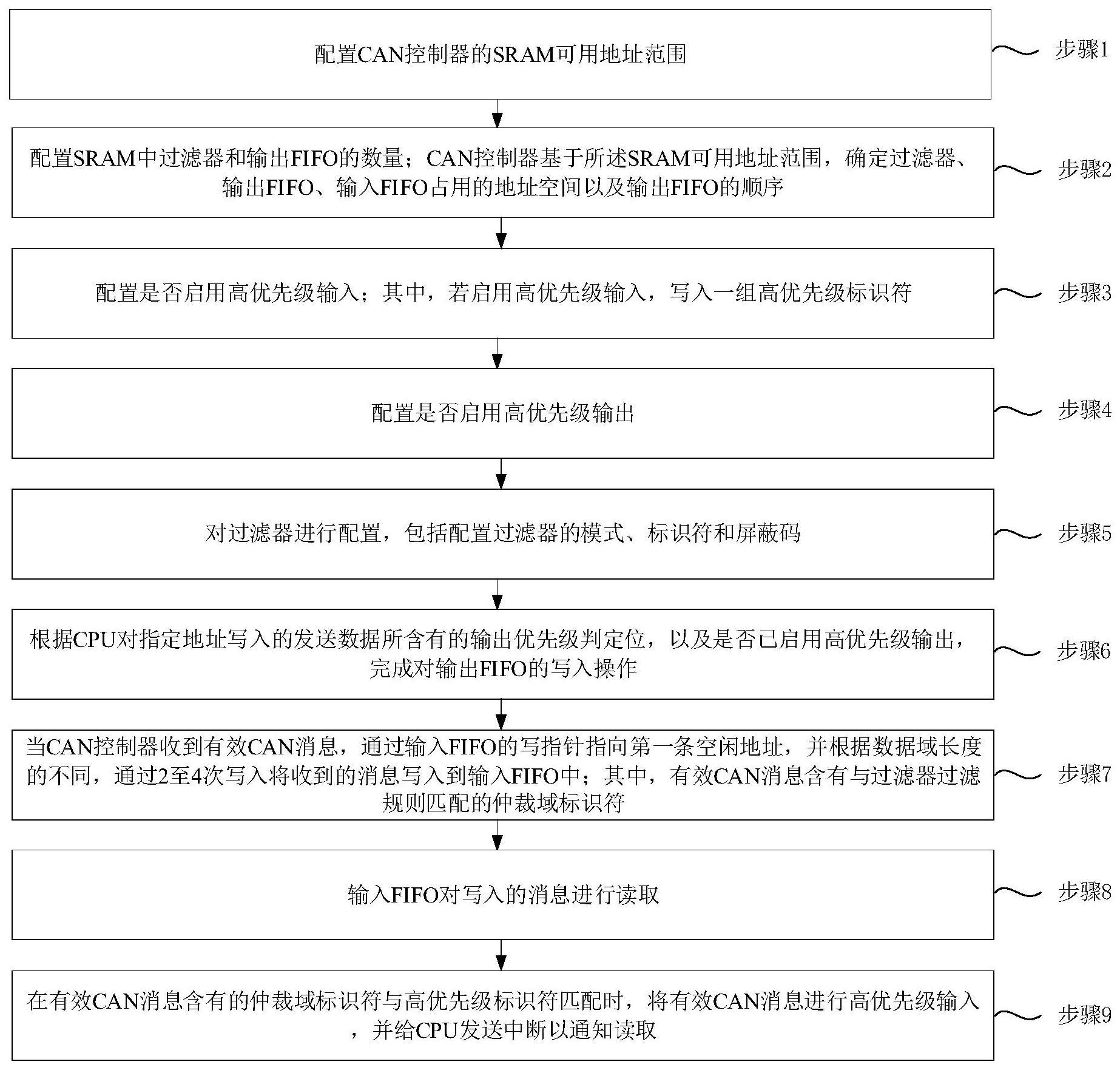

2、一种高空间利用率的组合型can控制器存储配置方法,包括受初始化信号触发的初始化阶段,以及初始化完成后的正常工作阶段,所述初始化阶段包括步骤1至步骤5,所述正常工作阶段包括步骤6至步骤9,各步骤包括:

3、步骤1:配置can控制器的sram可用地址范围;

4、步骤2:配置sram中过滤器和输出fifo的数量;所述can控制器基于所述sram可用地址范围,确定过滤器、输出fifo、输入fifo占用的地址空间以及输出fifo的顺序;

5、步骤3:配置是否启用高优先级输入;其中,若启用高优先级输入,写入一组高优先级标识符;

6、步骤4:配置是否启用高优先级输出;

7、步骤5:对过滤器进行配置,包括配置过滤器的模式、标识符和屏蔽码;

8、步骤6:根据cpu对指定地址写入的发送数据所含有的输出优先级判定位,以及是否已启用高优先级输出,完成对输出fifo的写入操作;

9、步骤7:当所述can控制器收到有效can消息,通过输入fifo的写指针指向第一条空闲地址,并根据数据域长度的不同,通过2至4次写入将收到的消息写入到输入fifo中;其中,所述有效can消息含有与过滤器过滤规则匹配的仲裁域标识符;

10、步骤8:输入fifo对写入的消息进行读取;

11、步骤9:在所述有效can消息含有的仲裁域标识符与所述高优先级标识符匹配时,将所述有效can消息进行高优先级输入,并给cpu发送中断以通知读取。

12、在本发明的一个实施例中,步骤1,包括:

13、针对定制的sram控制器,所述can控制器的地址寄存器根据写入的起始地址和终止地址,配置所述can控制器的sram可用地址范围,并利用所述定制的sram控制器将所述sram可用地址范围锁定为所述can控制器专属使用;

14、其中,所述定制的sram控制器包括apb总线和can控制器专用总线两组总线,两组总线对存储区域互斥使用。

15、在本发明的一个实施例中,利用所述定制的sram控制器将所述sram可用地址范围锁定为所述can控制器专属使用,包括:

16、所述can控制器通过两次指定格式的地址信号告知所述定制的sram控制器将所述sram可用地址范围锁定为所述can控制器的专属地址范围,数据将不被允许通过传统apb总线读写,只允许所述can控制器通过can控制器专用总线对数据进行读写。

17、在本发明的一个实施例中,步骤2,包括:

18、通过配置所述can控制器的数量寄存器,配置sram中过滤器和输出fifo的数量;

19、所述can控制器根据配置的过滤器和输出fifo的数量,自动在所述sram可用地址范围中设定过滤器和输出fifo占用的地址空间,并将各组输出fifo按占用的地址空间从前到后依次排序;

20、所述can控制器将所述sram可用地址范围中过滤器和输出fifo占用的地址空间之外的剩余地址分配为输入fifo占用的地址空间。

21、在本发明的一个实施例中,步骤2中对过滤器的配置过程,包括:

22、根据写入所述数量寄存器的数值n,确定sram中过滤器的数量为n组;并设定所述can控制器所占有的sram中前2*n个字线为过滤器存储区,包括n-1个普通过滤器和一个冻结修改过滤器,每个过滤器占用两个字线,其中n大于1。

23、在本发明的一个实施例中,步骤2中对输出fifo的配置过程,包括:

24、根据写入所述数量寄存器的数值m,确定sram中输出fifo数量为m个;并将占用的sram中所述过滤器存储区结束后的第一个字线开始的4*m个字线设定为输出fifo存储区,一个输出fifo占用四个字线;输出fifo采用先入先出模式,其中m大于1。

25、在本发明的一个实施例中,步骤3,包括:

26、当过滤器数量大于或等于4组,且输入fifo占用的地址空间大于12个字线时,通过所述can控制器的控制寄存器配置是否启用高优先级输入;

27、若选择启用高优先级输入,通过所述控制寄存器将第一组过滤器配置为高优先级过滤器,输入fifo中的前四个字线被锁定,作为一组独立的输入邮箱用做高优先级输入邮箱;第一组过滤器用于标识重要设备发送的紧急信息,并输出到所述高优先级输入邮箱以便cpu快速读取,实现高优先级插队输入;第一组过滤器至倒数第二组过滤器均只能在初始化模式下按顺序写入;最后一组过滤器为冻结修改过滤器,具备在can控制器被软件冻结状态下修改的功能;

28、若启用高优先级输入,则为高优先级过滤器写入一组高优先级识别符;

29、相应的,步骤9包括:

30、仅当所述有效can消息含有的仲裁域标识符与所述高优先级标识符匹配时,才将所述有效can消息存入高优先级输入邮箱,存入完成后通过中断立即告知cpu出现高优先级数据,并跳过普通输出fifo优先输出该组邮箱数据。

31、在本发明的一个实施例中,步骤4,包括:

32、当输出fifo的数量大于3组时,通过所述can控制器的控制寄存器配置是否启用高优先级输出;

33、若选择启用高优先级输出,则通过所述控制寄存器将第一组输出fifo配置为高优先级输出邮箱,占用四组字线,以在启用高优先级输出时对正常工作阶段需要优先输出的发送数据实现高优先级插队输出;

34、相应的,步骤6,包括:

35、当cpu写入的发送数据中的输出优先级判定位为1时,通过所述can控制器的控制寄存器将该发送数据写入该高优先级输出邮箱,写入完成后跳过普通输出fifo的输出排队,等待总线空闲时优先发送,实现高优先级插队输出。

36、在本发明的一个实施例中,步骤5,包括:

37、cpu通过apb总线对指定地址进行写入,对各组过滤器中的两个32位寄存器按顺序进行配置,其中,针对每组过滤器:

38、通过设置第一个32位寄存器的[31]位数值为0,配置该组过滤器采用的模式为标识符列表模式,则该组过滤器的两个32位寄存器所存储的均为标识符;通过设置第一个32位寄存器的[31]位数值为1,配置该组过滤器采用的模式为屏蔽码模式,则该组过滤器的第一个32位寄存器所存储的为标识符,第二个32位寄存器所存储的为屏蔽码;

39、通过设置过滤器的第一个32位寄存器的[30]位对应的ide位数值为0,配置该组过滤器记录的标识符是标准标识符,则该组过滤器的第一个32位寄存器中[28:18]位为第一组标准标识符,[10:0]位为第二组标准标识符;通过设置第一个32位寄存器的[30]位对应的ide位数值为1,配置该组过滤器记录的标识符是扩展标识符,则该组过滤器的32位寄存器中[28:18]位为标准标识符,[17:0]位为扩展标识符。

40、在本发明的一个实施例中,在所述初始化阶段中,所述can控制器中地址寄存器的配置、数量寄存器的配置和控制寄存器的配置分别进行,且各寄存器完成相应配置后被立即锁定,若需更改配置则再次对所述can控制器进行初始化。

41、本发明的有益效果:

42、本发明实施例提供了一种高空间利用率的组合型can控制器存储配置方法,对sram的存取过程中,通过修改can控制器对sram的使用模式,允许用户根据实际项目需要通过配置寄存器灵活启用存储器空间,灵活配置过滤器及输入输出fifo数量,从而降低对存储空间需求,提高sram的利用率,大幅提升可使用空间内sram的存储密度且严格限制使用的地址范围,并提供了mcu开发中can控制器与其他外设共用同一块sram的可能。且本发明配置简单,使用方便,面向工程实际,将配置的选择权交给用户。在应用中可以根据工程需要针对性调整配置的识别码数量、输入fifo数量及输出fifo数量,相比于普通can控制器,具有更广的适用性,并有效的减少了性能浪费。另外,本发明在传统先入先出fifo的模式上,加入了发送和接收的高优先级设计,避免了传统fifo必须按顺序依次读取信息可能带来的缺陷,使得报文中一些紧急信息能够快速送达。

- 还没有人留言评论。精彩留言会获得点赞!