一种MPRM逻辑电路面积和功耗优化方法、设备及介质

本发明涉及逻辑电路面积和功耗优化领域,尤其是涉及一种mprm逻辑电路面积和功耗优化方法、设备及介质。

背景技术:

1、早期的ic(integrated circuit,集成电路)设计主要集中在布尔逻辑上。事实上,数字电路也可以通过基于xnor/xor运算的reed-muller(rm)逻辑来实现,可以实现完整的逻辑功能。研究表明,数字电路采用基于rm的逻辑(如算术逻辑电路、奇偶校验电路等)比传统的布尔逻辑在功耗、面积、速度和可测试性方面更具优势。rm逻辑函数按变量取值形式可分为固定极性rm(fixed-polarity reed-muller,fprm)表达式和混合极性rm(mixed-polarity reed-muller,mprm)表达式。极性决定了mprm逻辑电路的表示,进而影响电路的功率和面积。对于一个有n个输入变量的逻辑函数,有3n个混合极性和2n个固定极性,分别对应3n个混合极性表达式和2n个固定极性表达式,所有固定极性表达式都包含在混合极性表达式中。因此,mprm逻辑电路比fprm逻辑电路具有更大的优化空间,但相应的优化过程也更为复杂。随着集成电路技术的发展和电路规模的不断增大,集成电路优化设计已从早期的单目标电路性能优化转变为多目标电路性能综合优化。因此,面积和功耗已经成为阻碍大规模以及超大规模集成电路发展的重要因素之一。

2、现有mprm逻辑电路面积和功耗优化方法大多基于加权系数法、非支配排序遗传算法和多目标粒子群算法等传统智能优化算法,基于加权系数法的搜索方法虽然比较直观,但权系数的设置较为敏感,并且需要多次运行以搜索到帕累托(pareto)非支配集合;基于非支配排序遗传算法的多目标优化方法虽然具有鲁棒性高、扩展性好等特点,但是种群多样性不高,收敛速度慢并且易陷入局部最优;基于多目标粒子群算法的多目标优化方法用于小规模电路表现较好,对于输入变量增多的大规模电路缺乏测试。此外,由于需要另外考虑参数的权重值以及粒子的边界处理,导致该算法鲁棒性和运行效率较低。

3、由于受加权系数法、非支配排序遗传算法和多目标粒子群算法等算法自身缺陷的影响,使得基于加权系数法、非支配排序遗传算法和多目标粒子群算法的mprm逻辑电路面积和功耗优化方法存在解集质量不高、收敛速度慢、易陷入局部最优等问题,难以满足中大规模mprm逻辑电路快速、有效优化最优面积和功耗的需要。因此,对于mprm逻辑电路面积和功耗优化领域来说,研究一种能快速收敛至帕累托最优(pareto optimality)前沿的面积和功耗优化方法已迫在眉睫。

技术实现思路

1、本发明的目的就是为了提供一种提高mprm逻辑电路面积和功耗优化效果的mprm逻辑电路面积和功耗优化方法、设备及介质。

2、本发明的目的可以通过以下技术方案来实现:

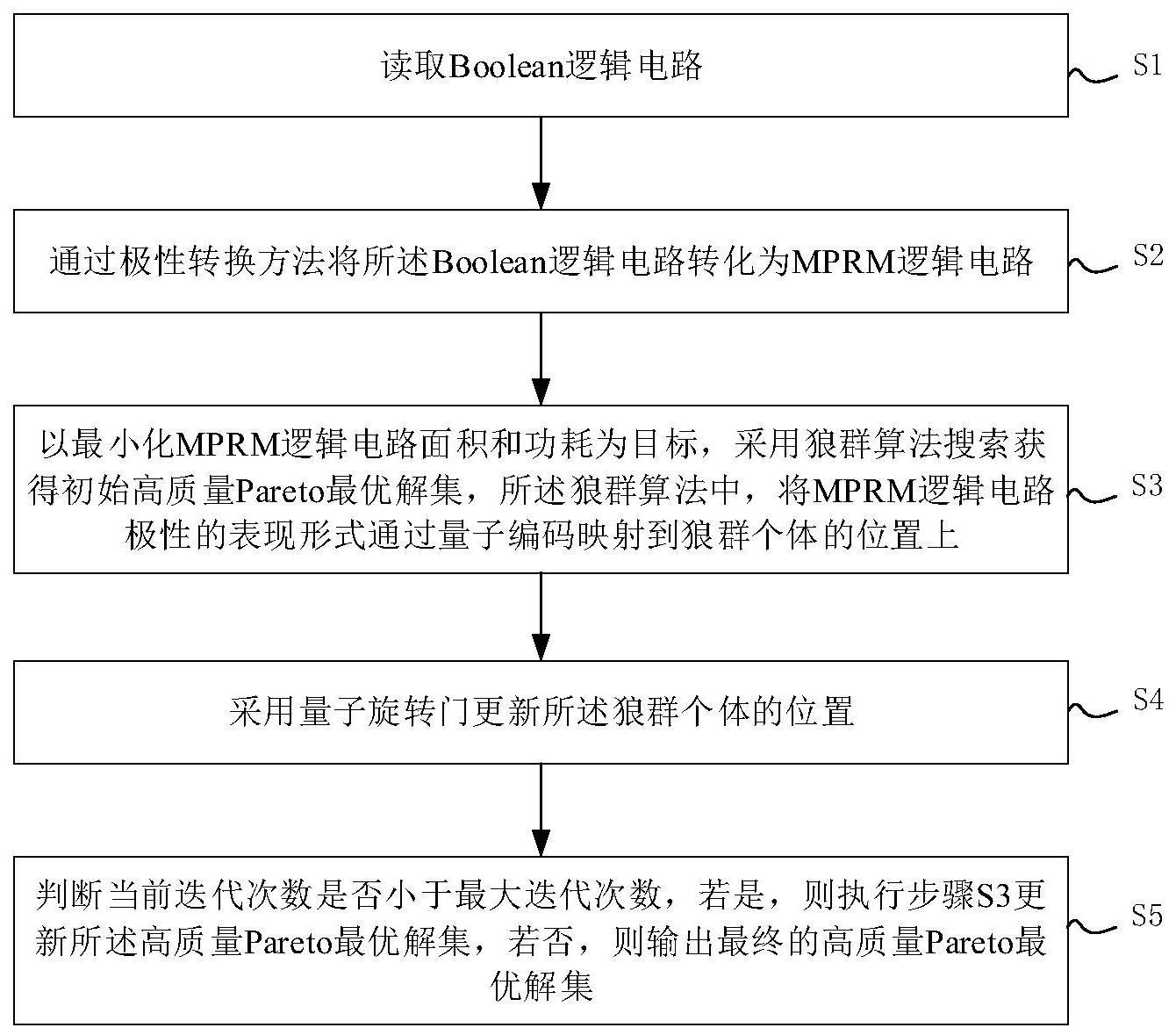

3、一种mprm逻辑电路面积和功耗优化方法,包括以下步骤:

4、s1、读取boolean逻辑电路;

5、s2、通过极性转换方法将所述boolean逻辑电路转化为mprm逻辑电路;

6、s3、以最小化mprm逻辑电路面积和功耗为目标,采用狼群算法搜索获得初始高质量pareto最优解集,所述狼群算法中,将mprm逻辑电路极性的表现形式通过量子编码映射到狼群个体的位置上;

7、s4、采用量子旋转门更新所述狼群个体的位置;

8、s5、判断当前迭代次数是否小于最大迭代次数,若是,则执行步骤s3更新所述高质量pareto最优解集,若否,则输出最终的高质量pareto最优解集。

9、进一步地,所述量子编码为二进制编码,表示为:

10、

11、其中,α和β分别表示量子比特“0”和“1”出现的概率值且满足归一化条件|α|2+|β|2=1。

12、进一步地,所述mprm逻辑电路面积和功耗最小化的表达式为:

13、

14、其中,p表示mprm电路的极性,f(p)表示该极性的适应度估算,a(p)表示该极性下的电路面积,即mprm电路中极性p的二输入门的总数;e(p)表示该极性下的电路功耗,即mprm电路中极性p的开关活动率;u表示二输入门集合;mor和mxnor分别表示二输入or门和二输入xnor门数目;lor和lxnor分别表示二输入or门和二输入xnor门的输出信号概率,li表示第i个二输入门的ei可用其输出端的信号概率,ei=2li。

15、进一步地,所述更新所述狼群个体的位置的具体步骤包括:

16、通过改变旋转角度更新所述量子旋转门;

17、基于更新后的量子旋转门计算更新后的狼群个体的位置;

18、基于所述更新后的狼群个体的位置判断狼群个体是否陷入局部最优,若是,则执行变异策略以更新狼群个体的位置,若否,则继续执行。

19、进一步地,所述旋转角度的表达式为:

20、δθij(t+1)=θij(t)+φij·(θkj(t)-θij(t))

21、其中,θij表示第i个体的第j位量子比特所对应的量子旋转门的旋转角,φij是[-1,1]之间的随机数,k≠i,t表示当前的迭代数。

22、进一步地,所述更新后的狼群个体的位置的表达式为:

23、pit=[sin(θi1(t)+δθi1(t+1)),…,sin(θid(t)+δ(θid(t+1))]

24、其中,pit表示正弦位置的解,δθ表示旋转角度。

25、进一步地,所述变异策略的表达式为:

26、

27、其中,π′t表示第t次迭代变异后的狼,πα,πβ和πδ分别代表头狼,探狼和猛狼,和分别代表在第t次迭代中每种类型狼的第γ维度;rand()表示(0,1)之间的随机数,z作为控制常数被设置为1,表示第π只狼的第γ个元素向右或向左移动d个单位。

28、进一步地,狼群个体迭代次数超过设定阈值迭代次数且狼群个体的位置没有发生改变时判定狼群个体陷入局部最优。

29、本发明还提供一种电子设备,包括:一个或多个处理器;存储器;和被存储在存储器中的一个或多个程序,所述一个或多个程序包括用于执行如上所述一种mprm逻辑电路面积和功耗优化方法的指令。

30、本发明还提供一种计算机可读存储介质,包括供电子设备的一个或多个处理器执行的一个或多个程序,所述一个或多个程序包括用于执行如上所述一种mprm逻辑电路面积和功耗优化方法的指令。

31、与现有技术相比,本发明具有以下有益效果:

32、(1)本发明通过将狼群算法与和量子理论相结合来优化mprm逻辑电路的面积和功耗,能够使mprm逻辑电路面积和功耗快速收敛至帕累托最优,提高了mprm逻辑电路面积和功耗优化的效率,改善了mprm逻辑电路面积和功耗优化的效果。

33、(2)本发明通过将个体陷入局部最优时,执行一种变异策略增强种群多样性,降低算法陷入局部最优的风险。

技术特征:

1.一种mprm逻辑电路面积和功耗优化方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的一种mprm逻辑电路面积和功耗优化方法,其特征在于,所述量子编码为二进制编码,表示为:

3.根据权利要求1所述的一种mprm逻辑电路面积和功耗优化方法,其特征在于,所述mprm逻辑电路面积和功耗最小化的表达式为:

4.根据权利要求1所述的一种mprm逻辑电路面积和功耗优化方法,其特征在于,所述更新所述狼群个体的位置的具体步骤包括:

5.根据权利要求4所述的一种mprm逻辑电路面积和功耗优化方法,其特征在于,所述旋转角度的表达式为:

6.根据权利要求4所述的一种mprm逻辑电路面积和功耗优化方法,其特征在于,所述更新后的狼群个体的位置的表达式为:

7.根据权利要求4所述的一种mprm逻辑电路面积和功耗优化方法,其特征在于,所述变异策略的表达式为:

8.根据权利要求4所述的一种mprm逻辑电路面积和功耗优化方法,其特征在于,狼群个体迭代次数超过设定阈值迭代次数且狼群个体的位置没有发生改变时判定狼群个体陷入局部最优。

9.一种电子设备,其特征在于,包括:

10.一种计算机可读存储介质,其特征在于,包括供电子设备的一个或多个处理器执行的一个或多个程序,所述一个或多个程序包括用于执行如权利要求1-8任一所述一种mprm逻辑电路面积和功耗优化方法的指令。

技术总结

本发明涉及一种MPRM逻辑电路面积和功耗优化方法,包括以下步骤:S1、读取Boolean逻辑电路;S2、通过极性转换方法将Boolean逻辑电路转化为MPRM逻辑电路;S3、以最小化MPRM逻辑电路面积和功耗为目标,采用狼群算法搜索获得初始高质量Pareto最优解集,狼群算法中,将MPRM逻辑电路极性的表现形式通过量子编码映射到狼群个体的位置上;S4、采用量子旋转门更新狼群个体的位置;S5、判断当前迭代次数是否小于最大迭代次数,若是,则执行步骤S3更新高质量Pareto最优解集,若否,则输出最终的高质量Pareto最优解集。与现有技术相比,本发明提高了MPRM逻辑电路面积和功耗优化效果。

技术研发人员:江建慧,周宇豪,张颖

受保护的技术使用者:同济大学

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!