pcie数据包的通知方法、装置及存储介质与流程

本发明涉及通信以及数据领域,具体涉及一种pcie数据包的通知方法、装置及存储介质。

背景技术:

1、pcie(peripheral component interconnect express,周边装置互连高速)为一种高速串行连接标准,用于在计算机系统内部或之间传输数据。在pcie dma传输过程时,软件预先准备好缓存,接着软件将缓存地址告诉pcie 设备,最后再通知pcie 设备启动传输。pcie设备在接收到通知信号后,根据配置的地址开始传输数据,从软件的缓存里读取数据,或将处理好的数据写到缓存中。

2、现有技术是通过写缓存来通知pcie设备来执行dma传输,需要通过总线接口的握手机制来保证寄存器(缓存)的有效性,时延大。

技术实现思路

1、本发明实施例提供了一种pcie数据包的通知方法、装置及存储介质,可以减少网络时延,提高网络流畅度。

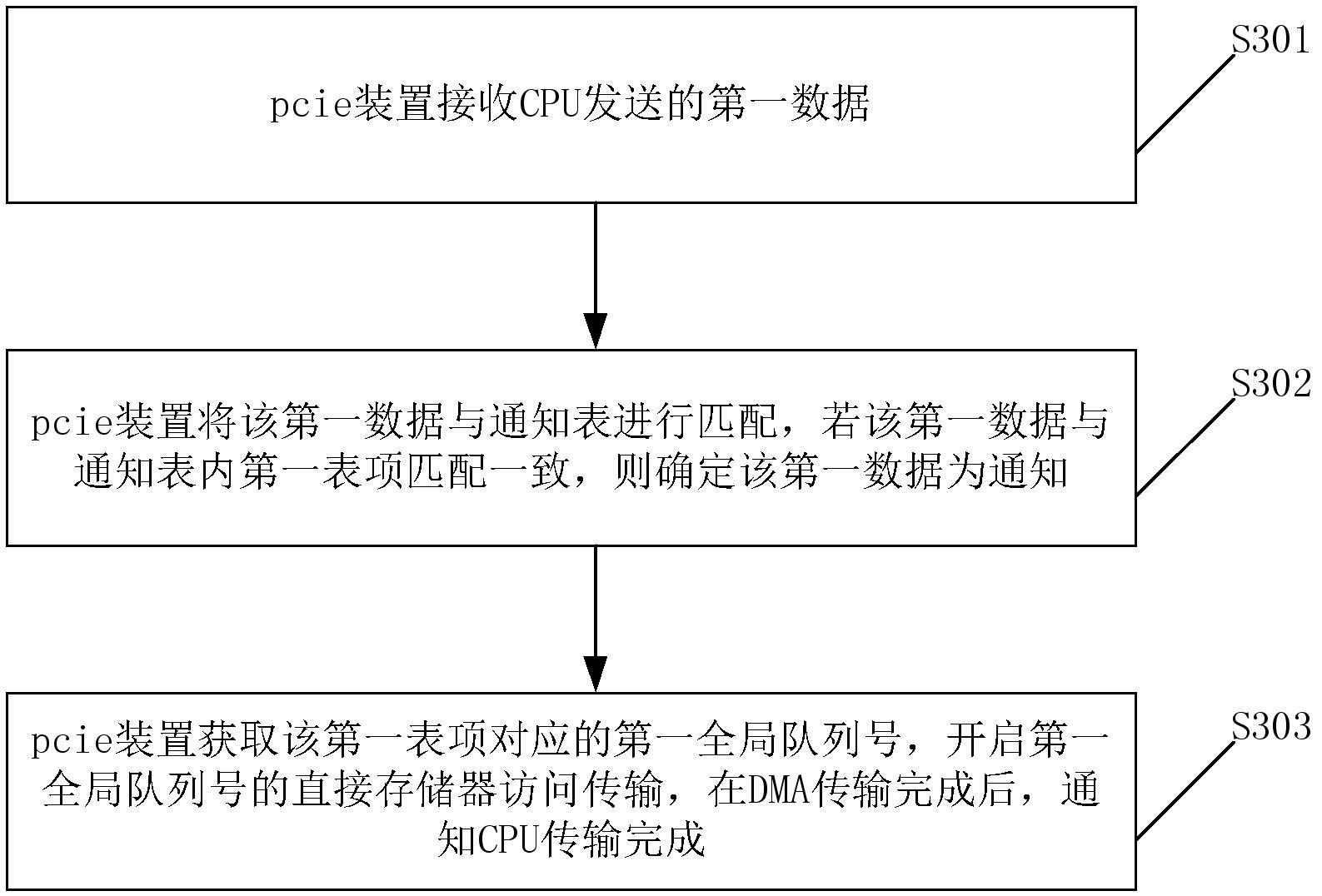

2、第一方面,本发明实施例提供一种pcie数据包的通知方法,所述方法应用于pcie装置,所述方法包括如下步骤:

3、pcie装置接收cpu发送的第一数据;

4、pcie装置将该第一数据与通知表进行匹配,若该第一数据与通知表内第一表项匹配一致,则确定该第一数据为通知notify;

5、所述通知表包括:notify下的多个表项,每个表项均包括: pcie的唯一bar空间地址和队列标识;

6、pcie装置获取该第一表项对应的第一全局队列号,开启第一全局队列号的直接存储器访问dma传输,在dma传输完成后,通知cpu传输完成

7、第二方面,提供一种pcie装置,所述装置包括:pcie终端模块和业务处理模块,所述装置还包括:通知表匹配模块;其中,

8、pcie终端模块,用于接收cpu发送的第一数据;

9、通知表匹配模块,用于将该第一数据与通知表进行匹配,若该第一数据与通知表内第一表项匹配一致,则确定该第一数据为通知notify,获取该第一表项对应的第一全局队列号;

10、所述通知表包括:notify下的多个表项,每个表项均包括: pcie的唯一bar空间地址和队列标识;

11、业务处理模块,用于开启第一全局队列号的直接存储器访问dma传输,在dma传输完成后,控制pcie终端模块通知cpu传输完成。

12、第三方面,提供一种计算机可读存储介质,其存储用于电子数据交换的程序,其中,所述程序使得终端执行第一方面提供的方法。

13、实施本发明实施例,具有如下有益效果:

14、本申请提供的技术方案的pcie装置接收cpu发送的第一数据后,将该第一数据与通知表进行匹配,若匹配一致,确定该第一数据为notify,然后直接获取对应的表项以及该表项对应的全局队列号,开启全局队列号的dma传输,在dma传输完成后,通知cpu传输完成。上述方案在获取第一全局队列号(即执行dma传输)时无需通过cpu缓存来获取,可以直接通过notify表来获取,这样就无需通过总线接口的握手机制来获取全局队列号,提高了时效性,降低了时延。

技术特征:

1.一种pcie数据包的通知方法,其特征在于,所述方法应用于pcie装置,所述方法包括如下步骤:

2.根据权利要求1所述的pcie数据包的通知方法,其特征在于,所述通知表包括:主表和备表,所述主表和备表存储的表项相同;所述方法还包括:

3.根据权利要求1所述的pcie数据包的通知方法,其特征在于,所述pcie装置将该第一数据与通知表进行匹配具体包括:

4.根据权利要求1所述的pcie数据包的通知方法,其特征在于,所述方法在第一数据与通知表进行匹配时采用多级表匹配,具体包括:

5.根据权利要求1所述的pcie数据包的通知方法,其特征在于,所述开启第一全局队列号的直接存储器访问传输具体包括:

6.一种pcie装置,所述装置包括:pcie终端模块和业务处理模块,其特征在于,所述装置还包括:通知表匹配模块;其中,

7.根据权利要求6所述的pcie装置,其特征在于,所述通知表包括:主表和备表,所述主表和备表存储的表项相同;

8.根据权利要求6所述的pcie装置,其特征在于,

9.根据权利要求6所述的pcie装置,其特征在于,

10.一种计算机可读存储介质,其存储用于电子数据交换的程序,其中,所述程序使得终端执行如权利要求1-5任意一项所述的方法。

技术总结

本申请提供一种pcie数据包的通知方法、装置及存储介质,所述方法包括:pcie装置接收CPU发送的第一数据;pcie装置将该第一数据与通知表进行匹配,若该第一数据与通知表内第一表项匹配一致,则确定该第一数据为通知;所述通知表包括:notify下的多个表项,每个表项均包括:pcie的唯一BAR空间地址和队列标识;pcie装置获取该第一表项对应的第一全局队列号,开启第一全局队列号的直接存储器访问传输,在直接存储器访问传输完成后,通知CPU传输完成。本申请提供的技术方案具有减少网络延时的优点。

技术研发人员:林恢移

受保护的技术使用者:珠海星云智联科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!