高速串行接口的自适应均衡算法的仿真验证方法及系统与流程

本申请涉及通信,具体涉及一种高速串行接口的自适应均衡算法的仿真验证方法及系统。

背景技术:

1、serdes是一种高速串行接口,serdes ip是常用的高速串行接口协议。serdes ip的自适应均衡算法是整个协议的核心单元,是由模拟器件和数字电路共同构成的,也即,serdes ip的自适应均衡算法是模数混合实现的。由于模数混合仿真需花费的时间较长,因此有必要提出一种对自适应均衡算法进行快速仿真验证的方案。

技术实现思路

1、为解决上述技术问题,本申请的实施例提供了高速串行接口的自适应均衡算法的仿真验证方法,以及提供了高速串行接口的自适应均衡算法的仿真验证系统。

2、在一示例性的实施例中,高速串行接口的自适应均衡算法的仿真验证方法包括:模拟生成高速串行总线信号,并将所述高速串行总线信号输入仿真平台,所述仿真平台用于仿真所述自适应均衡算法的模拟器件;在所述仿真平台上对所述高速串行总线信号进行仿真,得到所述高速串行总线信号对应的数字信号,以及基于所述数字信号恢复出的时钟信号;利用所述自适应均衡算法的数字逻辑,在所述时钟信号下对所述数字信号进行计算,得到输出参数,并将所述输出参数反馈至所述仿真平台,使所述仿真平台基于所述输出参数对所述接收到的高速串行总线信号进行仿真。

3、在一示例性的实施例中,所述在所述仿真平台上对所述高速串行总线信号进行仿真,包括:在所述仿真平台上建模所述自适应均衡算法的模拟器件,得到仿真电路,所述仿真电路包括依次连接的滤波器、判决反馈均衡器、模数转换器和时钟恢复单元;将所述高速串行总线信号输入所述仿真电路,得到所述模数转换器输出的所述数字信号,以及所述时钟恢复单元输出的所述时钟信号。

4、在一示例性的实施例中,所述方法还包括:获取所述滤波器的输出信号,并对所述滤波器的输出信号进行数据分析处理和/或画眼图处理。

5、在一示例性的实施例中,所述滤波器包括依次连接的衰减器、连续时间线性均衡器和电压增益放大器,以对输入的高速串行总线信号进行多层级滤波处理。

6、在一示例性的实施例中,所述判决反馈均衡器还与所述模数转换器的信号输出端连接,用于对所述模数转换器输出的数字信号的预设比特位进行最小均方运算后得到的运算结果进行数模转换后相加,得到运算结果信号,并将所述滤波器的输出信号减去所述运算结果信号后的信号输出。

7、在一示例性的实施例中,所述时钟恢复单元包括依次连接的鉴相器、数字滤波器、数模转换器和压控振荡器,所述压控振荡器的信号输出端还与所述鉴相器的信号输入端连接,用于将输出的时钟信号作为反馈信号输入至所述鉴相器。

8、在一示例性的实施例中,所述模拟生成高速串行总线信号,包括:模拟生成高速串行总线的测试码,并使所述测试码经过前馈均衡器,以得到所述测试码对应的调节信号;在所述调节信号上增加信号高速串行总线对应的信道干扰信号,以得到所述高速串行总线信号。

9、在一示例性的实施例中,所述高速串行总线信号为real型的信号。

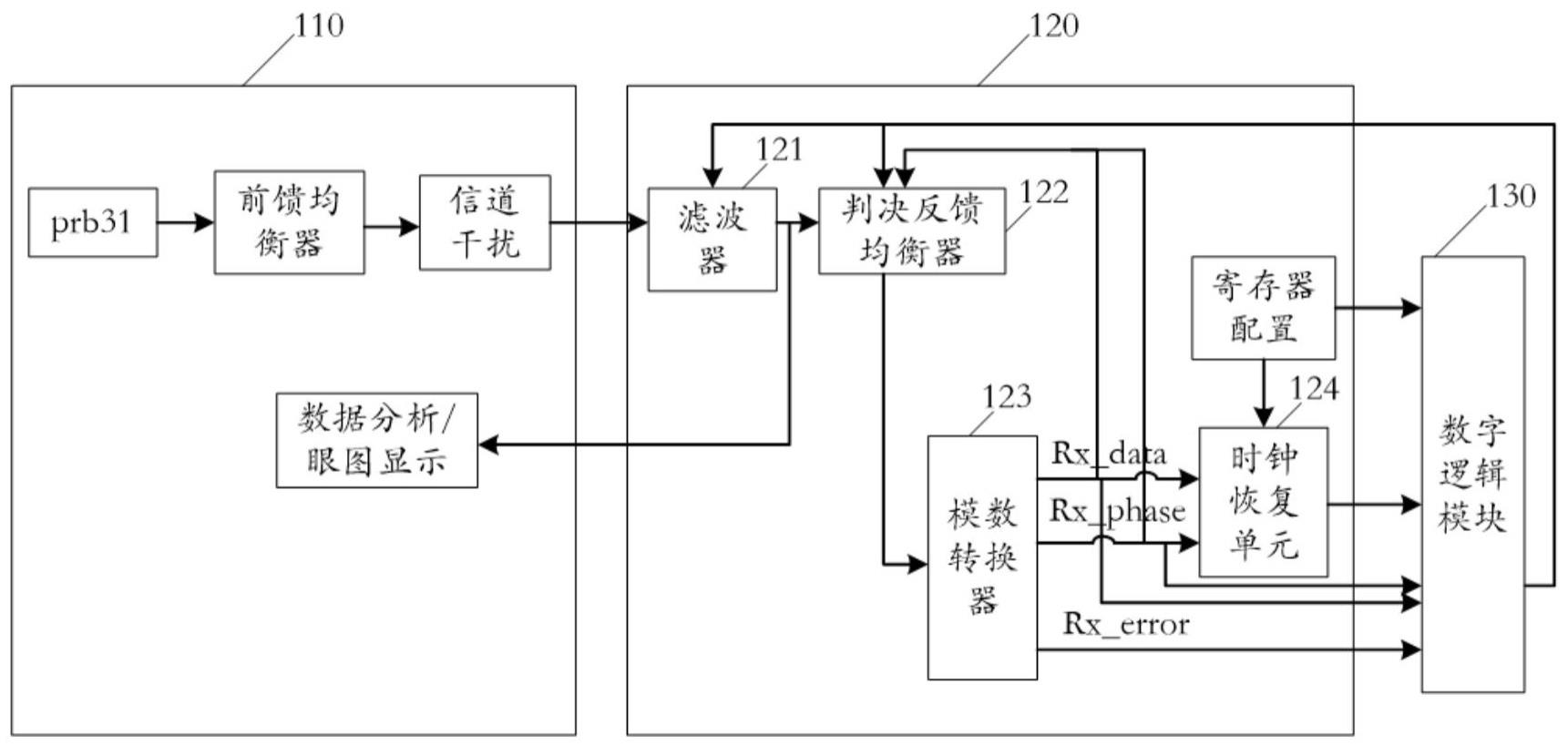

10、在一示例性的实施例中,高速串行接口的自适应均衡算法的仿真验证系统包括:数据分析程序、仿真平台和数字逻辑模块,所述仿真平台用于仿真所述自适应均衡算法的模拟器件,所述数字逻辑模块用于存放所述自适应均衡算法的数字逻辑,其中:所述数据分析程序模拟生成高速串行总线信号,并将所述高速串行总线信号输入所述仿真平台;所述仿真平台对所述高速串行总线信号进行仿真,得到所述高速串行总线信号对应的数字信号,以及基于所述数字信号恢复出的时钟信号,并将所述数字信号和所述时钟信号输出给所述数字逻辑模块;所述数字逻辑模块利用所述自适应均衡算法的数字逻辑,在所述时钟信号下对所述数字信号进行计算,得到输出参数,并将所述输出参数反馈至所述仿真平台,使所述仿真平台基于所述输出参数对所述接收到的高速串行总线信号进行仿真。

11、在一示例性的实施例中,所述仿真平台通过建模所述自适应均衡算法的模拟器件,得到仿真电路,所述仿真电路包括依次连接的滤波器、判决反馈均衡器、模数转换器和时钟恢复单元,并且所述判决反馈均衡器的信号输入端还与所述模数转换器的信号输出端连接,其中:所述滤波器根据接收到的所述数字逻辑模块的输出参数,对接收到的高速串行总线信号进行滤波处理;所述判决反馈均衡器根据接收到的所述数字逻辑模块的输出参数,和所述模数转换器输出的数字信号,对所述滤波器的输出信号进行干扰消除;所述模数转换器输出所述高速串行总线信号对应的数字信号;所述时钟恢复单元输出所述时钟信号。

12、在本申请的实施例提供的技术方案中,是将自适应均衡算法解耦为模拟器件和数字逻辑两个部分,针对模拟器件部分搭建独立的仿真平台,通过仿真平台对模拟生成的高速串行总线信号进行仿真,数字逻辑部分也作为独立模块,利用仿真平台输出的数字信号和时钟信号计算输出参数,并将输出参数反馈给仿真平台中的模拟器件。如此,通过将自适应均衡算法的模拟器件和数字逻辑解耦,能够提升自适应均衡算法的仿真验证速度;而当仿真平台中的模拟器件的输入参数发生变化后,输出信号也会相应变化,从而实现自适应均衡算法的调节过程。由此可见,本实施例提供的技术方案能够实现对于自适应均衡算法快速仿真验证。

13、应理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本申请。

技术特征:

1.一种高速串行接口的自适应均衡算法的仿真验证方法,其特征在于,所述方法包括:

2.根据权利要求1所述的方法,其特征在于,所述在所述仿真平台上对所述高速串行总线信号进行仿真,包括:

3.根据权利要求2所述的方法,其特征在于,所述方法还包括:

4.根据权利要求2所述的方法,其特征在于,所述滤波器包括依次连接的衰减器、连续时间线性均衡器和电压增益放大器,以对输入的高速串行总线信号进行多层级滤波。

5.根据权利要求2所述的方法,其特征在于,所述判决反馈均衡器还与所述模数转换器的信号输出端连接,用于对所述模数转换器输出的数字信号的预设比特位进行最小均方运算后得到的运算结果进行数模转换后相加,得到运算结果信号,并将所述滤波器的输出信号减去所述运算结果信号后的信号输出。

6.根据权利要求2所述的方法,其特征在于,所述时钟恢复单元包括依次连接的鉴相器、数字滤波器、数模转换器和压控振荡器,所述压控振荡器的信号输出端还与所述鉴相器的信号输入端连接,用于将输出的时钟信号作为反馈信号输入至所述鉴相器。

7.根据权利要求1-6任一项所述的方法,其特征在于,所述模拟生成高速串行总线信号,包括:

8.根据权利要求7所述的方法,其特征在于,所述高速串行总线信号为real型的信号。

9.一种高速串行接口的自适应均衡算法的仿真验证系统,其特征在于,所述系统包括数据分析程序、仿真平台和数字逻辑模块,所述仿真平台用于仿真所述自适应均衡算法的模拟器件,所述数字逻辑模块用于存放所述自适应均衡算法的数字逻辑,其中:

10.根据权利要求9所述的系统,其特征在于,所述仿真平台通过建模所述自适应均衡算法的模拟器件,得到仿真电路,所述仿真电路包括依次连接的滤波器、判决反馈均衡器、模数转换器和时钟恢复单元,并且所述判决反馈均衡器的信号输入端还与所述模数转换器的信号输出端连接,其中:

技术总结

本申请的实施例揭示了高速串行接口的自适应均衡算法的仿真验证方法及系统。该方法包括:模拟生成高速串行总线信号,并将所述高速串行总线信号输入仿真平台,所述仿真平台用于仿真所述自适应均衡算法的模拟器件;在所述仿真平台上对所述高速串行总线信号进行仿真,得到所述高速串行总线信号对应的数字信号,以及基于所述数字信号恢复出的时钟信号;利用所述自适应均衡算法的数字逻辑,在所述时钟信号下对所述数字信号进行计算,得到输出参数,并将所述输出参数反馈至所述仿真平台,使所述仿真平台基于所述输出参数对所述接收到的高速串行总线信号进行仿真。本申请能够实现对于自适应均衡算法快速仿真验证。

技术研发人员:李艳华

受保护的技术使用者:牛芯半导体(深圳)有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!