一种基于RISC-V架构的神经网络搜索芯片的制作方法

本发明涉及神经网络芯片,特别是涉及一种基于risc-v架构的神经网络搜索芯片。

背景技术:

1、近些年来,随着社会发展,人工智能(artificial intelligence,ai)广泛应用于云端数据中心,智能端设备和边缘端设备。同时,神经网络在各种ai任务中展现出强大的能力,包括但不限于图像识别、人脸识别、关键词检测和文本处理等场景。人工神经网络性能不断提升,包含大量参数和运算的深度神经网络得到了广泛的使用。ai在计算过程中,由于卷积、池化以及激活等操作,会产生大量的中间数据并需要大量的数据搬移,这对ai芯片的性能和功耗提出了更高的要求。

2、在传统的存算分离的冯诺依曼架构上训练神经网络时,存在诸多局限:处理器和存储器之间搬运数据的总线带宽有限;在分级的存储器结构下,远离处理器的存储级容量大,但带宽低延迟高;神经网络的计算的数据量大,并行度高,需要大量的数据搬移等。在训练时大量的时间和能量消耗在数据的搬运和存储器的读写上,算力提升需要高带宽的存储器以及新型的计算架构。并且随着电路工艺的不断进步,处理器和存储器之间的性能沟壑越来越大,系统性能主要受到存储器性能的限制。此外,冯诺依曼架构下神经网络算法中会发生频繁的数据搬移,产生的高功耗远远高于计算产生功耗,该神经网络架构下较多数据占用cpu资源带宽,使得cpu计算效率较低、功耗较高。

3、存算一体芯片提供了一种新型神经网络加速器的方法:存算一体芯片将计算操作嵌入存储单元中,消除了存储器和处理单元的边界。相较于传统冯诺依曼架构下串行处理数据,处理器和片外存储器不断增大的性能差异,导致处理器访存计算性能极大的影响了系统性能。此外存算一体芯片会对数据并行处理,在计算过程中,减少了中间数据的搬运,有着较少的片外存储访问次数,因此存算一体架构的计算效率远高于冯诺依曼计算架构的计算效率,在卷积计算和大数据处理场景中尤其明显。

4、现阶段神经网络模型层出不穷,各种模型在图像处理、机器翻译等深度学习任务都扮演着举足轻重的角色,其中模型中网络结构是一种特殊的超参数,例如transfomer、resnet等网络结构都需要能够更加精确设计才能够实现深度学习的模型性能,神经网络结构搜索(neural architecture search,nas)即代表将传统的手工网络结构设计转变为自动化设计。现阶段google等已有通过强化学习进行神经网络结构搜索,在图像分类和语言建模任务上都超越了此前手工设计的网络。

5、但目前的神经网络类型较多,依靠经验模型往往达不到理想的结果。

技术实现思路

1、为了克服现有技术的不足,本发明的目的是提供一种基于risc-v架构的神经网络搜索芯片。

2、为实现上述目的,本发明提供了如下方案:

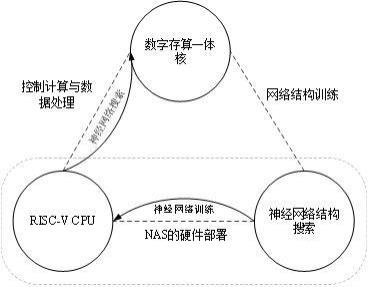

3、一种基于risc-v架构的神经网络搜索芯片,包括:

4、cpu控制器模块,与memory存储单元通信连接,用于基于上位机的resnet神经网络搜索任务,对输入数据和模型参数进行处理,得到搜索完成的神经网络结构;其中,所述cpu控制器模块使用risc-v精简指令集架构控制数据流和数据缓冲;

5、dma单元,分别与所述cpu控制器模块、memory存储单元和片上存储模块通信连接;

6、数字存算一体核模块,与所述片上存储模块通信连接,用于根据数据指令对搜索完成的神经网络结构进行训练。

7、优选的,所述根据数据指令对搜索完成的神经网络结构进行训练,包括:

8、利用任务调度器通过dma单元直接访存数据指令,并保存在片上存储模块的buffer中,利用cpu控制器模块通过机器码编译具体指令位,识别指令需求并发出控制信号,并通过数据转换将所述控制信号转换为8bit位一组数据传输给所述数字存算一体核模块,以配置数字存算一体核模块对搜索完成的神经网络结构进行训练。

9、优选的,在神经网络搜索过程中,利用流水线的方式对神经网络结构进行搜索训练。

10、优选的,所述数字存算一体核模块包括alu单元。

11、优选的,所述alu单元包括加法器、乘法器和移位累加器;在进行运算流程时,利用所述乘法器实现数据和地址的乘法运算,再利用所述加法器对乘法运算后的数据和地址进行加法运算,最后通过移位累加器对加法运算后的数据和地址进行处理得到运算结果。

12、优选的,所述片上存储模块含有多层数据缓冲区,且每一层数据缓冲区通过fifo进行缓冲。

13、优选的,所述数字存算一体核模块,通过片上总线接口与所述片上存储模块通信连接。

14、优选的,所述memory存储单元为sram存储器。

15、根据本发明提供的具体实施例,本发明公开了以下技术效果:

16、本发明提供了一种基于risc-v架构的神经网络搜索芯片,包括:cpu控制器模块,与memory存储单元通信连接,用于基于上位机的resnet神经网络搜索任务,对输入数据和模型参数进行处理,得到搜索完成的神经网络结构;其中,所述cpu控制器模块使用risc-v精简指令集架构控制数据流和数据缓冲;dma单元,分别与所述cpu控制器模块、memory存储单元和片上存储模块通信连接;数字存算一体核模块,与所述片上存储模块通信连接,用于根据数据指令对搜索完成的神经网络结构进行训练。本发明通过利用数字存算一体核与risc-v架构的cpu完成神经网络的训练和搜索,能够提升总线传输数据的调度效率,同时该架构下数字存算一体核能够充分利用算力资源实现网络推理任务,克服传统存储运算算力的限制,实现速度更快、精度更高的神经网络搜索。

技术特征:

1.一种基于risc-v架构的神经网络搜索芯片,其特征在于,包括:

2.根据权利要求1所述的基于risc-v架构的神经网络搜索芯片,其特征在于,所述根据数据指令对搜索完成的神经网络结构进行训练,包括:

3.根据权利要求1所述的基于risc-v架构的神经网络搜索芯片,其特征在于,在神经网络搜索过程中,利用流水线的方式对神经网络结构进行搜索训练。

4.根据权利要求1所述的基于risc-v架构的神经网络搜索芯片,其特征在于,所述数字存算一体核模块包括alu单元。

5.根据权利要求4所述的基于risc-v架构的神经网络搜索芯片,其特征在于,所述alu单元包括加法器、乘法器和移位累加器;在进行运算流程时,利用所述乘法器实现数据和地址的乘法运算,再利用所述加法器对乘法运算后的数据和地址进行加法运算,最后通过移位累加器对加法运算后的数据和地址进行处理得到运算结果。

6.根据权利要求1所述的基于risc-v架构的神经网络搜索芯片,其特征在于,所述片上存储模块含有多层数据缓冲区,且每一层数据缓冲区通过fifo进行缓冲。

7.根据权利要求1所述的基于risc-v架构的神经网络搜索芯片,其特征在于,所述数字存算一体核模块,通过片上总线接口与所述片上存储模块通信连接。

8.根据权利要求1所述的基于risc-v架构的神经网络搜索芯片,其特征在于,所述memory存储单元为sram存储器。

技术总结

本发明提供了一种基于RISC‑V架构的神经网络搜索芯片,属于神经网络芯片技术领域,包括:CPU控制器模块,与Memory存储单元通信连接,用于基于上位机的Resnet神经网络搜索任务,对输入数据和模型参数进行处理,得到搜索完成的神经网络结构;DMA单元,分别与CPU控制器模块、Memory单元和片上存储模块通信连接;数字存算一体核模块,用于根据数据指令对搜索完成的神经网络结构进行训练。本发明通过数字存算一体核与RISC‑V架构的CPU完成神经网络的训练和搜索,能够提升总线传输数据的调度效率,同时该架构下数字存算一体核能够充分利用算力资源实现网络推理任务,克服传统存储运算算力的限制,实现速度更快、精度更高的神经网络搜索。

技术研发人员:刘斌,袁梓涵,潘彪,康旺

受保护的技术使用者:北京京瀚禹电子工程技术有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!