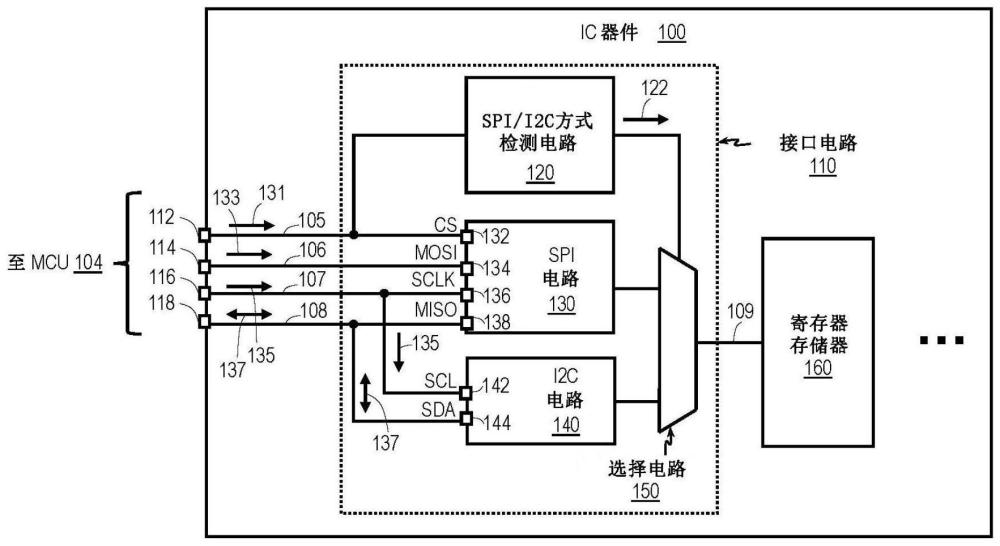

用于多协议通信接口的高效引脚共享集成电路(IC)器件的制作方法

本公开一般涉及电子器件,并且更具体地涉及用于多协议通信接口的具有高效引脚共享的集成电路(ic)器件。

背景技术:

1、串行外围接口(spi)和集成电路间接口(i2c)广泛用于集成电路(ic)设备或组件之间的通信,例如微控制器和外围设备(如传感器、模数转换器(adc)、数模转换器(dac)、存储器、光器件等)之间的通信,基于全双工主从式串行通信接口。来自spi主设备或spi从设备的数据在spi主设备提供的时钟信号的上升沿或下降沿上同步。spi主设备和spi从设备都可以同时传输数据,例如,使用包括时钟线、芯片选择(cs)线、主输入、从输出(miso)数据线和主输出、从输入(mosi)数据线的4线spi。另一方面,i2c是使用时钟线和双向数据线这两条线的基于半双工主从的串行通信接口。类似于spi,i2c主设备可以提供时钟信号,并且可以基于时钟信号的上升沿或下降沿在i2c主装置和i2c从装置之间传送数据。一些设备可以包括多协议通信接口(例如,包括spi和i2c接口),以提供与各种设备通信的灵活性。

技术实现思路

技术特征:

1.一种用于集成电路(ic)设备之间的通信的接口电路布置,所述接口电路布置包括:

2.根据权利要求1所述的接口电路布置,其中所述模式检测电路还响应于成功检测到所述信号模式而输出选择所述spi电路的指示。

3.根据权利要求1所述的接口电路布置,其中所述模式检测电路还响应于未能检测到所述信号模式而输出选择所述i2c电路的指示。

4.根据权利要求1所述的接口电路布置,其中所述模式检测电路通过确定在所述第三连接端口处接收的信号中从逻辑高电压电平到逻辑低电压电平的转变数量是否满足负电压转变的阈值数量来检测所述信号模式。

5.根据权利要求4所述的接口电路布置,其中用于检测所述信号模式的负电压转变的阈值数量是预定值。

6.根据权利要求5所述的接口电路布置,其中用于检测所述信号模式的负电压转变的阈值数量是基于存储在寄存器存储器处的值。

7.根据权利要求6所述的接口电路布置,其中所述i2c电路经由所述i2c数据端口接收所述负电压转变的阈值数量所基于的值,并且其中所接收的值被存储在所述寄存器存储器中。

8.一种集成电路(ic)器件,包括:

9.根据权利要求8所述的ic器件,其中所述方式检测电路进一步:

10.根据权利要求9所述的ic器件,其中所述方式检测电路通过以下方式产生所述选择信号:

11.根据权利要求9所述的ic器件,其中所述方式检测电路包括:

12.根据权利要求11所述的ic器件,其中所述方式检测电路还包括:

13.根据权利要求9所述的ic器件,其中耦合到i2c接口的数据线所耦合到的第四端子的spi的第二数据线对应于spi的主输入、从输出(miso)线。

14.根据权利要求9所述的ic器件,其中:

15.根据权利要求9所述的ic器件,其中当所述i2c接口激活时,耦合到所述spi的cs线的第一端子作为i2c地址端子操作。

16.一种由集成电路(ic)器件执行的方法,所述集成电路器件具有串行外围接口(spi)电路、内部集成电路(i2c)电路、耦合到所述spi电路的芯片选择(cs)线的第一端子、耦合到spi电路的数据线和i2c电路的数据线上的第二端子、以及耦合到spi电路的时钟线和i2c的时钟线的第三端子,该方法包括:

17.根据权利要求16所述的方法,其中:

18.根据权利要求17所述的方法,其中在选择所述spi电路或所述i2c电路中用于所述比较的负边缘的阈值数量是预定的。

19.根据权利要求17所述的方法,其中在选择所述spi电路或所述i2c电路中用于所述比较的负边缘的阈值数量是基于寄存器读取的。

20.根据权利要求17所述的方法,进一步包括:

技术总结

本公开涉及用于多协议通信接口的高效引脚共享集成电路(IC)器件。提供了与通信接口相关的系统和方法。一种用于集成电路(IC)设备之间的通信的接口电路布置,接口电路布置包括:串行外围接口(SPI)电路,具有SPI时钟端口、SPI数据端口和SPI芯片选择(CS)端口;具有I2C时钟端口和I2C数据端口的内部集成电路(I2C)电路,其中所述I2C时钟端口和所述SPI时钟端口电耦合到第一连接端口,并且其中所述12C数据端口和所述SPI数据端口电耦合到第二连接端口;模式检测电路,用于检测第三连接端口处的信号模式,所述第三连接端口电耦合到所述SPI CS端口;和选择电路,用于响应于所述模式检测电路的输出而选择性地将所述SPI电路或所述I2C电路耦合到数据路径。

技术研发人员:王勇,罗仁贵

受保护的技术使用者:亚德诺半导体国际无限责任公司

技术研发日:

技术公布日:2024/3/5

- 还没有人留言评论。精彩留言会获得点赞!