一种超高速伪随机数信号产生装置

本发明属于伪随机数信号产生,更为具体地讲,涉及一种超高速伪随机数信号产生装置。

背景技术:

1、在传统基于fpga的混沌迭代计算模块中,不同的方程间以及同一方程不同计算部分之间存在延时不匹配的现象。为避免出现迭代次序错乱的现象,传统的fpga混沌迭代计算模块主要采用busy-free的结构,即当前迭代未计算完成时,将整个混沌迭代计算模块置于busy状态,拒绝所有的数据输入。对于同一方程,先完成计算部分的计算结果存入寄存器中,等待其他计算部分完成后,再读出与其他计算部分进行,对于不同的方程,则先计算的方程的次态值通过寄存器寄存起来,待所有方程计算完毕后,再将统一输出,随后置混沌迭代计算模块于free状态,准备进入下一次迭代。

2、上述方法可以避免数据迭代混沌,但是平均计算耗时较长,如果混沌迭代计算需要数n个时钟(通常需要数百个时钟),则需要n个时钟才能输出一组混沌模型的次态值,效率较低。

3、此外,混沌迭代计算模块输出的路数有限,以三维混沌迭代计算模块为例,其输出就三路,即三个通道,这样在需要多通道输出的情况下,就不能满足需要。

技术实现思路

1、本发明的目的在于克服现有技术的不足,提供一种超高速伪随机数信号产生装置,以实现多通道多位伪随机数信号高速产生。

2、为实现上述发明目的,本发明超高速伪随机数信号产生装置,其特征在于,包括:

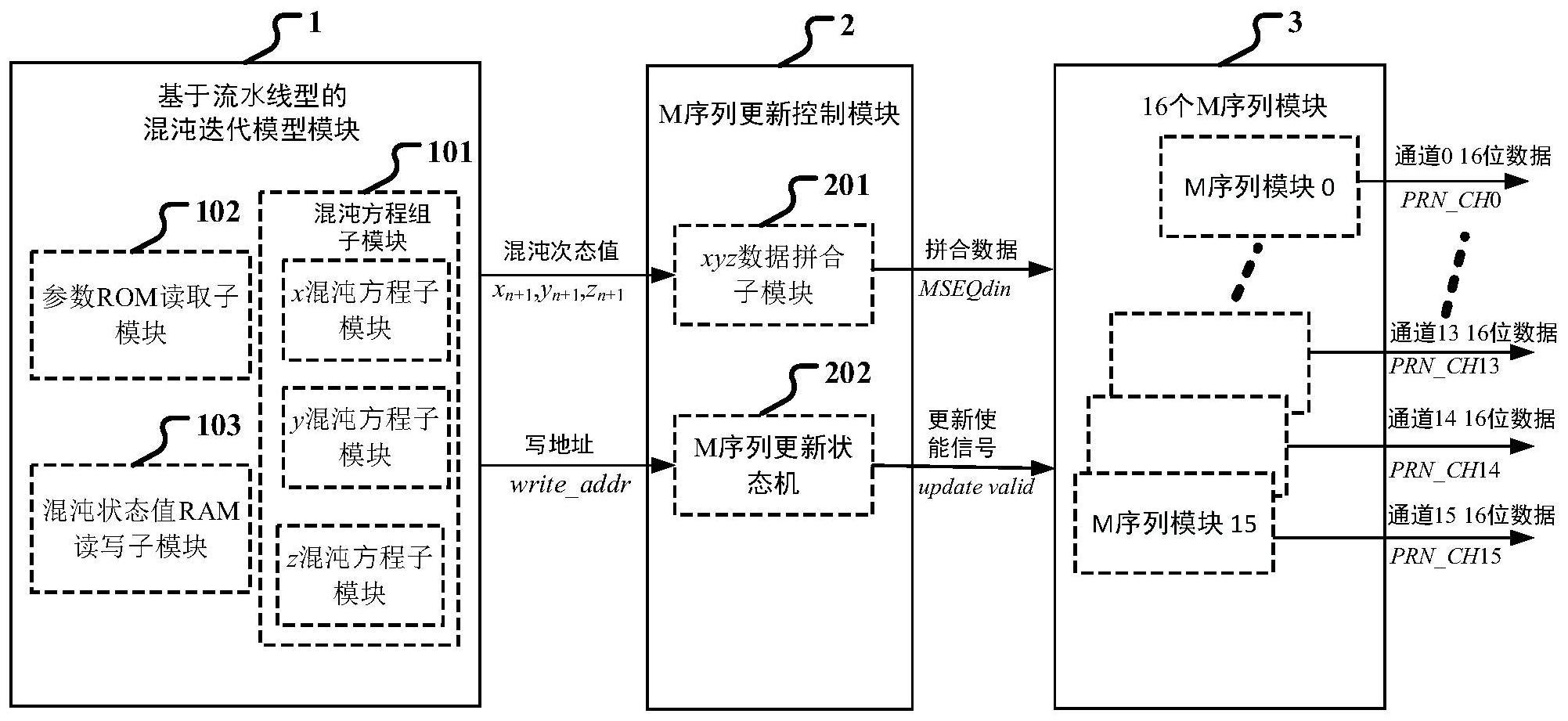

3、基于流水线型的混沌迭代模型模块,由混沌方程组子模块、参数rom读取子模块、混沌状态值ram读写子模块组成,混沌方程组子模块中各个混沌方程内部以及之间迭代计算需要同步进行延时时,采用移位寄存器进行延时移位寄存,移位寄存器中寄存器的数量等于需要延时的时钟个数,这样混沌方程组子模块可以进行流水迭代计算,参数rom读取子模块用于存放m组混沌方程参数,混沌状态值ram读写子模块用于存放m组混沌现态值,混沌现态值的初始值来自上位机,每个时钟从参数rom读取子模块读取一组混沌方程参数给混沌方程组子模块,从混沌状态值ram读写子模块读取一组混沌现态值给混沌方程组子模块,混沌方程组子模块依据接收的混沌方程参数和混沌现态值进行迭代计算,计算出的结果即混沌次态值一方面输出,另一方面作为下一次迭代计算的混沌现态值更新混沌状态值ram读写子模块中的混沌现态值,这样在每个时钟混沌方程组子模块输出一组混沌次态值,同时,输出更新混沌状态值ram读写子模块混沌现态值的写地址,其中,m大于一组混沌次态值计算所需的时钟个数;

4、m序列更新控制模块,用于接收混沌方程子模块输出的混沌次态值以及相应更新混沌状态值ram读写子模块混沌现态值的写地址的,并执行两项操作:①数据拼合:将混沌方程子模块输出的混沌次态值拼合为一个数据即拼合数据,并输出,②序列模块选择性更新:将写地址作为混沌序号驱动m序列更新状态机使更新使能信号有效;

5、多个m序列模块,每个m序列模块包括多个m序列发生器以及各自对应的m序列反馈系数rom,用于接收拼合数据和更新使能信号,并将拼合数据拆分重组为多组反馈系数读地址以及m序列发生器初值,每组反馈系数读地址以及m序列发生器初值对应一个m序列发生器,每个m序列模块在其接收的更新使能信号有效时,根据反馈系数读地址在对应的m序列反馈系数rom中读取m序列反馈系数,然后与m序列发生器初值一起更新m序列发生器的反馈系数和初值;m序列发生器每个时钟输出一位数据信号,将多个m序列发生器每个时钟输出的一位数据信号组成一个通道的多位数据信号;每个m序列模块输出一个通道的多位数据信号,多个m序列模块输出的多位数据信号构成多个通道多位伪随机数据信号。

6、本发明的目的是这样实现的。

7、本发明超高速伪随机数信号产生装置包括基于流水线型的混沌迭代模型模块、m序列更新控制模块以及多个m序列模块,其中,基于流水线型混沌迭代模型模块中混沌方程组子模块采用移位寄存器进行延时移位寄存,同时增加参数rom读取子模块以及混沌状态值ram读写子模块,构成流水迭代计算,这样在每个时钟混沌方程输出一个混沌次态值,从而高速产生迭代输出值。此外,m序列更新控制模块将各个混沌方程输出的混沌次态值拼合得到拼合数据,并根据写地址产生更新使能信号,多个m序列模块在更新使能信号有效时,将拼合数据拆分重组为多个m序列发生器对应的多组反馈系数读地址以及m序列发生器初值,根据反馈系数读地址得到反馈系数,这样产生一个多个通道多位数据信号,通过这样的方式,从反馈系数和初值两个维度保证了m序列模块构造的随机性,从而保证m序列发生器的输出值始终随机,避免陷入周期性重复。本发明将混沌迭代模型与m序列发生器相结合,实现了多通道多位伪随机数信号的均匀、高速产生。

技术特征:

1.一种超高速伪随机数信号产生装置,其特征在于,包括:

2.根据权利要求1所述的超高速伪随机数信号产生装置,其特征在于,所述m序列更新控制模块将拼合数据同时发送给多个m序列模块,m序列更新状态机根据写地址不断使多个m序列模块的更新使能信号逐个有效。

3.根据权利要求1所述的超高速伪随机数信号产生装置,其特征在于,所述m序列更新控制模块根据写地址不断进行数据拼合,并存储,当拼合数据存储数量大于m序列模块的数量时,所有存储的拼合数据读出,分别输出到各自对应的m序列模块,同时,输出一路更新使能信号到所有m序列模块,使所有m序列模块有效,读取拼合数据。

技术总结

本发明公开了一种超高速伪随机数信号产生装置,其中,基于流水线型混沌迭代模型模块中混沌方程组子模块采用移位寄存器进行延时移位寄存,同时增加参数ROM读取子模块以及混沌状态值RAM读写子模块,构成流水迭代计算,从而高速产生迭代输出值。此外,M序列更新控制模块将各个混沌方程输出的混沌次态值拼合得到拼合数据,并根据写地址产生更新使能信号,多个M序列模块在更新使能信号有效时,将拼合数据拆分重组为多个M序列发生器对应的多组反馈系数读地址以及M序列发生器初值,根据反馈系数读地址得到反馈系数,这样产生一个多个通道多位数据信号,从而保证M序列发生器的输出值始终随机,避免陷入周期性重复。本发明将混沌迭代模型与M序列发生器相结合,实现了多通道多位伪随机数信号的均匀、高速产生。

技术研发人员:许波,罗晓伟,钱磊,耿航,苟轩,陈凯,程玉华,何仁军

受保护的技术使用者:电子科技大学

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!