一种访存方法、装置、电子设备及可读存储介质与流程

本发明涉及计算机,尤其涉及一种访存方法、装置、电子设备及可读存储介质。

背景技术:

1、risc-v是目前使用较为广泛的一种精简指令集。risc-v指令集中提供了一种段访问内存指令(也即segment类型的指令),该指令有如下访存方式:segment向量访存指令的目的向量寄存器的分配方式由emul(或lmul)和nf指定,其中,emul用于指示合并向量寄存器组中有效向量寄存器的数目,lmul用于指示合并向量寄存器组中向量寄存器的数目。emul(或lmul)的取值会出现以下7中情况,分别是:1/8、1/4、1/2、1、2、4、8,一个目的寄存器的宽度是128bit。nf用于指示合并向量寄存器组的数目,nf的取值为0至8之间的整数。segment向量访存指令访问元素的宽度由eew(有效元素宽度)或sew(单个元素宽度)指定,分别是:1 byte,2 byte,4 byte,8 byte。以segment strided 类型的指令为例,考虑一种极限情况,emul=1,nf=8,eew=1byte,这样的话填满一个目的寄存器需要访问16次内存,如果8个目的寄存器全部填满,需要访问128次内存。

2、显然,相关技术中段访问内存指令的访问内存的次数过多,容易导致访存延迟,且浪费功耗。

技术实现思路

1、本发明实施例提供一种访存方法、装置、电子设备及可读存储介质,可以解决相关技术中段访问内存指令的访问内存的次数过多,容易导致访存延迟,且浪费功耗的问题。

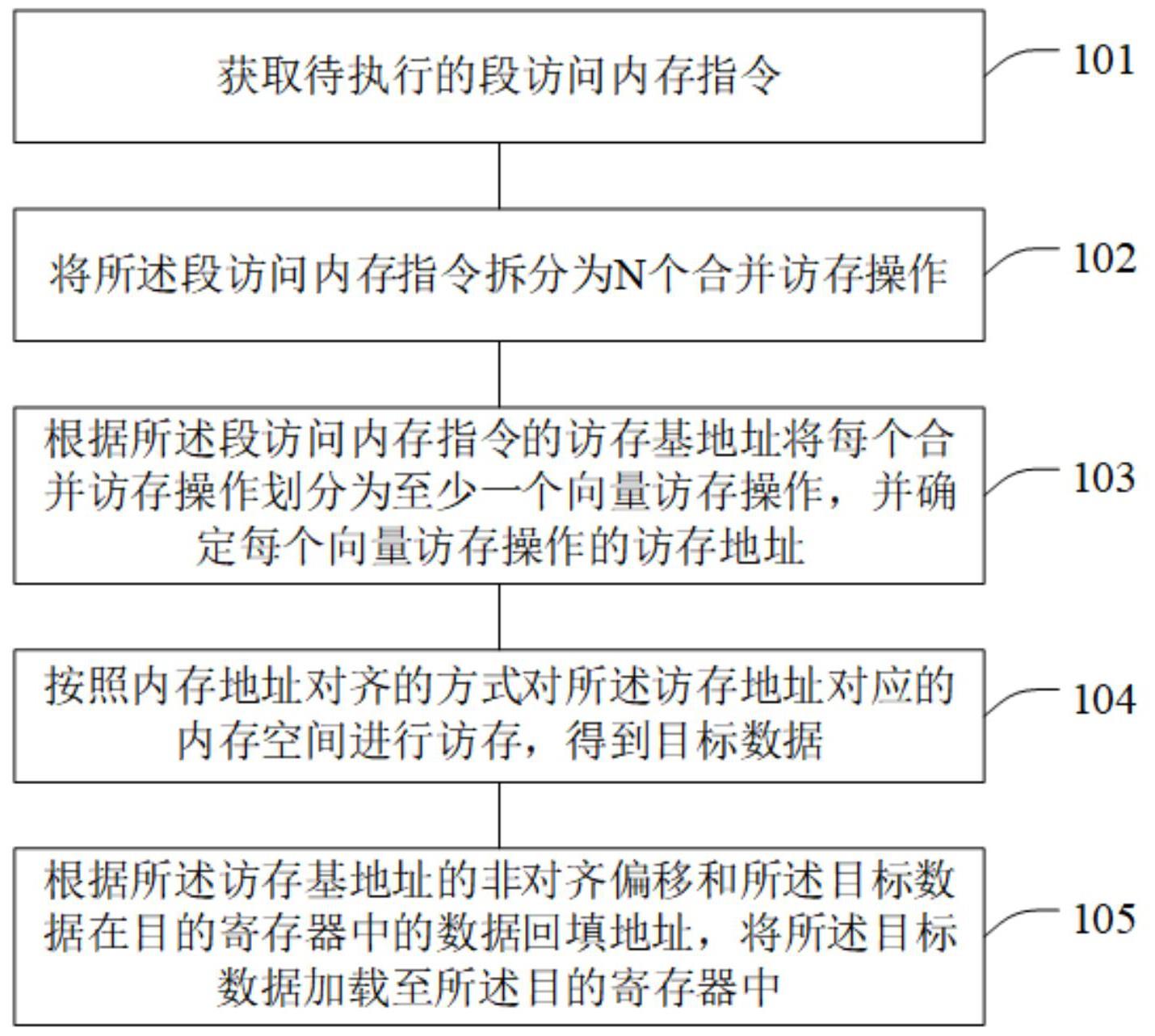

2、为了解决上述问题,本发明实施例公开了一种访存方法,所述方法包括:

3、获取待执行的段访问内存指令,所述段访问内存指令用于将数据段存储到目的寄存器中;

4、将所述段访问内存指令拆分为n个合并访存操作;一个合并访存操作用于对nf个合并向量寄存器组中位置索引相同的元素进行合并访存,nf为所述合并向量寄存器组的数目;nf和n均为正整数;所述位置索引用于指示元素在每个合并向量寄存器组中的位置;

5、根据所述段访问内存指令的访存基地址将每个合并访存操作划分为至少一个向量访存操作,并确定每个向量访存操作的访存地址;一个向量访存操作用于访问一次内存;

6、按照内存地址对齐的方式对所述访存地址对应的内存空间进行访存,得到目标数据;

7、根据所述访存基地址的非对齐偏移和所述目标数据在目的寄存器中的数据回填地址,将所述目标数据加载至所述目的寄存器中。

8、另一方面,本发明实施例公开了一种访存装置,所述装置包括:

9、指令获取模块,用于获取待执行的段访问内存指令,所述段访问内存指令用于将数据段存储到目的寄存器中;

10、第一拆分模块,用于将所述段访问内存指令拆分为n个合并访存操作;一个合并访存操作用于对nf个合并向量寄存器组中位置索引相同的元素进行合并访存,nf为所述合并向量寄存器组的数目;nf和n均为正整数;所述位置索引用于指示元素在每个合并向量寄存器组中的位置;

11、第二拆分模块,用于根据所述段访问内存指令的访存基地址将每个合并访存操作划分为至少一个向量访存操作,并确定每个向量访存操作的访存地址;一个向量访存操作用于访问一次内存;

12、访存模块,用于按照内存地址对齐的方式对所述访存地址对应的内存空间进行访存,得到目标数据;

13、加载模块,用于根据所述访存基地址的非对齐偏移和所述目标数据在目的寄存器中的数据回填地址,将所述目标数据加载至所述目的寄存器中。

14、再一方面,本发明实施例还公开了一种电子设备,所述电子设备包括处理器、存储器、通信接口和通信总线,所述处理器、所述存储器和所述通信接口通过所述通信总线完成相互间的通信;所述存储器用于存放可执行指令,所述可执行指令使所述处理器执行前述的访存方法。

15、本发明实施例还公开了一种可读存储介质,当所述可读存储介质中的指令由电子设备的处理器执行时,使得电子设备能够执行前述的访存方法。

16、本发明实施例包括以下优点:

17、本发明实施例提供了一种访存方法,通过将段访问内存指令拆分为n个合并访存操作,对nf个合并向量寄存器组中位置索引相同的元素进行合并访存;根据段访问内存指令的访存基地址将每个合并访存操作划分为至少一个向量访存操作,每个向量访存操作用于访问一次内存;按照内存地址对齐的方式对向量访存操作的访存地址对应的内存空间进行访存,得到目标数据,并根据所述访存基地址的非对齐偏移和所述目标数据在目的寄存器中的数据回填地址,将所述目标数据加载至所述目的寄存器中。相比于相关技术中按照元素宽度访问内存,本发明实施例对nf个合并寄存器组中位置索引相同的元素的进行了合并访存,有效减少了段访问内存指令的访存次数,有利于降低访存延迟和功耗,提升了处理器性能。

技术特征:

1.一种访存方法,其特征在于,所述方法包括:

2.根据权利要求1所述的方法,其特征在于,所述将所述段访问内存指令拆分为n个合并访存操作,包括:

3.根据权利要求2所述的方法,其特征在于,所述根据所述第一参数、所述第二参数和所述第三参数,确定第四参数,包括:

4.根据权利要求3所述的方法,其特征在于,所述根据所述第四编码值确定所述第四参数的数值之前,所述方法还包括:

5.根据权利要求2所述的方法,其特征在于,所述根据所述第一参数、所述第二参数、所述第三参数、所述第四参数和向量寄存器宽度,确定所述段访问内存指令对应的合并访存操作的数目n,包括:

6.根据权利要求2所述的方法,其特征在于,所述按照内存地址对齐的方式对所述访存地址对应的内存空间进行访存,得到目标数据,包括:

7.根据权利要求6所述的方法,其特征在于,所述段访问内存指令的寻址模式为跨步寻址模式;所述段访问内存指令的第(n+1)个合并访存操作访存的第(i+1)个元素的地址a((n+1),(i+1))=a((n+1),i)+第一参数=a(n,(i+1))+x;其中,a((n+1),i)为所述段访问内存指令的第(n+1)个合并访存操作访存的第i个元素的地址;a(n,(i+1))为所述段访问内存指令的第n个合并访存操作访存的第(i+1)个元素的地址;n大于或等于0,且n小于或等于n;i大于或等于0,且i小于或等于nf;x为所述段访问内存指令的跨步值。

8.根据权利要求6所述的方法,其特征在于,所述段访问内存指令的寻址模式为单位跨步寻址模式;所述段访问内存指令的第(n+1)个合并访存操作访存的第(i+1)个元素的地址a((n+1),(i+1))=a((n+1),i)+第一参数= a(n,(i+1))+z,z = nf×第一参数;其中,a((n+1),i)为所述段访问内存指令的第(n+1)个合并访存操作访存的第i个元素的地址;a(n,(i+1))为所述段访问内存指令的第n个合并访存操作访存的第(i+1)个元素的地址;n大于或等于0,且n小于或等于n;i大于或等于0,且i小于或等于nf。

9.根据权利要求6所述的方法,其特征在于,所述段访问内存指令的寻址模式为索引寻址模式;所述段访问内存指令的第(n+1)个合并访存操作访存的第(i+1)个元素的地址a((n+1),(i+1))=a((n+1),i)+第二参数;其中,a((n+1),i)为所述段访问内存指令的第(n+1)个合并访存操作访存的第i个元素的地址;n大于或等于0,且n小于或等于n;i大于或等于0,且i小于或等于nf。

10.根据权利要求1所述的方法,其特征在于,所述根据所述访存基地址的非对齐偏移和所述目标数据在目的寄存器中的数据回填地址,将所述目标数据加载至所述目的寄存器中,包括:

11.一种访存装置,其特征在于,所述装置包括:

12.一种电子设备,其特征在于,所述电子设备包括处理器、存储器、通信接口和通信总线,所述处理器、所述存储器和所述通信接口通过所述通信总线完成相互间的通信;所述存储器用于存放可执行指令,所述可执行指令使所述处理器执行如权利要求1至10中任一项所述的访存方法。

13.一种可读存储介质,其特征在于,当所述可读存储介质中的指令由电子设备的处理器执行时,使得所述处理器能够执行如权利要求1至10中任一项所述的访存方法。

技术总结

本发明实施例提供一种访存方法、装置、电子设备及可读存储介质,涉及计算机技术领域,该方法包括:获取待执行的段访问内存指令;将所述段访问内存指令拆分为N个合并访存操作;根据所述段访问内存指令的访存基地址将每个合并访存操作划分为至少一个向量访存操作,并确定每个向量访存操作的访存地址;一个向量访存操作用于访问一次内存;按照内存地址对齐的方式对所述访存地址对应的内存空间进行访存,得到目标数据;根据所述访存基地址的非对齐偏移和所述目标数据在目的寄存器中的数据回填地址,将所述目标数据加载至所述目的寄存器中。本发明实施例减少了段访问内存指令的访存次数,有利于降低访存延迟和功耗,提升了处理器性能。

技术研发人员:马建露,王华强,王凯帆,陈键,唐丹,包云岗

受保护的技术使用者:北京开源芯片研究院

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!