一种基于1T1R忆阻器和原位计算的二值神经网络加速系统

本发明设计半导体集成电路和神经网络领域,具体涉及到一种基于1t1r忆阻器和原位计算的二值神经网络加速系统。

背景技术:

1、二值神经网络是将神经网络的权重和激活函数输出都量化为二值的神经网络。随着大数据与物联网的快速发展,人类社会对于神经网络的需求越来越高,但大规模神经网络具有巨大的计算量和参数存储量,这将会占用大量的资源。而二进制神经网络相比传统神经网络不仅大大减少了所需的内存,同时还能够保持较高的精度,可以节省大量的内存资源与运算资源,尤其对于神经网络的边缘侧部署具有重大意义。

2、忆阻器是一种非易失性存储器,忆阻器的阻值可以根据流经它的电荷数量发生改变。目前具有高电阻和低电阻两种状态的忆阻器工艺已经较为成熟。对于具有二种状态的忆阻器的存内计算结构在大规模的神经网络计算中具有较高的现实意义。

3、目前已有的通过忆阻器阵列实现二值神经网络的电路系统,需要高精度的模数转换器(adc)或者较大面积的数字计数器来实现计算结果的统计,很难做到保证高计算可靠性的同时,兼具较小的面积。

技术实现思路

1、为解决使基于忆阻器阵列的二值神经网络加速器兼具高计算可靠性和小面积的技术问题,本发明提供了一种基于1t1r(1个晶体管1个忆阻器)忆阻器阵列和原位计算的无adc的高可靠性存内计算二值神经网络加速系统,可以用于高实时性的目标识别、图像分类、点云分类、语义分割、自然语言处理、人体姿态估计。由于完全不含有adc所以在对二进制神经网络进行加速的同时也具有高可靠性,技术方案具体如下:

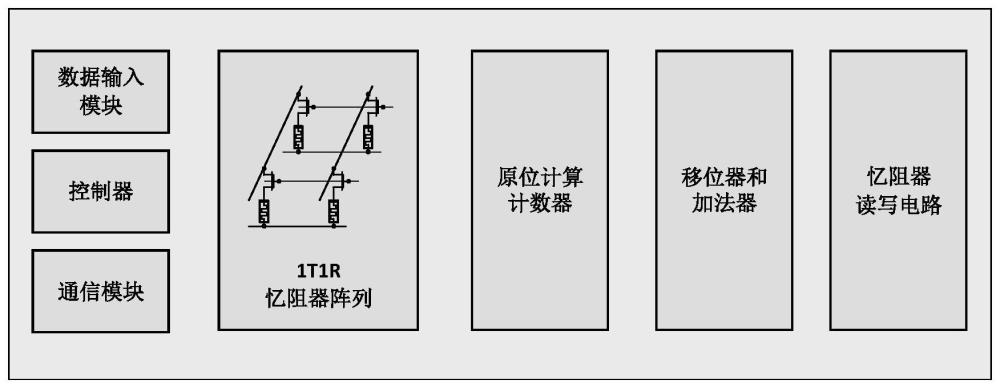

2、一种基于1t1r忆阻器和原位计算的二值神经网络加速系统,具体包括如下模块:忆阻器阵列模块、忆阻器读写电路模块、原位计算计数器模块、数据输入模块、移位器和加法器模块、通信模块、控制器模块;

3、其中,数据输入模块、移位器和加法器模块、通信模块、控制器模块位于fpga中;二值神经网络的权重通过上位机发送到通信模块,通信模块再将二值神经网络的权重数据发送至忆阻器读写电路模块,然后忆阻器读写电路模块将权重载入到忆阻器阵列模块中;上位机将二值神经网络运算的输入数据发送至数据输入模块,数据输入模块将二值神经网络运算的输入数据转换为wl信号并输入到忆阻器阵列模块中,从而控制忆阻器阵列中与忆阻器连接的mos管的打开与关闭;忆阻器阵列模块既用于存储二值神经网络的权重,又参与二值神经网络的运算,通过忆阻器阵列模块进行乘法运算,乘法运算的结果通过bl信号输出给原位计算计数器模块,原位计算计数器模块负责完成矩阵运算中的加法运算,进行加操作或者减操作,然后将运算结果发送给通信模块,通信模块将运算结果发送给移位器和加法器模块,移位器和加法器模块将输入中每个bit的运算结果进行移位和累加后,将结果发送给通信模块,再通过通信模块发送给上位机;

4、控制器模块负责控制fpga中的数据输入模块、移位器和加法器模块、通信模块的启动。

5、其中,在更改二值神经网络的参数后,也需要通过忆阻器读写电路模块对忆阻器阵列模块中的权重进行修改。

6、本发明的有益效果为:本发明设计了一种面积更小,计算可靠性更高的基于1t1r忆阻器和原位计算的二值神经网络加速系统,在进行需要部署在边缘测的高实时性的目标识别、图像分类、点云分类、语义分割、自然语言处理、人体姿态估计等任务时,可以提供更精确的加速运算,并且消耗更少的芯片资源,在提高计算效率的同时,还可以芯片降低成本。

技术特征:

1.一种基于1t1r忆阻器和原位计算的二值神经网络加速系统,其特征在于,包括如下模块:忆阻器阵列模块、忆阻器读写电路模块、原位计算计数器模块、数据输入模块、移位器和加法器模块、通信模块、控制器模块;

2.根据权利要求1所述的一种基于1t1r忆阻器和原位计算的二值神经网络加速系统,其特征在于,在更改二值神经网络的参数后,也需要通过忆阻器读写电路模块对忆阻器阵列模块中的权重进行修改。

3.根据权利要求1所述的一种基于1t1r忆阻器和原位计算的二值神经网络加速系统,其特征在于,数据输入模块由多个d触发器与数个逻辑门组成,输入为时钟信号,将需要发送给忆阻器阵列的输入数据输出为wl信号,d触发器的数量与wl信号的数量相同,d触发器与数个逻辑门构成的组合电路用于生成wl信号,以实现每个时钟周期都使一个输入数据为1对应的wl信号拉高一个周期,且输入数据为0对应的wl信号不拉高;当数据输入模块最左端d触发器输入端拉高一个周期后,所有输入为1的wl信号也会依次分时拉高一个周期。如果与wl信号相连的忆阻器的权重为+1,则当wl信号拉高时,该忆阻器对应的bl信号也会拉高,如果与wl信号相连的忆阻器的权重为-1,则当wl信号拉高时,该忆阻器对应的bl信号会拉低;设wl信号共有n个,与wl k信号和bl m信号相连的忆阻器存储的权重为wkm,与wl k信号对应的输入为xk,其中,m是列标记,k是行标记,则bl m信号对应的运算结果outm,如公式(1)所示:

4.根据权利要求1所述的一种基于1t1r忆阻器和原位计算的二值神经网络加速系统,其特征在于,所述原位计算计数器的级数可以根据wl信号的数量进行设置;每bit原位计算计数器电路的输入为系统时钟clk信号、clk_n信号、bl信号和bl_n信号,其中clk_n信号是clk信号的反相信号,bl_n信号是bl信号的反相信号,以及来自数据输入模块的w_en信号、wdata信号和wdata_n信号,用于更改计数器数据,其中wdata_n信号是wdata信号的反相信号;每bit原位计算计数器电路的输出为数据out和用做下一级原位计算计数器的clk_out;每bit原位计算计数器电路包括3个反相器、11个nmos管开关和1个电容;反相器1的首端连接反相器2的尾端,反相器2的首端为结点1,反相器2的尾端为结点2;反相器1的尾端连接nmos管1的漏极,nmos管1的源极连接结点1,nmos管1的栅极连接clk_n信号;这样当clk信号为低时,开关打开,两个反相器将对数据out进行锁存;其中结点2存储输出数据out;电容一端接地,另一端为结点3,结点3连接nmos管2的源极,结点2连接nmos管2的漏极,clk_n信号连接nmos管2的栅极;结点3连接nmos管3的漏极,结点1连接nmos管3的源极,nmos管3的栅极连接clk;结点1连接nmos管4的源极,nmos管4的漏极连接wdata_n信号,nmos管4的栅极连接w_en信号;结点2连接nmos管5的源极,nmos管5的漏极连接wdata信号,nmos管5的栅极连接w_en信号;结点2连接nmos管6的漏极,nmos管6的源极为结点4,nmos管6的栅极连接clk信号;nmos管7的漏极连接结点4,nmos管7的源极接地,nmos管7的栅极连接clk_n信号;结点2连接反相器3的首端,反相器3的尾端连接nmos管8的漏极,nmos管8的源极为结点5,nmos管8的栅极连接clk信号;结点5连接nmos管9的漏极,nmos管9的源极接地,nmos管9的栅极连接clk_n信号;结点4连接nmos管10的漏极,nmos管10的源极为结点6,nmos管10的栅极连接bl_n信号;结点5连接nmos管11的漏极,nmos管11的源极连接结点6,nmos管11的栅极连接bl信号,结点6为用做下一级原位计算计数器的clk_out。

技术总结

本发明公开了一种基于1T1R忆阻器和原位计算的二值神经网络加速系统,涉及半导体集成电路和神经网络领域。本发明利用了1T1R忆阻器阵列中忆阻器的存储特性,并设计了原位计算计数器电路和对应的输入数据编码方法,通过存内计算的结构对二值神经网络进行加速。因为本发明不包含ADC结构,所以在对网络进行加速的同时也具有高可靠性。相较于传统的忆阻器村内计算加速器,本发明不仅只需要用到忆阻器的两个状态,具有很高的硬件实现性,而且无ADC结构,具有更高的集成度和可靠性。本发明可以应用于高实时性的目标识别、图像分类、点云分类、语义分割、自然语言处理、人体姿态估计。

技术研发人员:刘洋,潘瑞城,白剑,张逍洋,王俊杰

受保护的技术使用者:电子科技大学

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!