一种频率自适应的异步电路及其约束方法

本申请涉及集成电路设计,尤其是一种频率自适应的异步电路及其约束方法。

背景技术:

1、近年来随着集成电路制造工艺尺度的不断缩小和设计规模的增大,同步电路设计所带来的诸如时钟偏移、功耗高、电磁干扰等问题愈发突出,而异步电路的工作方式是各个模块之间通过相互握手来实现数据通信,具有低功耗、无时钟偏移问题和事件驱动的特性,以其独特的优势有希望成为后摩尔时代集成电路发展的突破方向。

2、然而,现有的异步电路设计方法,其产生的一系列时钟均为固定周期的。这意味着,如果某一流水级间的关键路径特别长,整个异步处理器依然只能按最慢路径延迟来工作,异步电路的性能依然受关键路径限制。

技术实现思路

1、有鉴于此,本申请提供一种频率自适应的异步电路及其约束方法,以提高异步电路的性能。

2、本申请的一方面提供了一种频率自适应的异步电路,包括:数据通路和控制通路;

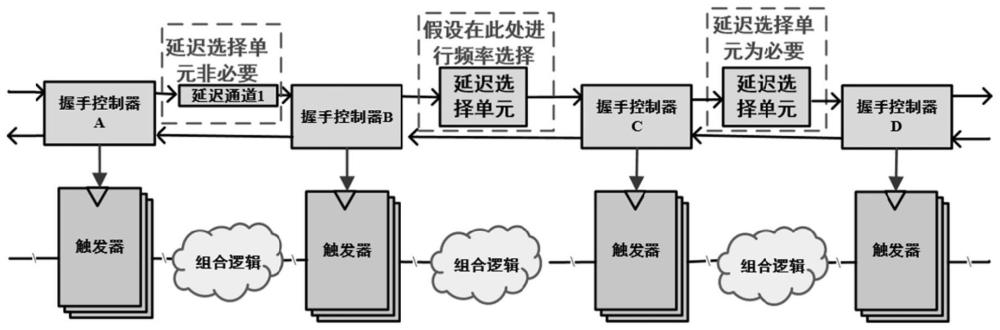

3、其中,数据通路包括多个触发器和多个组合逻辑电路,每个组合逻辑电路连接在两个触发器之间;触发器用于暂存数据,组合逻辑电路用于进行组合运算;

4、控制通路包括多个握手控制器;握手控制器与触发器的连接方式包括:一个握手控制器与一个触发器连接,且相邻的两个触发器所对应的两个握手控制器互相连接,或者,一个握手控制器与数据通路中的多个触发器相连;互相连接的两个握手控制器通过请求信号和应答信号实现握手通信;

5、相邻的两个握手控制器之间还包括延迟模块,所述延迟模块用于在输出请求信号到输入请求信号之间进行延迟匹配操作。

6、可选地,所述延迟模块采用延迟通道;所述延迟通道的输入端用于接收所述输出请求信号,所述延迟通道的输出端用于输出所述输入请求信号;

7、或者,所述延迟模块采用延迟选择单元;所述延迟选择单元包括解复用器、复用器及多条延迟通道;每条所述延迟通道的输入端与所述解复用器的输出端连接,每条所述延迟通道的输出端与所述复用器的输入端连接;所述解复用器的输入端用于接收所述输出请求信号,所述复用器的输出端用于输出所述输入请求信号。

8、可选地,在需要改变频率的位置及其在数据流向方向之后的各个所述延迟模块均采用所述延迟选择单元;所述需要改变频率的位置处于互相连接的两个握手控制器之间;

9、在需要改变频率的位置之前的各个所述延迟模块均采用所述延迟通道或者所述延迟选择单元。

10、可选地,所述延迟通道由缓冲器链、反相器链或逻辑门链中的其中之一构成。

11、可选地,所述握手控制器为任意的异步电路控制器。

12、本申请的另一方面还提供了一种频率自适应的异步电路的约束方法,包括:用于约束上述的一种频率自适应的异步电路,所述方法包括:

13、对于经过第一组合逻辑电路的计时路径,将前一个握手控制器生成的本地时钟定义为源时钟,周期设置为第一组合逻辑电路的时延;根据第一组合逻辑电路的时延定义后续的时钟信号;

14、对于从后触发器到前触发器的反馈路径,修改前后两个触发器的触发时间,并保持所述触发时间;

15、对于经过第二组合逻辑电路的计时路径,设置最大时延为第二组合逻辑电路的时延;

16、其中,第一组合逻辑电路的时延小于第二组合逻辑电路的时延,第一、第二组合逻辑电路均连接在前触发器和后触发器之间。

17、可选地,所述方法还包括:

18、识别并统计所有经过第二组合逻辑电路的计时路径,并生成统计报告。

19、本申请的另一方面还提供了一种频率自适应的异步电路的约束装置,包括:

20、第一单元,用于对于经过第一组合逻辑电路的计时路径,将前一个握手控制器生成的本地时钟定义为源时钟,周期设置为第一组合逻辑电路的时延;根据第一组合逻辑电路的时延定义后续的时钟信号;

21、第二单元,用于对于从后触发器到前触发器的反馈路径,修改前后两个触发器的触发时间,并保持所述触发时间;

22、第三单元,用于对于经过第二组合逻辑电路的计时路径,设置最大时延为第二组合逻辑电路的时延;

23、其中,第一组合逻辑电路的时延小于第二组合逻辑电路的时延,第一、第二组合逻辑电路均连接在前触发器和后触发器之间。

24、本申请的另一方面还提供了一种电子设备,包括处理器以及存储器;

25、所述存储器用于存储程序;

26、所述处理器执行所述程序实现所述的方法。

27、本申请的另一方面还提供了一种计算机可读存储介质,所述存储介质存储有程序,所述程序被处理器执行实现所述的方法。

28、本申请还公开了一种计算机程序产品或计算机程序,该计算机程序产品或计算机程序包括计算机指令,该计算机指令存储在计算机可读存储介质中。电子设备的处理器可以从计算机可读存储介质读取该计算机指令,处理器执行该计算机指令,使得该电子设备执行上述的方法。

29、本申请具备以下有益效果:

30、1.能够实现按需自动调整频率;

31、2.相比于现有同步电路的dvfs,本申请的方法面向异步电路。dvfs只是通过调整电压调整延迟,并没有优化关键路径;本申请的方法对关键路径进行了优化。dvfs的细粒度为任务级别;本申请的方法的细粒度极低,如在处理器中可低至指令级。dvfs需要复杂的算法和设计,本申请的方法设计实现简单。dvfs存在牺牲精度的风险,本申请的方法不存在。

32、3.相比与cscd方法为数模混合设计,其设计极其复杂,本申请设计简单;cscd方法需要版图中时序逻辑和组合逻辑分开,对速度和功耗有不利影响,本申请不存在此问题;cscd方法需要设计灵敏方法器,且存在失效风险,本申请不需要放大器,也无此问题。

技术特征:

1.一种频率自适应的异步电路,其特征在于,包括:数据通路和控制通路;

2.根据权利要求1所述的一种频率自适应的异步电路,其特征在于,所述延迟模块采用延迟通道;所述延迟通道的输入端用于接收所述输出请求信号,所述延迟通道的输出端用于输出所述输入请求信号;

3.根据权利要求2所述的一种频率自适应的异步电路,其特征在于,在需要改变频率的位置及其在数据流向方向之后的各个所述延迟模块均采用所述延迟选择单元;所述需要改变频率的位置处于互相连接的两个握手控制器之间;

4.根据权利要求2或3所述的一种频率自适应的异步电路,其特征在于,所述延迟通道由缓冲器链、反相器链或逻辑门链中的其中之一构成。

5.根据权利要求1至3任一项所述的一种频率自适应的异步电路,其特征在于,所述握手控制器为任意的异步电路控制器。

6.一种频率自适应的异步电路的约束方法,其特征在于,用于约束如权利要求1至5任一项所述的一种频率自适应的异步电路,所述方法包括:

7.根据权利要求6所述的一种频率自适应的异步电路的约束方法,其特征在于,所述方法还包括:

8.一种频率自适应的异步电路的约束装置,其特征在于,包括:

9.一种电子设备,其特征在于,包括处理器以及存储器;

10.一种计算机可读存储介质,其特征在于,所述存储介质存储有程序,所述程序被处理器执行实现如权利要求6或7中任一项所述的方法。

技术总结

本申请公开了一种频率自适应的异步电路及其约束方法,电路包括:数据通路和控制通路;数据通路包括多个触发器和多个组合逻辑电路,每个组合逻辑电路连接在两个触发器之间;控制通路包括多个握手控制器;握手控制器与触发器的连接方式包括:一个握手控制器与一个触发器连接,且相邻的两个触发器所对应的两个握手控制器互相连接,或者,一个握手控制器与数据通路中的多个触发器相连;相邻的两个握手控制器之间还包括延迟模块,延迟模块用于在输出请求信号到输入请求信号之间进行延迟匹配操作。本申请提高了异步电路的性能,可广泛应用于集成电路设计技术领域。

技术研发人员:虞志益,周凌峰,肖山林,王慧瑶,王景海,许泽阳,王博涵

受保护的技术使用者:中山大学

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!