背景技术:

1、例如移动电话、个人数字助理(pda)、数码相机、便携式播放器、游戏和其它装置的计算装置需要将更多性能和特征集成到越来越小的空间中。因此,处理器裸片的密度和集成在单个集成电路(ic)封装内的裸片的数目增加。一些传统的多芯片模块包括两个或更多个半导体芯片,所述半导体芯片并排安装在载体衬底上,或者在一些情况下安装在中介层(所谓的“2.5d”)上,所述中介层又安装在载体衬底上。

技术实现思路

技术特征:1.一种处理器,包括:

2.根据权利要求1所述的处理器,其中,所述第一gpu小芯片被配置为通过经由所述有源电桥小芯片将所述存储器访问请求路由到所述第二gpu小芯片来路由所述存储器访问请求。

3.根据权利要求2所述的处理器,其中,所述第一gpu小芯片被配置为响应于确定与所述存储器访问请求相关联的数据被存储在与所述第二gpu小芯片相关联的存储器中,将所述存储器访问请求路由到所述第二gpu小芯片。

4.根据权利要求1所述的处理器,其中,所述第一gpu小芯片被配置为通过将所述存储器访问请求路由到由所述第一cpu小芯片和所述第二gpu小芯片共享的在所述有源电桥小芯片处的高速缓存存储器级来路由所述存储器访问请求。

5.根据权利要求4所述的处理器,其中,所述高速缓存存储器级包括在所述第一gpu小芯片和所述第二gpu小芯片上一致的统一高速缓存存储器。

6.根据权利要求1所述的处理器,其中,所述第一gpu小芯片进一步被配置为:

7.根据权利要求1所述的处理器,其中,所述第一gpu小芯片被配置为从所述有源电桥小芯片请求与所述存储器访问请求相关联的数据。

8.根据权利要求1所述的处理器,其中,所述有源电桥小芯片可通信地耦合所述gpu小芯片阵列中的gpu小芯片。

9.根据权利要求1所述的处理器,其中,所述第一gpu小芯片还包括可扩展数据结构,所述可扩展数据构造被配置成从所述cpu接收所述存储器访问请求。

10.一种系统,包括:

11.根据权利要求10所述的系统,其中,所述第一gpu小芯片进一步被配置为:

12.根据权利要求10所述的系统,其中,所述第一gpu小芯片进一步被配置为:

13.根据权利要求10所述的系统,其中,所述第一gpu小芯片进一步被配置为:

14.根据权利要求10所述的系统,其中,所述有源电桥小芯片包括由所述第一gpu小芯片和所述第二gpu小芯片共享的高速缓存存储器级别。

15.根据权利要求14所述的系统,其中,所述高速缓存存储器级包括在所述gpu小芯片阵列的所述第一和第二gpu小芯片上一致的统一高速缓存存储器。

16.一种方法,包括:

17.根据权利要求16所述的方法,其中将所述存储器访问请求路由到所述第二gpu小芯片是响应于确定与所述存储器访问请求相关联的数据存储在与所述第二gpu小芯片相关联的存储器中。

18.根据权利要求16所述的方法,其中路由所述存储器访问请求包括:

19.根据权利要求16所述的方法,其中路由所述存储器访问请求包括:

20.根据权利要求19所述的方法,其中所述高速缓存存储器级是所述有源电桥小芯片处的统一的最后一级高速缓存。

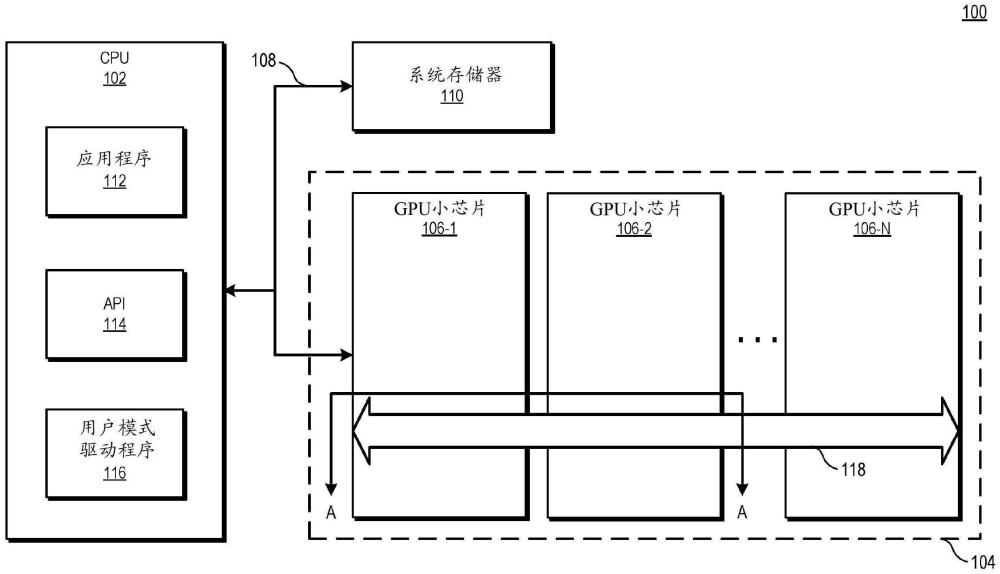

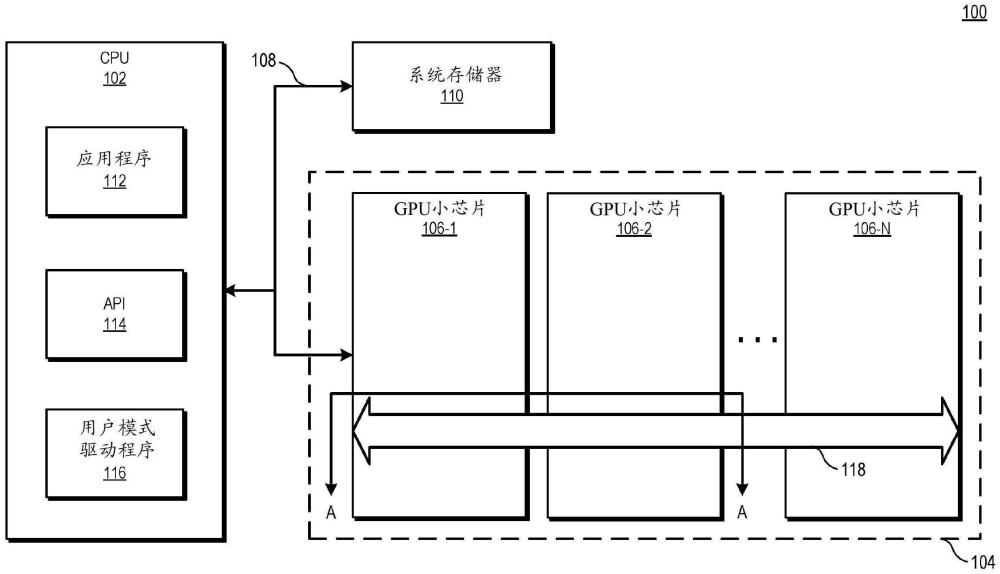

技术总结一种小芯片系统[100]包括中央处理单元(CPU)[102],其可通信地耦合至GPU小芯片阵列[104]的第一GPU小芯片[106‑1]。所述GPU小芯片阵列包括经由总线[108]可通信地耦合至所述CPU的所述第一GPU小芯片以及经由有源电桥小芯片[118]可通信地耦合至所述第一GPU小芯片的第二GPU小芯片[106‑2]。所述有源电桥小芯片是有源硅裸片,所述有源硅裸片桥接GPU小芯片并允许将片上系统(SoC)功能分成更小的功能小芯片组。

技术研发人员:斯凯勒·J·萨利赫,吴锐进

受保护的技术使用者:超威半导体公司

技术研发日:技术公布日:2024/4/17