一种验证方法、芯片、系统、电子设备及可读存储介质与流程

本发明涉及计算机,尤其涉及一种验证方法、芯片、系统、电子设备及可读存储介质。

背景技术:

1、在相关技术中,对于高层次综合(high-level synthesis,hls)设计的验证,通常是采用软件仿真的验证方式,与fpga原型验证、fpga仿真等硬件仿真方法相比,基于硬件的仿真通常以数十或数百兆赫兹的速度运行,而软件仿真的速度往往较慢,以数十或数百千赫兹为单位,且波形转储或调试信息显示等调试选项会使得仿真速度进一步降低,整体验证效率较低。

技术实现思路

1、本发明实施例提供一种验证方法、芯片、系统、电子设备及可读存储介质,可以解决相关技术中硬件设计验证效率较低的问题。

2、为了解决上述问题,本发明实施例公开了一种验证方法,应用于可编程逻辑芯片,所述可编程逻辑芯片的可编程逻辑区域中包括设计模块、仿真模块和板载模块,所述设计模块包括硬件设计和所述硬件设计对应的功能单元;所述仿真模块包括所述设计模块和中断模块;所述板载模块包括所述仿真模块和验证模块;所述可编程逻辑芯片的处理系统中运行有所述硬件设计对应的软件设计,所述软件设计用于实现与所述硬件设计相同的功能;所述方法包括:

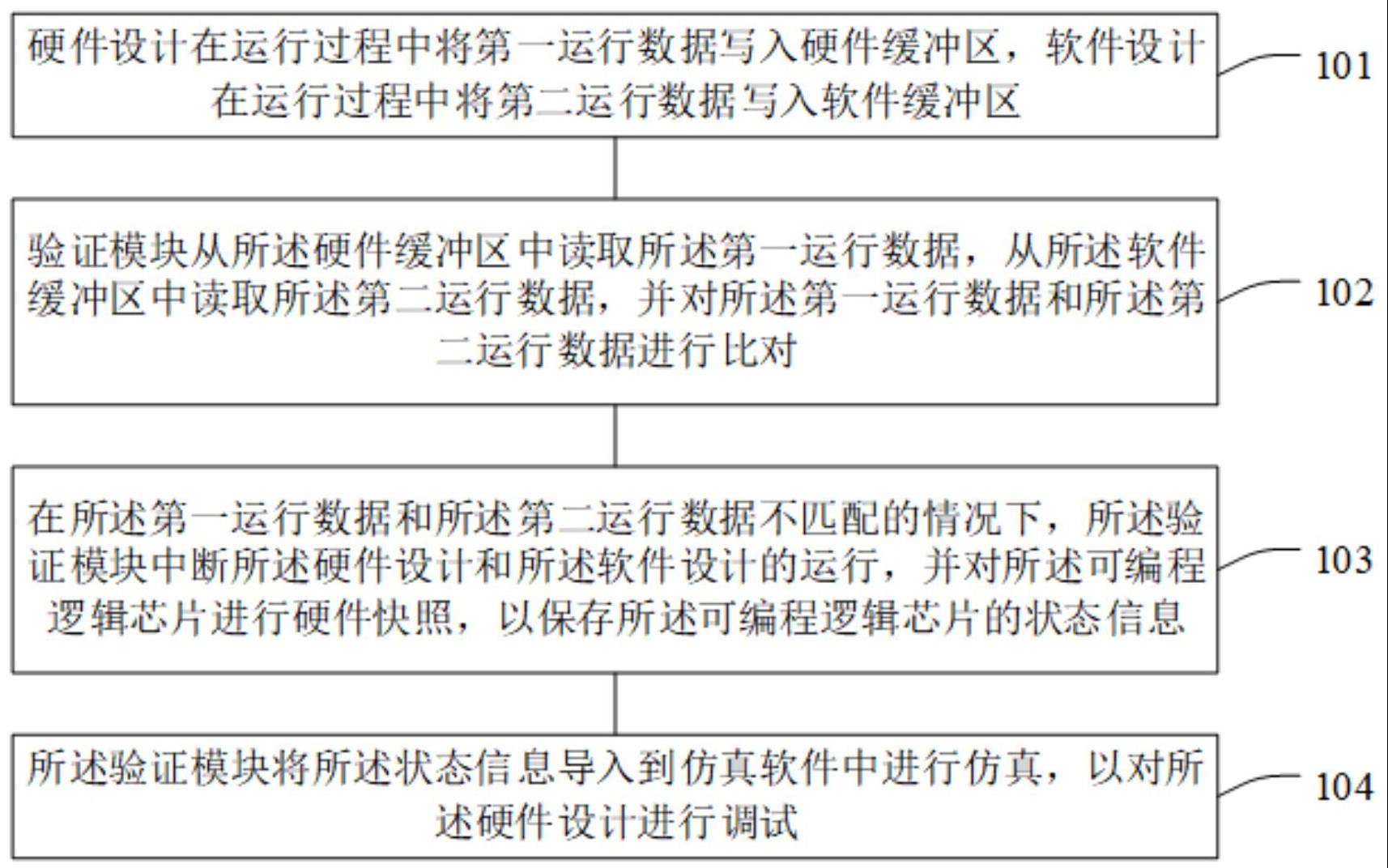

3、所述硬件设计在运行过程中将第一运行数据写入硬件缓冲区,所述软件设计在运行过程中将第二运行数据写入软件缓冲区;

4、所述验证模块从所述硬件缓冲区中读取所述第一运行数据,从所述软件缓冲区中读取所述第二运行数据,并对所述第一运行数据和所述第二运行数据进行比对;

5、在所述第一运行数据和所述第二运行数据不匹配的情况下,所述验证模块中断所述硬件设计和所述软件设计的运行,并对所述可编程逻辑芯片进行硬件快照,以保存所述可编程逻辑芯片的状态信息;

6、所述验证模块将所述状态信息导入到仿真软件中进行仿真,以对所述硬件设计进行调试。

7、另一方面,本发明实施例公开了一种可编程逻辑芯片,所述可编程逻辑芯片的可编程逻辑区域中包括设计模块、仿真模块和板载模块,所述设计模块包括硬件设计和所述硬件设计对应的功能单元;所述仿真模块包括所述设计模块和中断模块;所述板载模块包括所述仿真模块和验证模块;所述可编程逻辑芯片的处理系统中运行有所述硬件设计对应的软件设计,所述软件设计用于实现与所述硬件设计相同的功能;

8、所述硬件设计,用于在运行过程中将第一运行数据写入硬件缓冲区;

9、所述软件设计,用于在运行过程中将第二运行数据写入软件缓冲区;

10、所述验证模块,用于从所述硬件缓冲区中读取所述第一运行数据,从所述软件缓冲区中读取所述第二运行数据,并对所述第一运行数据和所述第二运行数据进行比对;在所述第一运行数据和所述第二运行数据不匹配的情况下,中断所述硬件设计和所述软件设计的运行,并对所述可编程逻辑芯片进行硬件快照,以保存所述可编程逻辑芯片的状态信息;将所述状态信息导入到仿真软件中进行仿真,以对所述硬件设计进行调试。

11、又一方面,本发明实施例还公开了一种验证系统,所述系统包括可编程逻辑芯片和个人电脑,所述个人电脑中搭载有仿真软件;所述可编程逻辑芯片的可编程逻辑区域中包括设计模块、仿真模块和板载模块,所述设计模块包括硬件设计和所述硬件设计对应的功能单元;所述仿真模块包括所述设计模块和中断模块;所述板载模块包括所述仿真模块和验证模块;所述可编程逻辑芯片的处理系统中运行有所述硬件设计对应的软件设计,所述软件设计用于实现与所述硬件设计相同的功能;

12、所述硬件设计,用于在运行过程中将第一运行数据写入硬件缓冲区;

13、所述软件设计,用于在运行过程中将第二运行数据写入软件缓冲区;

14、所述验证模块,用于从所述硬件缓冲区中读取所述第一运行数据,从所述软件缓冲区中读取所述第二运行数据,并对所述第一运行数据和所述第二运行数据进行比对;在所述第一运行数据和所述第二运行数据不匹配的情况下,中断所述硬件设计和所述软件设计的运行,并对所述可编程逻辑芯片进行硬件快照,以保存所述可编程逻辑芯片的状态信息;将所述状态信息导入到仿真软件中进行仿真,以对所述硬件设计进行调试。

15、再一方面,本发明实施例还公开了一种电子设备,所述电子设备包括处理器、存储器、通信接口和通信总线,所述处理器、所述存储器和所述通信接口通过所述通信总线完成相互间的通信;所述存储器用于存放可执行指令,所述可执行指令使所述处理器执行前述的验证方法。

16、本发明实施例还公开了一种可读存储介质,当所述可读存储介质中的指令由电子设备的处理器执行时,使得电子设备能够执行前述的验证方法。

17、本发明实施例包括以下优点:

18、综上,本发明实施例提供了一种验证方法,将硬件设计加载到fpga芯片上运行,利用fpga加速提升了验证效率;并且,在硬件设计的第一运行数据与软件设计的第二运行数据不匹配的情况下,可以通过硬件快照快速、精准地定位错误,将快照保存的状态信息导入到仿真软件中,利用仿真软件对硬件设计进行更细粒度的调试,保证了仿真的自由度和调试效率。

技术特征:

1.一种验证方法,其特征在于,应用于可编程逻辑芯片,所述可编程逻辑芯片的可编程逻辑区域中包括设计模块、仿真模块和板载模块,所述设计模块包括硬件设计和所述硬件设计对应的功能单元;所述仿真模块包括所述设计模块和中断模块;所述板载模块包括所述仿真模块和验证模块;所述可编程逻辑芯片的处理系统中运行有所述硬件设计对应的软件设计,所述软件设计用于实现与所述硬件设计相同的功能;所述方法包括:

2.根据权利要求1所述的方法,其特征在于,所述硬件设计在运行过程中将第一运行数据写入硬件缓冲区,包括:

3.根据权利要求1所述的方法,其特征在于,所述方法还包括:

4.根据权利要求1所述的方法,其特征在于,所述方法还包括:

5.根据权利要求1所述的方法,其特征在于,所述所述硬件设计在运行过程中将第一运行数据写入硬件缓冲区,所述软件设计在运行过程中将第二运行数据写入软件缓冲区,包括:

6.根据权利要求1所述的方法,其特征在于,所述方法还包括:

7.根据权利要求1所述的方法,其特征在于,所述可编程逻辑芯片还搭载有外部设备;所述硬件设计在运行过程中,通过片上总线与所述外部设备、所述功能单元、所述中断模块和所述验证模块中的任一项进行交互。

8.根据权利要求1所述的方法,其特征在于,所述功能单元包括数据存储器,所述数据存储器用于存储所述硬件设计对应的输入数据,所述硬件设计在运行过程中从所述数据存储器中读取输入数据,并对所述运行数据进行处理。

9.一种可编程逻辑芯片,其特征在于,所述可编程逻辑芯片的可编程逻辑区域中包括设计模块、仿真模块和板载模块,所述设计模块包括硬件设计和所述硬件设计对应的功能单元;所述仿真模块包括所述设计模块和中断模块;所述板载模块包括所述仿真模块和验证模块;所述可编程逻辑芯片的处理系统中运行有所述硬件设计对应的软件设计,所述软件设计用于实现与所述硬件设计相同的功能;

10.根据权利要求9所述的可编程逻辑芯片,其特征在于,所述硬件设计具体用于:

11.根据权利要求9所述的可编程逻辑芯片,其特征在于,所述中断模块用于:

12.根据权利要求9所述的可编程逻辑芯片,其特征在于,所述中断模块还用于:

13.一种验证系统,其特征在于,所述系统包括可编程逻辑芯片和个人电脑,所述个人电脑中搭载有仿真软件;所述可编程逻辑芯片的可编程逻辑区域中包括设计模块、仿真模块和板载模块,所述设计模块包括硬件设计和所述硬件设计对应的功能单元;所述仿真模块包括所述设计模块和中断模块;所述板载模块包括所述仿真模块和验证模块;所述可编程逻辑芯片的处理系统中运行有所述硬件设计对应的软件设计,所述软件设计用于实现与所述硬件设计相同的功能;

14.一种电子设备,其特征在于,所述电子设备包括处理器、存储器、通信接口和通信总线,所述处理器、所述存储器和所述通信接口通过所述通信总线完成相互间的通信;所述存储器用于存放可执行指令,所述可执行指令使所述处理器执行如权利要求1至8中任一项所述的验证方法。

15.一种可读存储介质,其特征在于,当所述可读存储介质中的指令由电子设备的处理器执行时,使得所述处理器能够执行如权利要求1至8中任一项所述的验证方法。

技术总结

本发明实施例提供一种验证方法、芯片、系统、电子设备及可读存储介质,涉及计算机技术领域,该方法包括:硬件设计在运行过程中将第一运行数据写入硬件缓冲区,软件设计在运行过程中将第二运行数据写入软件缓冲区;验证模块从硬件缓冲区中读取所述第一运行数据,从软件缓冲区中读取所述第二运行数据,并对第一运行数据和第二运行数据进行比对,在第一运行数据和第二运行数据不匹配的情况下,中断硬件设计和软件设计的运行,并对可编程逻辑芯片进行硬件快照,以保存可编程逻辑芯片的状态信息,将所述状态信息导入到仿真软件中进行仿真,以对硬件设计进行调试。本发明实施例提升了验证效率,并保证了仿真的自由度和调试效率。

技术研发人员:石侃,徐烁翔,张子卿,韩英明,翁伟杰,包云岗

受保护的技术使用者:北京开源芯片研究院

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!