FPGA自适应位宽数据传输方法、装置、设备和介质与流程

本申请涉及fpga芯片优化,特别是涉及一种fpga自适应位宽数据传输方法、装置、设备和介质。

背景技术:

1、fpga(field-programmable gate array)即现场可编程门阵列,是一种可编程的集成电路芯片,具有可编程性、并行处理 、可重构性、高效性能、低功耗、嵌入式特性和可靠性等特点。随着当代电子技术的不断发展,fpga参与的项目设计需求越来越多样化,设计复杂程度也越来越高。

2、在fpga程序设计中,数据缓存作为降低设计复杂度的手段越来越广泛的被应用到设计当中。fpga中较为常用的缓存资源有fifo(先入先出缓冲区)和ram(随机存储器)等结构。

3、然而,上述传统数据缓存存在数据传输的操作精度和带宽难以兼顾的技术问题。

技术实现思路

1、基于此,有必要针对上述技术问题,提供一种fpga自适应位宽数据传输方法、一种fpga自适应位宽数据传输装置、一种计算机设备和一种计算机可读存储介质。

2、为了实现上述目的,本发明实施例采用以下技术方案:

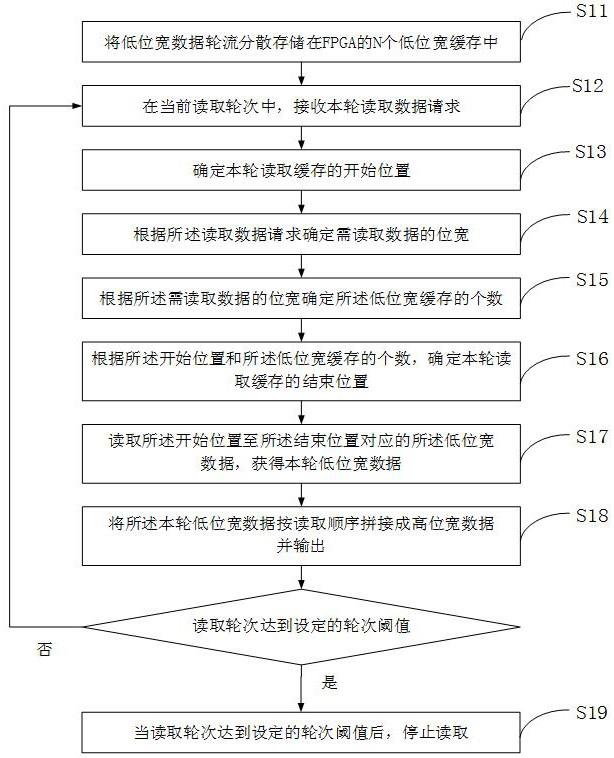

3、一方面,提供一种fpga自适应位宽数据传输方法,包括:

4、将低位宽数据轮流分散存储在fpga的n个低位宽缓存中;低位宽缓存的位宽根据低位宽接口端的位宽确定,n为高位宽接口端的位宽与低位宽接口端的位宽之比;

5、在当前读取轮次中,接收本轮读取数据请求;

6、确定本轮读取缓存的开始位置;

7、根据读取数据请求确定需读取数据的位宽;

8、根据需读取数据的位宽确定低位宽缓存的个数;

9、根据开始位置和低位宽缓存的个数,确定本轮读取缓存的结束位置;

10、读取开始位置至结束位置对应的低位宽数据,获得本轮低位宽数据;

11、将本轮低位宽数据按读取顺序拼接成高位宽数据并输出;

12、接收下一轮读取数据请求,进入下一读取轮次的读取;

13、当读取轮次达到设定的轮次阈值后,停止读取。

14、另一方面,还提供一种fpga自适应位宽数据传输装置,包括:

15、缓存模块,用于将低位宽数据轮流分散存储在fpga的n个低位宽缓存中;低位宽缓存的位宽根据低位宽接口端的位宽确定,n为高位宽接口端的位宽与低位宽接口端的位宽之比;

16、接收模块,用于在当前读取轮次中,接收本轮读取数据请求;

17、第一位置确定模块,用于确定本轮读取缓存的开始位置;

18、第一解析模块,用于根据读取数据请求确定需读取数据的位宽;

19、第二解析模块,用于根据需读取数据的位宽确定低位宽缓存的个数;

20、第二位置确定模块,用于根据开始位置和低位宽缓存的个数,确定本轮读取缓存的结束位置;

21、读取模块,用于读取开始位置至结束位置对应的低位宽数据,获得本轮低位宽数据;

22、输出模块,用于将本轮低位宽数据按读取顺序拼接成高位宽数据并输出;

23、接收模块,用于接收下一轮读取数据请求,进入下一读取轮次的读取;

24、读取终止模块,用于当读取轮次达到设定的轮次阈值后,停止读取。

25、又一方面,还提供一种计算机设备,包括存储器和处理器,存储器存储有计算机程序,处理器执行计算机程序时实现上述的fpga自适应位宽数据传输方法的步骤。

26、再一方面,还提供一种计算机可读存储介质,其上存储有计算机程序,计算机程序被处理器执行时实现上述的fpga自适应位宽数据传输方法的步骤。

27、本申请实施例中提供的一个或多个技术方案,至少具有如下技术效果或优点:

28、上述fpga自适应位宽数据传输方法、装置、设备和介质,通过将低位宽数据轮流分散存储在fpga的多个低位宽缓存中,然后根据读取数据请求读出对应数量的低位宽数据,并按读取顺序进行拼接后输出,实现了fpga不同位宽接口间高精度的数据交互,克服了直接进行位宽转换而引起的数据丢失等问题,提高了读取效率和精准性。因此,通过分散存储与按序读取的设计,打破了操作精度与带宽的常规减益关系,实现了保证操作精度的同时兼顾了速率。

29、此外,当低位宽接口向高位宽接口传递数据时,高位宽端既可以按高位宽读取数据也可以按低位宽读取数据,使这种场景下缓存两端数据流的数据交互更加精准。

技术特征:

1.一种fpga自适应位宽数据传输方法,其特征在于,包括步骤:

2.根据权利要求1所述的fpga自适应位宽数据传输方法,其特征在于,所述低位宽缓存为fifo缓存。

3.根据权利要求2所述的fpga自适应位宽数据传输方法,其特征在于,使用srio接口读取所述开始位置至所述结束位置对应的所述低位宽数据,获得本轮低位宽数据。

4.根据权利要求3所述的fpga自适应位宽数据传输方法,其特征在于,将所述本轮低位宽数据按读取顺序拼接成高位宽数据并输出的步骤,包括:

5.一种fpga自适应位宽数据传输装置,其特征在于,包括:

6.根据权利要求5所述的fpga自适应位宽数据传输装置,其特征在于,所述低位宽缓存为fifo缓存。

7.根据权利要求6所述的fpga自适应位宽数据传输装置,其特征在于,所述读取模块为srio接口。

8.根据权利要求7所述的fpga自适应位宽数据传输装置,其特征在于,所述输出模块包括:

9.一种计算机设备,包括存储器和处理器,其特征在于,所述存储器存储有计算机程序,所述处理器执行所述计算机程序时实现上述权利要求1至4任一项所述的fpga自适应位宽数据传输方法的步骤。

10.一种计算机可读存储介质,其上存储有计算机程序,其特征在于,所述计算机程序被处理器执行时实现权利要求1至4中任一项所述fpga自适应位宽数据传输方法的步骤。

技术总结

本申请涉及一种FPGA自适应位宽数据传输方法、装置、设备和介质。所述方法包括:通过将低位宽数据轮流分散存储在FPGA的多个低位宽缓存中,然后根据读取数据请求读出对应数量的低位宽数据,并按读取顺序进行拼接后输出。实现了FPGA不同位宽接口间高精度的数据交互,克服了直接进行位宽转换而引起的数据丢失等问题,提高了读取效率和精准性。

技术研发人员:王杰,胡勇

受保护的技术使用者:湖南高至科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!