数据处理电路及电子设备的制作方法

本申请涉及集成电路(integrated circuit,ic),尤其涉及一种数据处理电路及电子设备。

背景技术:

1、目前,人工智能越来越普遍地应用在各个行业和领域。作为人工智能的基础,机器需要获取有效信息。为此,机器可以获取诸如图像、语音、文字之类的数据,并基于获取的数据进行特征提取,以得到有效信息。

2、通常,特征提取可以通过中央处理器(central processing unit,cpu)、图形处理器(graphics processing unit,gpu)等硬件来实现。cpu是通用处理器,可以通过控制模块寻址访问内存以调用数据并进行处理。cpu的单个运算单元强大,善于处理单个复杂的计算任务,但是不善于处理大量的并行任务。gpu具有大量的运算单元,善于处理大规模的重复计算任务,但是不善于处理复杂的计算任务。可以看到,在特征提取的过程中,使用cpu和gpu来进行二维运算都会消耗过多的算力和功耗。

3、细胞神经网络(cellular neural networks,cnn),或称为细胞非线性网络(cellular non-linear networks,cnn),于1988年被提出并应用于人工智能。特征提取可以通过cnn来实现。cnn的应用领域包括但不限于模式识别、图像处理、全局优化。现有的cnn多是基于cpu、gpu等硬件的软件框架设计的,这就导致这些cnn的实现不仅速度缓慢,而且费用高昂。

技术实现思路

1、本申请提供一种数据处理电路及电子设备,能够提高数据处理电路进行特征提取的处理速度并降低成本。

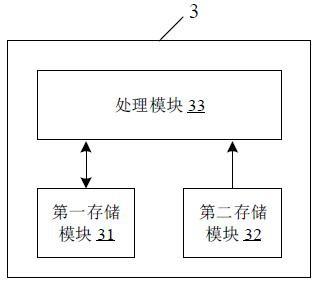

2、在第一方面,本申请提供了一种数据处理电路。该数据处理电路包括:多个cnn处理引擎。多个cnn处理引擎以环形方式连接。每个cnn处理引擎包括:第一存储模块,配置为存储第一数据,其中,第一数据采用8位浮点格式,第一数据为待处理的数据集合的一部分;第二存储模块,配置为存储第一系数,第一系数与第一数据关联;处理模块,配置为:对第一数据进行格式转换;进行转换后的第一数据和第一系数之间的卷积运算;将卷积结果转换为8位浮点格式。

3、在一些可能的实施方式中,第二存储模块还可以配置为存储第二系数。处理电路还可以配置为:获得相邻的上游cnn处理引擎输出的第二数据,其中,第二数据采用8位浮点格式;对第二数据进行格式转换;对转换后的第二数据和第二系数之间的卷积运算;将卷积结果转换为8位浮点格式。

4、在一些可能的实施方式中,处理模块可以包括:第一转换单元,配置为将第一数据转换至第一格式,其中,第一格式不同于8位浮点格式;运算单元,配置为对转换后的第一数据和第一系数之间的卷积运算;第二转换单元,配置为将卷积结果转换为8位浮点格式。

5、在一些可能的实施方式中,数据处理电路还可以包括:控制器,与多个cnn处理引擎耦合,并且配置为控制多个cnn处理引擎工作。

6、在一些可能的实施方式中,数据处理电路还可以包括:编码电路,配置为在第一存储模块存储第一数据以及第二存储模块存储第一系数之前,对第一数据和/或第一系数进行布斯编码。

7、在一些可能的实施方式中,数据处理电路还可以包括:时钟偏移电路,与多个cnn处理引擎耦合,并且配置为触发每个cnn处理引擎输出卷积结果。

8、在一些可能的实施方式中,时钟偏移电路可以包括多个d触发器。多个d触发器与多个cnn处理引擎一一对应地连接。多个d触发器中的每个d触发器被配置为触发该cnn处理引擎向相邻的下游cnn处理引擎输出卷积结果。

9、在一些可能的实施方式中,第一存储模块的存储空间的大小可以是基于第一数量和第二数量确定的。第一数量是多个cnn处理引擎的数量。第二数量是数据集合中数据的数量。

10、在一些可能的实施方式中,第二存储模块的存储空间的大小可以是基于第一数量和第三数量确定的。第一数量是多个cnn处理引擎的数量。第三数量是数据集合中关联的系数集合中系数的数量。

11、在一些可能的实施方式中,第一数据可以是大小为(m+2)×(m+2)的矩阵,第一系数可以是大小为3×3的矩阵。处理电路可以被配置为:进行第一系数与第一数据中的m2个3×3的矩阵之间的卷积运算,其中,m为正整数。

12、在一些可能的实施方式中,8位浮点格式可以包括以下之一:用于指示符号的1个比特、用于指示指数的4个比特、以及用于指示尾数的3个比特;用于指示符号的1个比特、用于指示指数的5个比特、以及用于指示尾数的2个比特。

13、在第二方面,本申请提供了一种电子设备。该电子设备可以包括:电路板;如第一方面的数据处理电路。数据处理电路位于电路板上。

14、根据本申请的技术方案,诸如图像之类的二维数据在传输和存储的过程中可以采用8位浮点格式。如此,在保证数据精度的前提下,减少了所占用的存储空间并简化了数据输出,继而提高了数据处理电路进行特征提取的效率并降低了成本。

15、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本申请。

技术特征:

1.一种数据处理电路,其特征在于,包括:

2.根据权利要求1所述的数据处理电路,其特征在于,所述第二存储模块还配置为存储第二系数;

3.根据权利要求1所述的数据处理电路,其特征在于,所述处理模块包括:

4.根据权利要求1所述的数据处理电路,其特征在于,所述数据处理电路还包括:

5.根据权利要求1所述的数据处理电路,其特征在于,所述数据处理电路还包括:编码电路,配置为在所述第一存储模块存储所述第一数据以及所述第二存储模块存储所述第一系数之前,对所述第一数据和/或所述第一系数进行布斯编码。

6.根据权利要求1所述的数据处理电路,其特征在于,所述数据处理电路还包括:

7.根据权利要求6所述的数据处理电路,其特征在于,所述时钟偏移电路包括多个d触发器,所述多个d触发器与所述多个cnn处理引擎一一对应地连接;

8.根据权利要求1所述的数据处理电路,其特征在于,所述第一存储模块的存储空间的大小是基于第一数量和第二数量确定的;

9.根据权利要求1所述的数据处理电路,其特征在于,所述第二存储模块的存储空间的大小是基于第一数量和第三数量确定的;

10.根据权利要求1所述的数据处理电路,其特征在于,所述第一数据是大小为(m+2)×(m+2)的矩阵,所述第一系数是大小为3×3的矩阵;

11.根据权利要求1所述的数据处理电路,其特征在于,所述8位浮点格式包括以下之一:

12.一种电子设备,其特征在于,包括:

技术总结

本申请提供一种数据处理电路及电子设备。该数据处理电路包括多个CNN处理引擎。多个CNN处理引擎以环形方式连接。每个CNN处理引擎包括:第一存储模块,配置为存储第一数据,其中,第一数据采用8位浮点格式,第一数据为待处理的数据集合的一部分;第二存储模块,配置为存储第一系数,第一系数与所述第一数据关联;处理模块,配置为:对第一数据进行格式转换;进行转换后的第一数据和第一系数之间的卷积运算;将卷积结果转换为8位浮点格式。在本申请中,通过将第一数据以8位浮点格式进行传输和存储,提高了数据处理电路的效率并降低了成本。

技术研发人员:彭杰,周君临,高鹏,杨林,虞惠华,门爱东,黄笑天,欧阳书平,杨晋

受保护的技术使用者:北京弘微智能技术有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!