一种近亚阈值区域MCU主控芯片电路设计方法与流程

本发明涉及电路设计,具体为一种近亚阈值区域mcu主控芯片电路设计方法。

背景技术:

1、低功耗单片机mcu(或微控制器)中,用于产生时钟信号的振荡器主要采用倍频电路和分频电路实现多种目标频率的时钟信号输出,实现功耗较高,如锁相环pll和锁频环fll等电路模块,主要功能是对原始时钟信号进行倍频操作,从而提高系统的整体时钟性能,然而与此同时功耗也会被相应提高;现有低功耗mcu中,pll和fll模块功耗较高,其主要功能是对原始时钟信号进行倍频操作,从而提高系统的整体时钟性能,与此同时其功耗也会被相应提高。通过对时钟的设计,欲实现高频时钟直接输出,仅使用高频相位锁定,有多个输出频率可选,不使用倍频,降低整体时钟系统功耗,进而降低总体mcu的功耗。

2、此外,有少数低功耗单片机mcu使用晶体振荡器,虽然晶体振荡器能提供多个可用频率,但晶体振荡器对器件要求较高,振荡频率会随环境温度、工艺、电源电压等发生改变,成本较高且适用范围很局限,从而无法满足低成本芯片设计以及高可用通信系统的要求。

3、现有时钟振荡器主要采用倍频方式,功耗较高。直接振荡对器件要求较高,振荡频率会随环境温度、工艺、电源电压等发生改变在芯片上集成lc及负阻器件可以进一步减少误差,提高一致性。

技术实现思路

1、本发明的目的在于提供一种近亚阈值区域mcu主控芯片电路设计方法,以解决上述背景技术中提出时钟振荡器主要采用倍频方式,功耗较高的问题。

2、为实现上述目的,本发明提供如下技术方案:

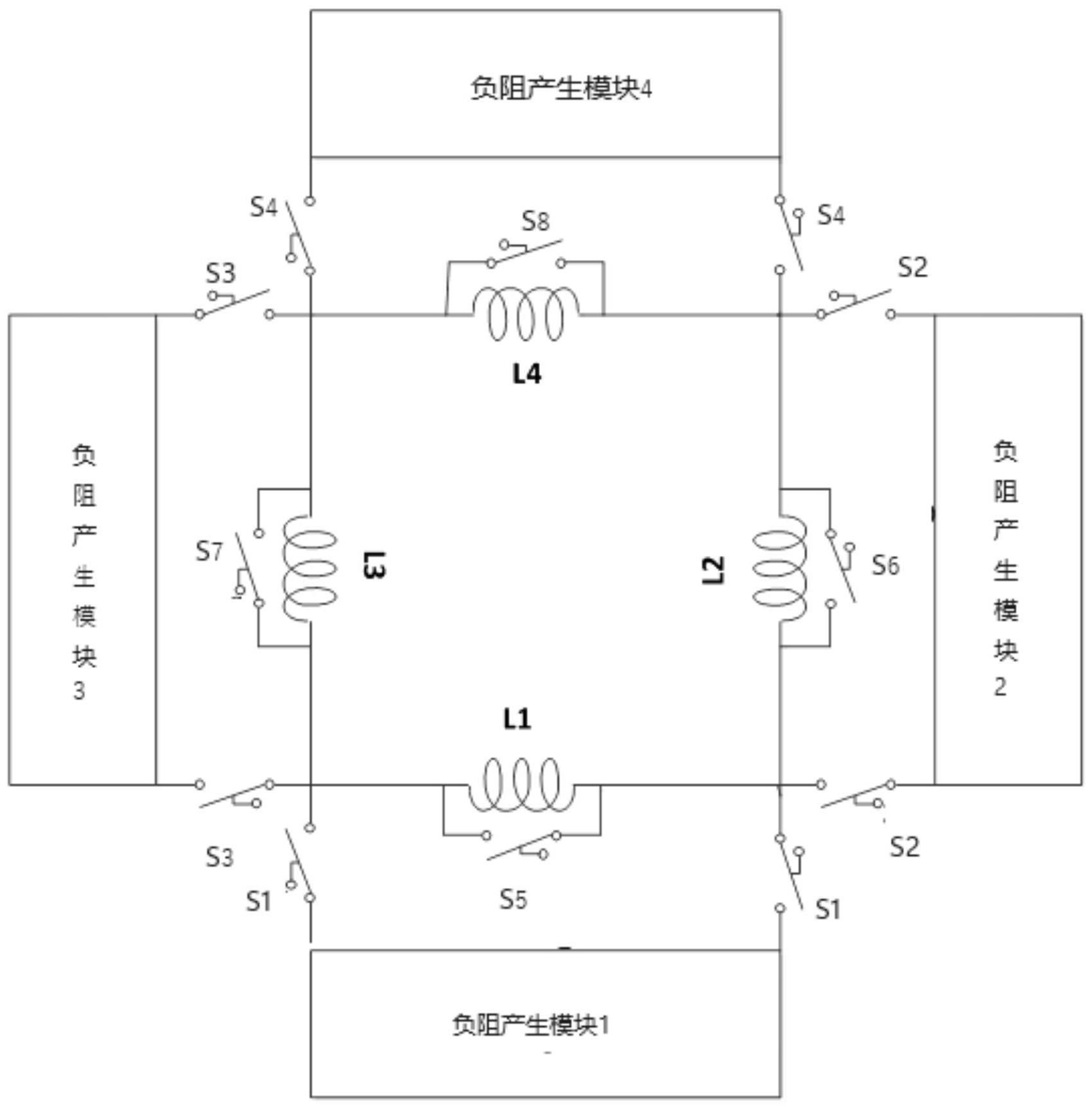

3、一种近亚阈值区域mcu主控芯片电路设计方法,包括十二组控制开关、四组负阻产生模块和四组电感模块,每组所述负阻产生模块与电感模块构成谐振回路,四个负阻产生模块、四个电感模块产生多个频率的时钟信号;

4、每组所述负阻产生模块与电感模块的两端之间均设置有控制开关,每组所述电感模块上并联一组控制开关。

5、作为优选,当选择频率时,电感和负阻模块接入电路,未选择的模块被旁路,此方式产生四个频率输出。

6、作为优选,两模块同时选通,产生六组频率输出,三模块同时选通产生四个频率输出。

7、作为优选,四模块同时接入产生最低频率输出,共有15个频率可以输出。

8、作为优选,所述fft处理器中包括16位乘法器、fir滤波器和sram单元。

9、作为优选,fft处理器在0.3v的亚阈值电压下,处理器功耗为6μw,最高工作频率为300hz。整个芯片面积为0.92mm2。

10、作为优选,fft处理器速度为标准工作电压下的0.3%,功耗为标准工作电压下的2.73%。

11、作为优选,所述乘法器包括全加器、半加器和二位比较器,通过级联的形式实现乘法器和触发器运算单元。

12、作为优选,所述sram单元采用一个简单的双稳态电路来保持一个数据位,只要电源一直加在这个电路上,sram单元一直保持所存放的数据位。

13、作为优选,所述sram具有3种工作模式:保持、读和写,当单元处于保持状态时,位值存放在单元中以备以后使用。

14、与现有技术相比,本发明的有益效果是:

15、1、本近亚阈值区域mcu主控芯片电路设计方法中,通过采用适合亚阈值电路的fft处理器架构,并针对性的建立了亚阈值的标准数字单元库,实现了应用在超低功耗领域的亚阈值fft处理器系统设计。一方面探索了超低功耗数字系统的设计流程,另一方面也对功耗敏感的应用场景中的数字系统设计提供了一个可以参考的方向。

16、2、本近亚阈值区域mcu主控芯片电路设计方法中,通过高频相位锁定现高频时钟的直接输出,可以显著降低时钟系统的功耗,进而降低mcu总体功耗。

技术特征:

1.一种近亚阈值区域mcu主控芯片电路设计方法,其特征在于:包括内置fft处理器、十二组控制开关、四组负阻产生模块和四组电感模块,每组所述负阻产生模块与电感模块构成谐振回路,四个负阻产生模块、四个电感模块产生多个频率的时钟信号;

2.根据权利要求1所述的近亚阈值区域mcu主控芯片电路设计方法,其特征在于:当选择频率时,电感和负阻模块接入电路,未选择的模块被旁路,此方式产生四个频率输出。

3.根据权利要求1所述的近亚阈值区域mcu主控芯片电路设计方法,其特征在于:两模块同时选通,产生六组频率输出,三模块同时选通产生四个频率输出。

4.根据权利要求1所述的近亚阈值区域mcu主控芯片电路设计方法,其特征在于:四模块同时接入产生最低频率输出,共有15个频率可以输出。

5.根据权利要求1所述的近亚阈值区域mcu主控芯片电路设计方法,其特征在于:所述fft处理器中包括16位乘法器、fir滤波器和sram单元。

6.根据权利要求5所述的近亚阈值区域mcu主控芯片电路设计方法,其特征在于:fft处理器在0.3v的亚阈值电压下,处理器功耗为6μw,最高工作频率为300hz,整个芯片面积为0.92mm2。

7.根据权利要求5所述的近亚阈值区域mcu主控芯片电路设计方法,其特征在于:fft处理器速度为标准工作电压下的0.3%,功耗为标准工作电压下的2.73%。

8.根据权利要求5所述的近亚阈值区域mcu主控芯片电路设计方法,其特征在于:所述乘法器包括全加器、半加器和二位比较器,通过级联的形式实现乘法器和触发器运算单元。

9.根据权利要求5所述的近亚阈值区域mcu主控芯片电路设计方法,其特征在于:所述sram单元采用一个简单的双稳态电路来保持一个数据位,只要电源一直加在这个电路上,sram单元一直保持所存放的数据位。

10.根据权利要求5所述的近亚阈值区域mcu主控芯片电路设计方法,其特征在于:所述sram具有3种工作模式:保持、读和写,当单元处于保持状态时,位值存放在单元中以备以后使用。

技术总结

本发明涉及电路设计技术领域,具体为一种近亚阈值区域MCU主控芯片电路设计方法,包括十二组控制开关、四组负阻产生模块和四组电感模块,每组负阻产生模块与电感模块构成谐振回路,四个负阻产生模块、四个电感模块产生多个频率的时钟信号;每组负阻产生模块与电感模块的两端之间均设置有控制开关。本发明通过采用适合亚阈值电路的FFT处理器架构,并针对性的建立亚阈值的标准数字单元库,实现应用在超低功耗领域的亚阈值FFT处理器系统设计。一方面探索超低功耗数字系统的设计流程,另一方面也对功耗敏感的应用场景中的数字系统设计提供一个可以参考的方向,通过高频相位锁定现高频时钟的直接输出,可以显著降低时钟系统的功耗。

技术研发人员:吉德志,邓立武,曾祥辉,段军鹏,周志新,赵兴攀,段根月,杨宇韬,李瀚云,朱文杰,蔡嘉伦,昝昊宇,宋立胜,拜之亮,杨凡

受保护的技术使用者:云南电网有限责任公司楚雄供电局

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!