一种IP核与FPGA连接的结构及方法与流程

本发明涉及现场可编程门阵列(field programmable gate array,fpga)。尤其涉及一种ip核与fpga连接的结构及方法。

背景技术:

1、目前,随着fpga的应用领域越发广泛,传统fpga中会加入专用功能的ip核以满足对特殊功能的性能要求。将ip核加入fpga通常做法为将ip核放置在fpga的某个边缘,这样放置的好处在于最大程度的保护了基本路由没有被中断,最小化因ip加入导致绕线资源绕通性能的下降。但是,将ip核放置在fpga边缘的缺点也非常明显的,如fpga边缘通常放置的是输入/输出单元,但ip核可能根本不需要与输入/输出单元相连接,同时由于ip核的存在阻断了逻辑资源与i/o之间的连接。

2、因此,如何实现ip核与fpga连接的同时,ip核既不形成对输入/输出单元与fpga之间的阻挡,又最小程度降低对绕线资源绕通的影响,是需要解决的问题。

技术实现思路

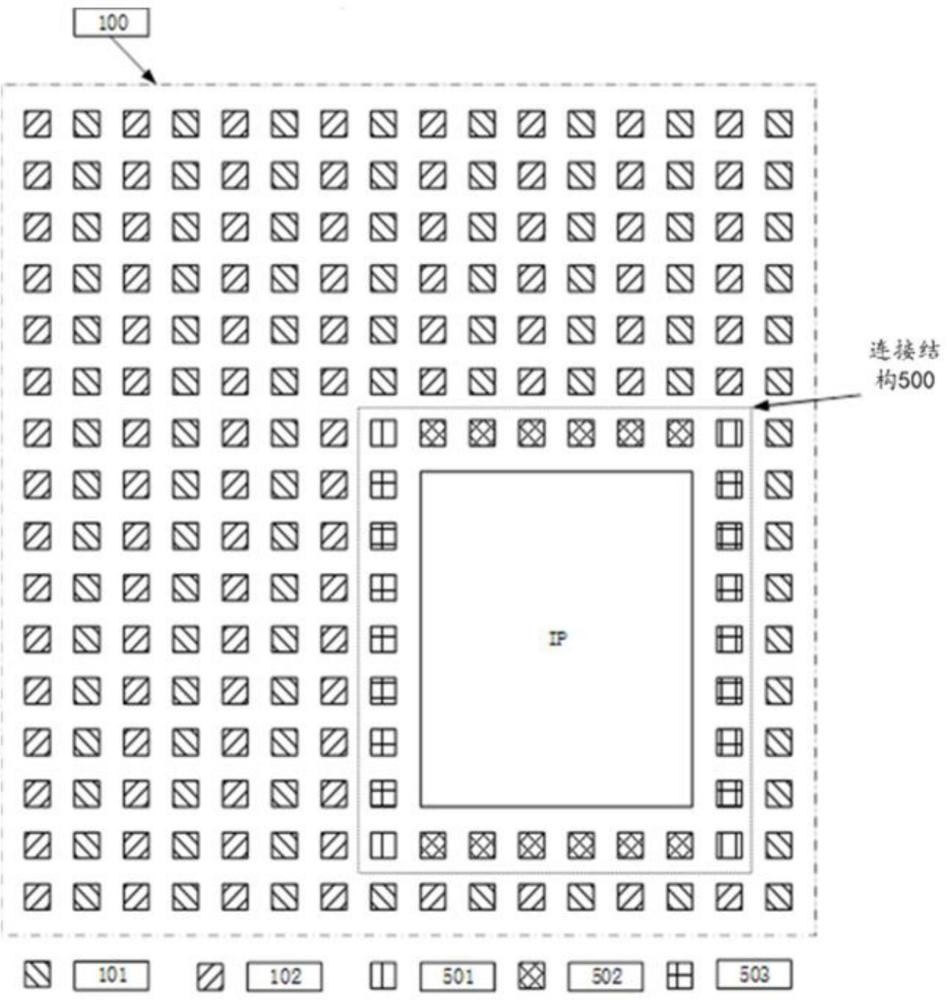

1、本申请提出一种ip核与fpga连接的结构及方法,可以解决上述问题,第一方面,本申请提出一种ip核与fpga连接的结构,应用于fpga芯片,包括若干逻辑资源模块,绕线资源模块,所述fpga芯片内部还有内嵌的至少一个ip核,其特征在于,所述ip核与所述逻辑资源模块/绕线资源模块通过连接结构连接,所述连接结构至少包括以下中的一种:第一连接模块组、第二连接模块组、第三连接模块组;所述第一连接模块组包括若干第一连接模块,所述第二连接模块组包括若干第二连接模块,所述第三连接模块组包括若干第三连接模块,所述第一连接模块组、第二连接模块组和第三连接模块组相互连接,构成所述连接结构;所述第一连接模块包括:第一垂直绕线资源模块,第一水平绕线资源模块,水平快速资源模块和第一ip连接模块;所述第二连接模块组中的各个连接模块包括:第二垂直绕线资源模块,第二水平绕线资源模块,垂直快速资源模块和第二ip连接模块;所述第三连接模块组中的各个连接模块包括:第三垂直绕线资源模块,第三水平绕线资源模块,可编程驱动缓冲模块和方向缓冲模块;信号经过所述ip核发送/接收,通过至少一个以下连接模块组:所述第一连接模块组、第二连接模块组以及第三连接模块组完成。

2、在一个实施例中,信号经过ip核发送/接收,通过至少一个以下连接模块组:所述第二连接模块组、第三连接模块组以及第一连接模块组完成,包括:所述逻辑资源模块/绕线资源模块通过任意连接模块组中连接模块的ip连接模块、水平绕线资源或者垂直绕线资源连接到所述连接结构,根据所述信号的起始地址和目标地址确定经过所述连接结构的路径;所述路径为经过所述连接结构中最少连接模块的路径;基于所述路径确定经过的所述连接模块;或者所述ip核通过任意连接模块组中连接模块的ip连接模块、水平绕线资源/垂直绕线资源连接到所述连接结构,根据所述信号的起始地址和目标地址确定经过所述连接结构的路径;所述路径为经过所述连接结构中最少连接模块的路径;基于所述路径确定经过的所述连接模块。所述信号在所述第一连接模块组内的传送过程为:从第i个第一连接模块的第一水平绕线资源模块传送到所述水平快速资源模块作用,再传送所述信号到相邻列的第i+1个第一连接模块的第一水平绕线资源模块,之后传送到水平快速资源模块作用,重复此过程直到根据所述路径确定的所述第一连接模块;所述信号在所述第二连接模块组内的传送过程为:从第i个第二连接模块的第二垂直绕线资源模块传送到所述垂直快速资源模块作用,再传送所述信号到相邻行的第i+1个第二连接模块的第二垂直绕线资源模块,之后传送到所述垂直快速资源模块作用,重复此过程直到根据所述路径确定的所述第二连接模块;所述信号在所述第三连接模块组和所述第一连接模块组/第二连接模块组之间的传送过程为:经过和所述第三连接模块相邻行/相邻列的所述第一连接模块/第二连接模块中的第一水平绕线资源/第一垂直绕线资源,传送所述信号到所述第三连接模块的第三水平绕线资源/第三垂直绕线资源,经过所述可编程驱动缓冲模块的作用,并在方向缓冲模块的作用下选择所述信号传送方向;之后通过所述第三垂直绕线资源模块/第三水平绕线资源模块输出到所述第一连接模块组/第二连接模块组。

3、在一个实施例中,所述第一/二连接模块还包括ip侧绕环回线模块,保证所述信号在所述第一垂直绕线资源模块/第二水平绕线资源模块与所述ip核相邻侧的垂直绕线闭环连接。

4、在一个实施例中,所述水平快速资源模块/垂直快速资源模块包括一组可编程驱动缓冲器和金属线。

5、在一个实施例中,所述方向缓冲模块包括若干使能缓冲器。

6、在一个实施例中,所述信号经过所述水平快速资源模块、垂直快速资源模块、可编程驱动缓冲模块加速后,所述连接机构相邻行和列的逻辑资源模块到所述连接结构的第一连接模块组或第二连接模块组的信号传输时间,和未嵌入所述ip核之前的所述信号传输时间相同,相邻行列之间的资源模块信号传输时间和未嵌入所述ip核的传输时间一致。

7、在一个实施例中,所述信号可以为从所述ip核发出传输至所述fpga芯片的任意位置。

8、在一个实施例中,所述信号可以为从所述ip核发出传输至所述fpga芯片的任意位置,包括:所述信号传输至所述连接结构,基于所述信号的起始地址和目标地址确定所述信号在所述连接结构的传输路径。

9、第二方面,本申请提出一种ip核与fpga连接的方法,应用于fpga芯片,包括若干逻辑资源模块,绕线资源模块,所述fpga芯片内部还有内嵌的至少一个ip核,其特征在于,所述ip核与所述逻辑资源模块/绕线资源模块通过连接结构连接,所述连接结构至少包括以下中的一种:第一连接模块组、第二连接模块组、第三连接模块组;所述第一连接模块组包括若干第一连接模块,所述第二连接模块组包括若干第二连接模块,所述第三连接模块组包括若干第三连接模块,所述第一连接模块组、第二连接模块组和第三连接模块组相互连接,构成所述连接结构;所述第一连接模块包括:第一垂直绕线资源模块,第一水平绕线资源模块,水平快速资源模块和第一ip连接模块;所述第二连接模块组中的各个连接模块包括:第二垂直绕线资源模块,第二水平绕线资源模块,垂直快速资源模块和第二ip连接模块;所述第三连接模块组中的各个连接模块包括:第三垂直绕线资源模块,第三水平绕线资源模块,可编程驱动缓冲模块和方向缓冲模块;信号经过所述ip核发送/接收,通过至少一个以下连接模块组:所述第一连接模块组、第二连接模块组以及第三连接模块组完成。

10、由上述技术方案可知,本申请技术方案通过设计一种ip核与fpga连接的结构和方法解决了上述问题,所述连接结构至少包括以下中的一种:水平连接结构,垂直连接结构,转角连接结构,从而将ip核内嵌于fpga芯片中,实现ip核与fpga的连接同时,既不形成对i/o与fpga之间的阻挡,又最小程度降低对绕线资源绕通的影响。

技术特征:

1.一种ip核与fpga连接的结构,应用于fpga芯片,包括若干逻辑资源模块,绕线资源模块,所述fpga芯片内部还有内嵌的至少一个ip核,其特征在于,

2.根据权利要求1所述的结构,其特征在于,信号经过ip核发送/接收,通过至少一个以下连接模块组:所述第二连接模块组、第三连接模块组以及第一连接模块组完成,包括:

3.根据权利要求1所述的结构,其特征在于,所述信号在所述第一连接模块组内的传送过程为:

4.根据权利要求1所述的结构,其特征在于,所述第一/二连接模块还包括ip侧绕环回线模块,保证所述信号在所述第一垂直绕线资源模块/第二水平绕线资源模块与所述ip核相邻侧的垂直绕线闭环连接。

5.根据权利要求1所述的结构,其特征在于,所述水平快速资源模块/垂直快速资源模块包括一组可编程驱动缓冲器和金属线。

6.根据权利要求1所述的结构,其特征在于,所述方向缓冲模块包括若干使能缓冲器。

7.根据权利要求1所述的结构,其特征在于,所述信号经过所述水平快速资源模块、垂直快速资源模块、可编程驱动缓冲模块加速后,和所述连接结构相邻行和列的逻辑资源模块到所述连接结构的第一连接模块组或第二连接模块组的信号传输时间,和未嵌入所述ip核之前的所述信号传输时间相同。

8.根据权利要求1所述的结构,其特征在于,所述信号可以为从所述ip核发出传输至所述fpga芯片的任意位置。

9.根据权利要求8所述的结构,其特征在于,所述信号可以为从所述ip核发出传输至所述fpga芯片的任意位置,包括:所述信号传输至所述连接结构,基于所述信号的起始地址和目标地址确定所述信号在所述连接结构的传输路径。

10.一种ip核与fpga连接的方法,应用于fpga芯片,包括若干逻辑资源模块,绕线资源模块,所述fpga芯片内部还有内嵌的至少一个ip核,其特征在于,

技术总结

本申请实施例公开了一种IP核与FPGA连接的结构,其特征在于,所述IP核与所述逻辑资源模块/绕线资源模块通过连接结构连接,所述连接结构至少包括以下中的一种:第一连接模块组、第二连接模块组、第三连接模块组;信号经过所述IP核发送/接收,通过至少一个以下连接模块组:所述第一连接模块组、第二连接模块组以及第三连接模块组完成。如此,实现了IP与FPGA的连接同时,既不形成对I/O与FPGA之间的阻挡,又最小程度降低对绕线资源绕通的影响。

技术研发人员:杨堃

受保护的技术使用者:京微齐力(北京)科技股份有限公司

技术研发日:

技术公布日:2024/1/25

- 还没有人留言评论。精彩留言会获得点赞!