一种基于SPIRAM的多CPU异步通信系统及方法与流程

本发明涉及异步通信领域,具体地涉及一种基于spi ram的多cpu异步通信系统及方法。

背景技术:

1、随着电力自动化的发展,对电力控制系统的要求越来越高,对于控制系统的架构、系统实时性、可靠性等提出了很高的要求。为了提高可靠性大都数系统都采用多cpu的架构,多cpu也带来了数据通信的问题,接收大量数据会频繁的打断系统的正常执行,并且导致系统的负荷加重,影响了系统任务的正常执行间隔时间。

2、目前电力行业多cpu架构通信方案有高速串口、can总线、lan以太网、usb、双端口ram等。1对多的通信方案一般采用can总线。

3、然而高速串口只能用于1对1的通信场合,并且对于不同板卡间的通信距离有要求,通信速率会随着距离增加而下降。can总线传输速率低(最高1mbps),有效载荷低导致了大数据通信的时延。lan以太网和usb对于cpu的要求高,需要较高的系统主频,在重负荷的场合会影响到系统的实时响应时间。双端口ram需要cpu的io管脚多(并口),一般用于1对1的通信场合,对于资源受限的部分cpu也无法采用。

技术实现思路

1、本发明实施例提出了一种基于spi ram的多cpu异步通信系统及方法,以改善上述问题。

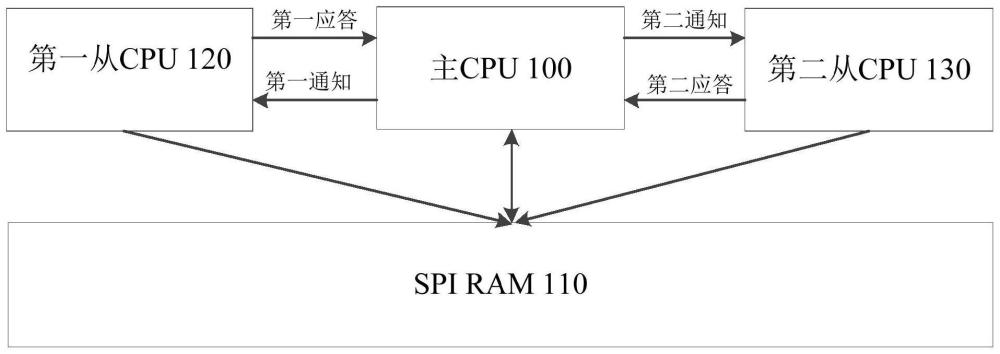

2、本发明实施例供了一种基于spi ram的多cpu异步通信系统,其包括主cpu、多个从cpu以及spi ram模组;所述主cpu以及多个从cpu均与所述spi ram模组连接;

3、所述主cpu,用于在将原始数据存储在spi ram模组后通知多个从cpu;

4、所述多个从cpu,用于在接收到所述主cpu的通知后,从spi ram模组中读取所述原始数据,并将所述原始数据转换成文件格式保存到内部的flash存储芯片。

5、优选地,所述spi ram模组包括一个spi ram,所述从cpu包括第一从cpu以及第二从cpu,则所述主cpu具体用于:

6、禁用第一从cpu以及第二从cpu对所述spi ram的操作权限;

7、获取原始数据,并将所述原始数据存储在spi ram中;

8、在将所述原始数据完全存储在spi ram后,向所述第一从cpu发送第一通知,以释放所述第一从cpu对所述spi ram的操作权限,并使得所述第一从cpu能够从spi ram中读取原始数据,将所述原始数据转换成文件格式保存到内部的flash存储芯片后,返回第一应答;

9、根据所述第一应答,向所述第二从cpu发送第二通知,以释放所述第二从cpu对所述spi ram的操作权限,并使得所述第二从cpu能够从spi ram中读取原始数据,将所述原始数据转换成文件格式保存到内部的flash存储芯片后,返回第二应答。

10、优选地,所述主cpu为交采板,所述第一从cpu为lcd板,所述第二从cpu为通信板,所述原始数据为录波数据。

11、优选地,所述spi ram模组包括与各个从cpu对应的spi ram,各个从cpu与其对应的spi ram连接,所述主cpu与各个spi ram均连接。

12、优选地,所述主cpu具体用于:

13、禁用各个从cpu对与其对应的spi ram的操作权限;

14、获取原始数据,并将所述原始数据存储在各个spi ram中;

15、在将所述原始数据完全存储在所有spi ram后,向各个从cpu发送第三通知,以释放各个从cpu对与其对应的spi ram的操作权限,并使得各个从cpu能够从对应的spi ram中读取原始数据,将所述原始数据转换成文件格式保存到内部的flash存储芯片后,返回第三应答。

16、优选地,所述spi ram为8mb的aps6404l-3sqr。

17、本发明实施例还提供了一种基于spi ram的多cpu异步通信方法,应用于如上述的基于spi ram的多cpu异步通信系统,其包括:

18、主cpu在将原始数据存储在spi ram模组后通知多个从cpu;

19、多个从cpu在接收到所述主cpu的通知后,从spi ram模组中读取所述原始数据,并将所述原始数据转换成文件格式保存到内部的flash存储芯片。

20、优选地,所述spi ram模组包括一个spi ram,所述从cpu包括第一从cpu以及第二从cpu,则主cpu在将原始数据存储在spi ram模组后通知多个从cpu具体包括:

21、禁用第一从cpu以及第二从cpu对所述spi ram的操作权限;

22、获取原始数据,并将所述原始数据存储在spi ram中;

23、在将所述原始数据完全存储在spi ram后,向所述第一从cpu发送第一通知,以释放所述第一从cpu对所述spi ram的操作权限,并使得所述第一从cpu能够从spi ram中读取原始数据,将所述原始数据转换成文件格式保存到内部的flash存储芯片后,返回第一应答;

24、根据所述第一应答,向所述第二从cpu发送第二通知,以释放所述第二从cpu对所述spi ram的操作权限,并使得所述第二从cpu能够从spi ram中读取原始数据,将所述原始数据转换成文件格式保存到内部的flash存储芯片后,返回第二应答。

25、优选地,所述spi ram模组包括与各个从cpu对应的spi ram,各个从cpu与其对应的spi ram连接,所述主cpu与各个spi ram均连接。

26、优选地,主cpu在将原始数据存储在spi ram模组后通知多个从cpu具体包括:

27、禁用各个从cpu对与其对应的spi ram的操作权限;

28、获取原始数据,并将所述原始数据存储在各个spi ram中;

29、在将所述原始数据完全存储在所有spi ram后,向各个从cpu发送第三通知,以释放各个从cpu对与其对应的spi ram的操作权限,并使得各个从cpu能够从对应的spi ram中读取原始数据,将所述原始数据转换成文件格式保存到内部的flash存储芯片后,返回第三应答。

30、综上所述,本实施例基于单/多路spi ram的异步数据交换方案,可以提高多cpu架构的通信效率,保证各个cpu执行时间可以放到更为紧急的任务上,而不是把算力浪费在通信的数据处理上。

31、本实施例通过单/多路spi ram实现了异步数据交换,在主cpu写入大量数据时从cpu去处理其他任务,等待主cpu通过信号线通知后在去spi ram读取异步数据,从而可以实现主从cpu的异步大数据通信。另外通过spi总线对比双端口ram的并口大大减少了io的使用数量。从而有效降低了cpu的采购成本,可以选用低主频、低成本的cpu来实现相应的功能。

技术特征:

1.一种基于spi ram的多cpu异步通信系统,其特征在于,包括主cpu、多个从cpu以及spi ram模组;所述主cpu以及多个从cpu均与所述spi ram模组连接;

2.根据权利要求1所述的基于spi ram的多cpu异步通信系统,其特征在于,所述spiram模组包括一个spi ram,所述从cpu包括第一从cpu以及第二从cpu,则所述主cpu具体用于:

3.根据权利要求2所述的基于spi ram的多cpu异步通信系统,其特征在于,所述主cpu为交采板,所述第一从cpu为lcd板,所述第二从cpu为通信板,所述原始数据为录波数据。

4.根据权利要求1所述的基于spi ram的多cpu异步通信系统,其特征在于,所述spiram模组包括与各个从cpu对应的spi ram,各个从cpu与其对应的spi ram连接,所述主cpu与各个spi ram均连接。

5.根据权利要求4所述的基于spi ram的多cpu异步通信系统,其特征在于,

6.根据权利要求1所述的基于spi ram的多cpu异步通信系统,其特征在于,所述spiram为8mb的aps6404l-3sqr。

7.一种基于spi ram的多cpu异步通信方法,应用于如权利要求1至6任意一项的基于spi ram的多cpu异步通信系统,其特征在于,包括:

8.根据权利要求7所述的基于spi ram的多cpu异步通信方法,其特征在于,所述spiram模组包括一个spi ram,所述从cpu包括第一从cpu以及第二从cpu,则主cpu在将原始数据存储在spi ram模组后通知多个从cpu具体包括:

9.根据权利要求7所述的基于spi ram的多cpu异步通信方法,其特征在于,所述spiram模组包括与各个从cpu对应的spi ram,各个从cpu与其对应的spi ram连接,所述主cpu与各个spi ram均连接。

10.根据权利要求9所述的基于spi ram的多cpu异步通信方法,其特征在于,

技术总结

本发明公开了一种基于SPI RAM的多CPU异步通信系统及方法,系统包括主CPU、多个从CPU以及SPI RAM模组;所述主CPU以及多个从CPU均与所述SPI RAM模组连接;所述主CPU,用于在将原始数据存储在SPI RAM模组后通知多个从CPU;所述多个从CPU,用于在接收到所述主CPU的通知后,从SPI RAM模组中读取所述原始数据,并将所述原始数据转换成文件格式保存到内部的FLASH存储芯片。本发明基于单/多路SPI RAM的异步数据交换方案,可以提高多CPU架构的通信效率,保证各个CPU执行时间可以放到更为紧急的任务上,另外通过SPI总线对比双端口RAM的并口大大减少了IO的使用数量。从而有效降低了CPU的采购成本,可以选用低主频、低成本的CPU来实现相应的功能。

技术研发人员:陈淑武,董欣运,吴建煌,刘礼慧,舒兆港

受保护的技术使用者:厦门四信智慧电力科技有限公司

技术研发日:

技术公布日:2024/2/21

- 还没有人留言评论。精彩留言会获得点赞!