支持浮点精度乘加运算的存算一体电路装置

本发明涉及存算一体领域,具体涉及一种支持浮点精度乘加运算的存算一体电路装置。

背景技术:

1、随着人工智能和万物互联技术的飞速发展,端侧设备对低功耗、高能效需求进一步提升。存算一体架构打破了传统冯诺依曼架构的“存储墙”瓶颈,消除了数据搬移开销,成为了可行的解决方案。在存算一体宏中,存储和计算单元硬件耦合,更适用于结构固定的定点数运算。然而,定点数的精度虽然能够满足推理的需求,但是如果实现线性方程组求解、神经网络训练等常见场景,还是需要浮点数的动态范围来支持。

2、浮点计算具有较高的复杂度。如图1所示,现有技术中对浮点数的乘累加运算进行计算时,需要先对输入的权重指数和激活指数做加法,再利用指数加的结果对尾数进行移位对齐,最后对移位后的尾数做定点数运算。这种先进行指数运算,再进行尾数运算的串行计算方案降低了浮点数计算的吞吐率,对存算一体读出即计算的特性并不友好。

3、当前,为了优化上述串行计算方案,预对齐是一种可行的解决方案。在fengbin tu和yiqi wang的论文“redcim:reconfigurable digital computingin-memory processorwith unified fp/int pipeline for cloudaiacceleration”中公开了一项利用预对齐方法在存算一体结构上实现浮点数乘累加的方法,如图2所示,其中对权重尾数进行了预处理,具体的处理方法和计算流程包括:对存在同一列的权重数据尾数进行移位,对齐到该列数据中的指数最大值,变成定点数之后再存储到存算一体的存储阵列中,这一部分的处理是离线进行的;输入激活部分执行单边的浮点运算,即继续在数字部分进行指数大小比较和对齐操作,对齐后将尾数送到存算一体宏中进行定点的乘累加运算。这种方案避免了对于权重指数的存储,减小了存储开销。同时,这种单边的浮点计算只需要在数字部分进行输入激活的比较对齐,避免了在存算一体结构上进行指数运算过程,把双边的浮点计算变成激活侧单边的浮点计算,消除了和存算一体不匹配的串行数据流,大大降低了计算复杂度。

4、但是,上述方案还具有较多的缺陷:第一,需要对齐好权重的尾数之后才能进行写入,预处理较为复杂;第二,由于输入激活侧的浮点计算全部依靠外围的数字逻辑实现,存算一体宏依然只支持定点数的乘累加计算,并没有真正的在存算一体架构上实现浮点计算;第三,为了利用输入激活侧的比特级稀疏性,fengbin tu等人提出的架构在输入激活侧采用了位串行的数据流,相比于位并行数据流而言,位串行需要更多的时钟周期才能完成计算,吞吐率较低;第四,由于预对齐方案在进行对齐之后,针对权重只保留有限的窗口位数,权重中的低位被丢弃,会导致推理的精度下降;第五,在动态范围很大的情况下,如线性方程组求解的场景中,预对齐会导致部分权重被直接置为0,带来的精度下降是不可忽视的,方案的鲁棒性和普适性较差。

5、综上,现有预对齐方案的浮点计算没有完全在存算一体结构上部署,并且存在权重低位舍弃导致精度下降的问题。

技术实现思路

1、本发明是为了解决上述问题而进行的,目的在于提供一种支持浮点精度乘加运算的存算一体电路装置。

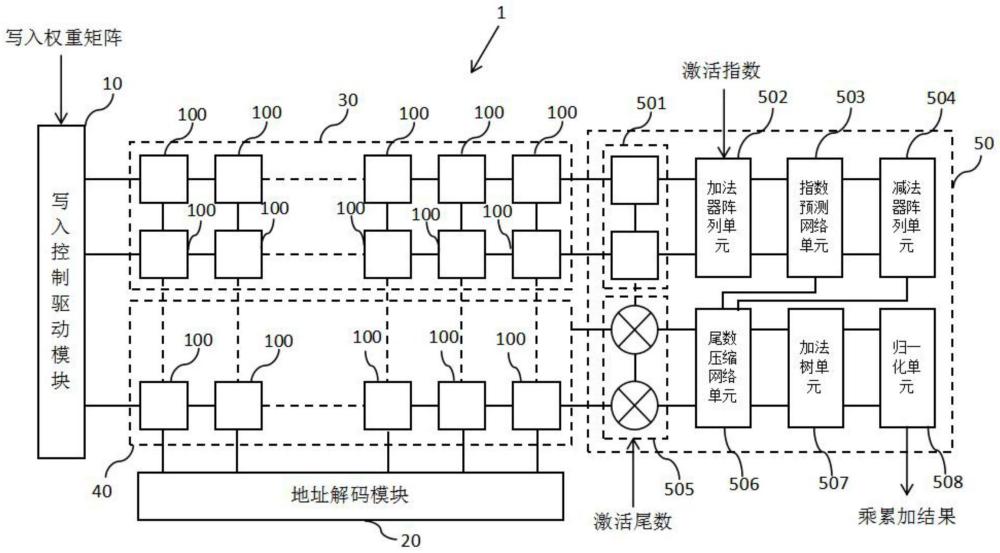

2、本发明提供了一种支持浮点精度乘加运算的存算一体电路装置,用于根据写地址、读地址、写入权重矩阵、激活指数和激活尾数计算得到乘累加结果,具有这样的特征,包括:写入控制驱动模块,用于对写入权重矩阵进行处理得到对应的非,并将写入权重矩阵和对应的非作为写入数据;地址解码模块,用于分别将写地址和读地址解码为独热码,分别得到写独热码和读独热码;指数阵列模块,包括指数存储阵列,用于根据写独热码和写入数据进行权重写入,并根据读独热码读取对应的权重指数;尾数和符号阵列模块,包括尾数和符号存储阵列,用于根据写独热码和写入数据进行权重写入,并根据读独热码读取对应的权重尾数;外围数字逻辑模块,用于根据激活指数、激活尾数、权重指数和权重尾数计算得到乘累加结果,其中,外围数字逻辑模块包括:读出单元,用于根据权重指数生成读出权重指数;加法器阵列单元,用于根据读出权重指数和激活指数进行加法运算,得到m个指数加和结果;指数预测网络单元,用于对所有指数加和结果进行处理得到控制信号、掩码和包含n个指数加和结果的加和序列;减法器阵列单元,用于将加和序列中各个指数加和结果与指数最大值进行减法运算,得到尾数移位值,指数最大值为所有指数加和结果中的最大值;尾数乘法计算单元,用于根据权重尾数、激活尾数和掩码进行乘法运算,得到m个乘法运算结果;尾数压缩网络单元,用于根据控制信号对所有乘法运算结果进行筛选和压缩,得到n个压缩后乘法运算结果;加法树单元,用于根据尾数移位值对压缩后乘法运算结果进行移位和累加运算,得到加法树输出;归一化单元,用于对加法树输出进行归一化运算,得到乘累加结果。

3、在本发明提供的支持浮点精度乘加运算的存算一体电路装置中,还可以具有这样的特征:其中,指数预测网络单元包括:控制信号和掩码生成子单元,存储有预设的双调排序算法,用于根据所有指数加和结果结合双调排序算法,得到控制信号和掩码;指数加和结果筛选子单元,用于从所有指数加和结果中筛选得到绝对值最大的n个指数加和结果;加和序列生成单元,用于根据尾数乘法计算单元输出的m个乘法运算结果中前n个最大值的排序顺序,对n个指数加和结果进行对应的重排序,得到加和序列。

4、在本发明提供的支持浮点精度乘加运算的存算一体电路装置中,还可以具有这样的特征:其中,尾数乘法计算单元包括多个计算子单元和关断控制子单元,尾数和符号存储阵列的每一行与多个计算子单元相连接,关断控制子单元用于根据掩码控制各个计算子单元的开启或关闭,计算子单元用于进行乘法运算。

5、在本发明提供的支持浮点精度乘加运算的存算一体电路装置中,还可以具有这样的特征:其中,读出单元为动态锁存器。

6、在本发明提供的支持浮点精度乘加运算的存算一体电路装置中,还可以具有这样的特征:其中,指数预测网络单元和尾数压缩网络单元均由传输管和比较器构建得到。

7、在本发明提供的支持浮点精度乘加运算的存算一体电路装置中,还可以具有这样的特征:其中,指数存储阵列和尾数和符号存储阵列均由多个基础存储单元构成,基础存储单元为8管sram单元。

8、发明的作用与效果

9、根据本发明所涉及的支持浮点精度乘加运算的存算一体电路装置,因为通过将完整的浮点乘累加计算过程映射到存算一体结构上,相较于现有的预对齐方法,避免了对所存储的权重数据复杂的预处理运算,同时也避免了由于预对齐方案丢弃权重低位数据造成的精度损失,进而可以支持更大的动态范围。所以,本发明的支持浮点精度乘加运算的存算一体电路装置能够实现存算一体结构上的完整浮点乘累加计算,并保持较好的精度。

技术特征:

1.一种支持浮点精度乘加运算的存算一体电路装置,用于根据写地址、读地址、写入权重矩阵、激活指数和激活尾数计算得到乘累加结果,其特征在于,包括:

2.根据权利要求1所述的支持浮点精度乘加运算的存算一体电路装置,其特征在于:

3.根据权利要求1所述的支持浮点精度乘加运算的存算一体电路装置,其特征在于:

4.根据权利要求1所述的支持浮点精度乘加运算的存算一体电路装置,其特征在于:

5.根据权利要求1所述的支持浮点精度乘加运算的存算一体电路装置,其特征在于:

6.根据权利要求1所述的支持浮点精度乘加运算的存算一体电路装置,其特征在于:

技术总结

本发明提供了一种支持浮点精度乘加运算的存算一体电路装置,具有这样的特征,包括写入控制驱动模块,用于对写入权重矩阵进行处理得到写入数据;地址解码模块,用于分别将写地址和读地址解码为独热码,分别得到写独热码和读独热码;指数阵列模块,包括指数存储阵列,用于根据写独热码和写入数据进行权重写入,并根据读独热码读取对应的权重指数;尾数和符号阵列模块,包括尾数和符号存储阵列,用于根据写独热码和写入数据进行权重写入,并根据读独热码读取对应的权重尾数;外围数字逻辑模块,用于根据激活指数、激活尾数、权重指数和权重尾数计算得到乘累加结果。总之,本方法能够实现存算一体结构上的完整浮点乘累加计算,并保持较好的精度。

技术研发人员:朱浩哲,张鸿懿,李梦洁,何斯琪,陈迟晓

受保护的技术使用者:复旦大学

技术研发日:

技术公布日:2024/2/19

- 还没有人留言评论。精彩留言会获得点赞!