一种基于UVM的FIFO缓冲模块的验证装置的制作方法

本发明实施例涉及测试验证,尤其涉及一种基于uvm的fifo缓冲模块的验证装置。

背景技术:

1、在传统验证方法学中,验证工程师通常需要手动编写测试环境、生成测试数据、设置时序和处理异常情况等。这样的验证方法可能会导致效率低下、测试覆盖率不足以及容易出现遗漏等问题。常见的传统验证方法学有:

2、面向测试向量的方法:这是最早期的验证方法之一,在这种方法中,验证工程师手动编写测试向量(测试输入数据),并将其应用于待测设计。然后,验证工程师会观察输出结果,并与预期结果进行比较以判断设计的正确性。这种方法的缺点是需要大量手动编写测试向量,无法有效应对复杂的设计和验证需求。

3、有向测试:这种方法中,验证工程师基于对设计的了解和经验,有针对性地编写测试用例来验证设计的特定功能。测试用例通常通过手动编写或脚本生成,以验证设计的不同路径和条件。这种方法的缺点是测试覆盖面有限,无法全面验证设计。

技术实现思路

1、本发明提供一种基于uvm的fifo缓冲模块的验证装置,以提高验证的效率和可靠性,从而为硬件设计的验证工作提供了有力支持。

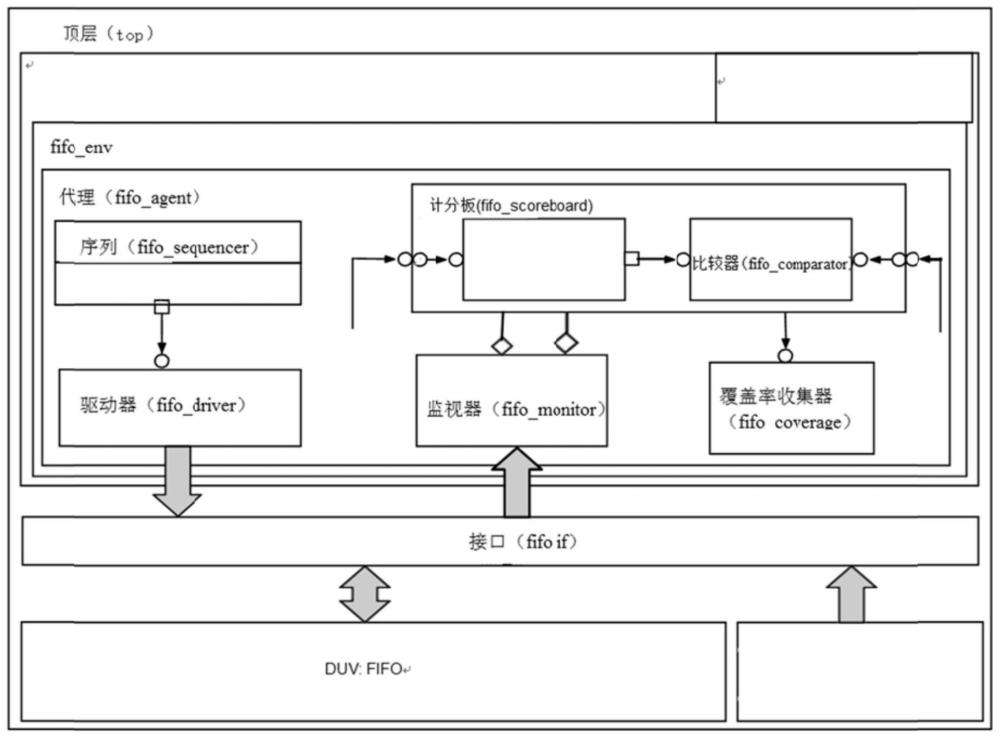

2、本发明实施例提供了一种基于uvm的fifo缓冲模块的验证装置,其特征在于,包括:

3、顶层模块,所述顶层模块用于实例化设计单元验证duv和接口,将duv和接口连接起来并定义时钟信号;

4、接口模块,所述接口模块用于定义输入输出信号的格式以及于实现总线功能模型bfm;

5、组件类模块,所述组件类模块用于初始化所述验证装置的基础架构:

6、组件类代理模块,所述组件类代理模块用于在uvm构建阶段,根据存储在uvm配置数据库中的配置对象,代理创建uvm的各个模块;

7、数据类模块,所述数据类模块用于模拟测试序列的基本项;

8、数据类序列模块,数据类序列为高级测试向量,通过数据类模块中的方法进行定义;

9、组件类驱动程序模块,所述组件类驱动程序模块用于在运行阶段执行循环,迭代地从顺序器获取一个项,并调用相应的接口bfm任务来生成适当的信号级别向量;

10、组件类监视器模块,所述组件类监视器用于通过bfm提供的任务感测duv信号。

11、可选的,所述顶层模块还用于导入uvm包以及提供对uvm配置数据库的访问,通过将接口注册到uvm配置数据库中,以允许基于类的验证装置连接到duv。

12、可选的,在读取和写入接口信号时,使用sv时钟块来构造来实现信号级时序控制。

13、可选的,所述组件类模块具体用于:

14、所述组件类模块在uvm构建阶段设置配置对象,所述配置对象用于参数化所述验证装置并将所述配置参数存储到uvm配置数据库中,以允许其他组件访问并进行自动配置。

15、可选的,所述数据类模块还用于将基本项中的项定义为无操作、写入、读取、读写或复位操作。

16、可选的,所述组件类监视器在检测到接口上的操作时会创建一个项,根据duv的时序规格,所述组件类监视器在等待一个时钟周期后将捕获的结果数据发送至记分板中的预测器和覆盖率收集器。

17、本发明的有益效果:

18、本发明通过基于uvm的测试平台方法,针对一个fifo缓冲模块构建了一个完整的testbench(测试平台)。该testbench包括了uvm的基本组件,如顺序器、驱动程序、监视器、覆盖率收集器和记分板,以及一个参考模型用于验证功能正确性。通过对测试输出的分析和覆盖率的评估,可以判断测试是否通过,并验证待验证的设计正确性和功能性。相比传统验证方法学,uvm提供了更高的可重用性、更好的抽象层次和仿真控制能力,所以该方法可以提高验证效率并加强测试环境的灵活性。在验证异步fifo等复杂模块时,uvm能够更好地管理测试复杂性,并提供丰富的功能和方法来实现全面的验证,为硬件设计的验证工作提供了有力支持。

技术特征:

1.一种基于uvm的fifo缓冲模块的验证装置,其特征在于,包括:

2.根据权利要求1所述的验证装置,其特征在于,所述顶层模块还用于导入uvm包以及提供对uvm配置数据库的访问,通过将接口注册到uvm配置数据库中,以允许基于类的验证装置连接到duv。

3.根据权利要求1所述的验证装置,其特征在于,在读取和写入接口信号时,使用sv时钟块来构造来实现信号级时序控制。

4.根据权利要求1所述的验证装置,其特征在于,所述组件类模块具体用于:

5.根据权利要求1所述的验证装置,其特征在于,所述数据类模块还用于将基本项中的项定义为无操作、写入、读取、读写或复位操作。

6.根据权利要求1所述的验证装置,其特征在于,所述组件类监视器在检测到接口上的操作时会创建一个项,根据duv的时序规格,所述组件类监视器在等待一个时钟周期后将捕获的结果数据发送至记分板中的预测器和覆盖率收集器。

技术总结

本发明公开了一种基于UVM的FIFO缓冲模块的验证装置。其中,该装置包括:顶层模块,用于实例化设计单元验证DUV和接口;接口模块,用于定义输入输出信号的格式;组件类模块,用于初始化所述验证装置的基础架构:组件类代理模块,用于代理创建UVM的各个模块;数据类模块,用于模拟测试序列的基本项;数据类序列模块,数据类序列通过数据类模块中的方法进行定义;组件类驱动程序模块,用于刺激DUV;组件类监视器模块,用于通过BFM提供的任务感测DUV信号。与现有技术相比,本发明可以提高验证效率并加强测试环境的灵活性,在验证异步FIFO等复杂模块时,UVM能够更好地管理测试复杂性,并提供丰富的功能和方法来实现全面的验证。

技术研发人员:吴杰,余向阳,蔡思聪,张磊,汪健

受保护的技术使用者:中国兵器工业集团第二一四研究所苏州研发中心

技术研发日:

技术公布日:2024/3/4

- 还没有人留言评论。精彩留言会获得点赞!