多FPGA芯片间可靠传输的通信方法与流程

本发明属于通信,更具体地说,涉及一种多fpga芯片间可靠传输的通信方法。

背景技术:

1、大规模数字芯片的验证,由于eda(电子设计自动化,electronicsdesignautomation)工具仿真验证时效上的局限性,一般会配合使用fpga(现场可编程门阵列,field-programmable gate array)芯片进行原型验证,fpga原型验证就是将asic(专用集成电路,application specific integrated circuit)的逻辑设计等价实现在fpga芯片中进行验证,相比eda仿真fpga可以实现门级并行处理,从而获得极大的时效收益。此外,大规模数字芯片的验证通常需要软硬件结合的方式,使用fpga可以给软件提供一个拥有实时反馈能力的开发平台,进一步提高电路验证的可靠性。大规模数字芯片越来越复杂,规模日益增大,这就需要资源更大的fpga芯片,但是资源丰富的fpga芯片由于技术封锁原因不易获取,因而将一个完整工程拆分放在多个fpga芯片中进行验证已经成为当下大规模设计验证中必不可少的重要手段。而要想充分发挥多fpga芯片验证的优势,首先就要找到一种可以解决跨芯片数据可靠通信的方法。

技术实现思路

1、本发明旨在提供一种多fpga芯片间可靠传输的通信方法,包括以下步骤:

2、s1.选择分割点,将目标设计分割放在多个fpga芯片中,分割后的模块分别为第n-1模块至第n模块,其中n大于等于2;

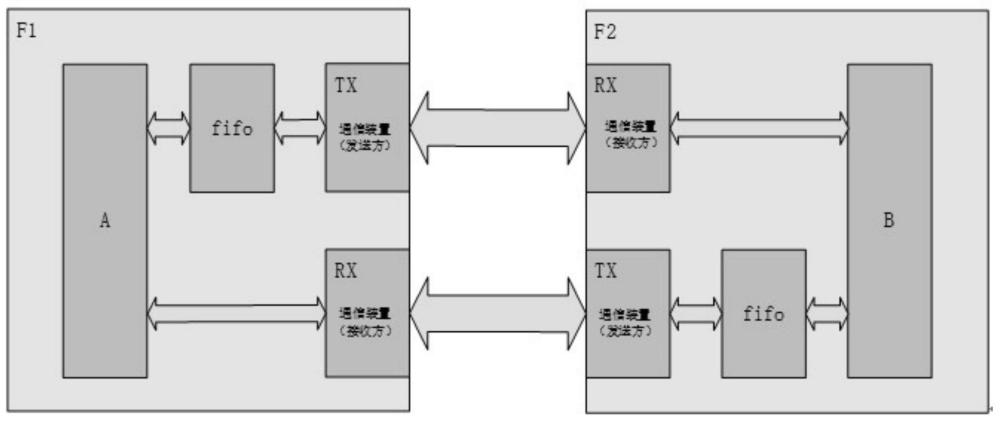

3、s2.当第n-1模块向第n模块传输数据时,在fn-1芯片中,第n-1模块将数据传输到一个fifo缓冲区中,fifo传输数据到fn-1的tx发送模块,fn-1的tx发送模块向位于fn芯片中的rx接收模块传输数据,fn芯片中的rx接收模块将数据传输第n模块;

4、当第n模块向第n-1模块传输数据时,在fn芯片中,第n模块将数据传输到一个fifo缓冲区中,fifo传输数据到fn的tx发送模块,fn的tx发送模块向位于fn-1芯片中的rx接收模块传输数据,fn-1芯片中的rx接收模块将数据传输到第n-1模块。

5、进一步的,s1中,分割点选择原则如下:

6、位于目标设计外围;

7、待传输数据相近且同时有效;

8、信号隶属于相同时钟域;

9、待传输数据位宽适中。

10、进一步的,2中发送和接收方之间采用业界通用握手通信协议,

11、信号link_rx_ready是通信装置接收方提供的ready信号,说明接收方可以接收收据;

12、信号link_tx_valid是通信装置发送方提供的valid信号,说明发送方的数据有效;

13、信号link_tx_data是通信装置发送方向接收方传输的数据;

14、当assert_on_txvalid和link_rx_ready同时为高时传输一个link_tx_data数据。

15、进一步的,s2的发送方中,信号read是通信装置发送方向fifo发出的读请求;

16、信号empty是fifo表示是否是空的状态;

17、信号user_data是fifo数据信号;

18、信号touser_valid是表示通信装置接收方传输给目的模块的数据有效;

19、信号touser_data是通信装置接收方传输到目的模块的数据;

20、计时器初始状态为0,每次握手成功link_rx_ready和link_rx_valid同时为高,完成一次传输计数器加1,将此时计数器的数值与传输数据拼接得到数据link_tx_data,其中link_rx_data,来自传输计数器,传递给接收方用作判断是哪一拍的数据,link_rx_data为需要传输的数据;由此形成的发送模块顶层接口。

21、进一步的,s2的接收方中,首先对收到的信号进行三级同步处理,信号link_tx_valid_asyn_r0是link_rx_valid同步第一级r0的输出;

22、信号link_tx_valid_asyn_r1是link_rx_valid同步第二级r1的输出;

23、信号link_tx_valid_asyn_r2是link_rx_valid同步第三级r2的输出。

24、其中判断拼接表示,将{link_tx_valid_asyn_r0,link_tx_valid_asyn_r1,link_tx_valid_asyn_r2}拼接,当其为3’b011时信号assert_on_txvalid有效,表示在接收方时钟域下的数据有效;当其为3’b110时信号dis_assert_on_txvalid表示在接收方时钟域下的数据无效;以assert_on_txvalid为起点,dis_assert_on_txvalid为终点可得信号rev_valid,在该信号有效时保存输入link_tx_data即可得到rev_data,rev_valid即为数据对应的有效信号,至此完成一个link_tx_data的接收;

25、然后分解rev_data,根据其高位rev_data所表达的数据顺序信息,通过寄存后重组恢复得到原始数据touser_data,数据对应有效信号为touser_valid。

26、根据本发明的另一方面,提供了一种计算机可读存储介质,其上存储有计算机程序,该程序被处理器执行时实现本发明的多fpga芯片间可靠传输的通信方法中的步骤。

27、根据本发明的又一方面,提供了一种计算机设备,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,所述处理器执行所述程序时实现本发明的多fpga芯片间可靠传输的通信方法中的步骤。

28、相比于现有技术,本发明至少具有如下有益效果:

29、本发明解决了实现多个fpga中芯片间互相通信。

技术特征:

1.一种多fpga芯片间可靠传输的通信方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的方法,其特征在于,s1中,分割点选择原则如下:

3.根据权利要求1所述的方法,其特征在于,s2中发送和接收方之间采用业界通用握手通信协议,

4.根据权利要求1所述的方法,其特征在于,s2的发送方中,信号read是通信装置发送方向fifo发出的读请求;

5.根据权利要求3所述的方法,其特征在于,s2的接收方中,首先对收到的信号进行三级同步处理,信号link_tx_valid_asyn_r0是link_rx_valid同步第一级r0的输出;

6.一种计算机可读存储介质,其上存储有计算机程序,其特征在于:该程序被处理器执行时实现如权利要求1~5中任一项所述的多fpga芯片间可靠传输的通信装置中的步骤。

7.一种计算机设备,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,其特征在于,所述处理器执行所述程序时实现如权利要求1~5中任一项所述的多fpga芯片间可靠传输的通信装置中的步骤。

技术总结

本发明公开了一种多FPGA芯片间可靠传输的通信方法,所述方法包括如下步骤:S1.选择分割点,将目标设计分割放在多个FPGA芯片中,分割后的模块分别为第N‑1模块至第N模块,其中N大于等于2;S2.当第N‑1模块向第N模块传输数据时,在F<subgt;N‑1</subgt;芯片中,第N‑1模块将数据传输到一个FIFO缓冲区中,FIFO传输数据到F<subgt;N‑1</subgt;的TX发送模块,F<subgt;N‑1</subgt;的TX发送模块向位于F<subgt;N</subgt;芯片中的RX接收模块传输数据,F<subgt;N</subgt;芯片中的RX接收模块将数据传输第N模块。本发明能够实现多个FPGA芯片间的数据可靠传输通信。

技术研发人员:钱家祥,石小刚

受保护的技术使用者:智绘微电子科技(南京)有限公司

技术研发日:

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!