芯片测试方法、系统、设备及存储介质与流程

本申请涉及芯片,尤其涉及一种芯片测试方法、系统、设备及存储介质。

背景技术:

1、随着芯片相关技术的飞速发展,芯片使用的通讯方式也在不断增加,有常规半双工的i2c协议、全双工的spi协议,或者是某一芯片厂家的专用通讯协议等等。

2、为了保证芯片的质量,防止存在功能缺陷的芯片流入市场,通常需要在芯片正式投入使用之前利用测试仪连接芯片的测试引脚进行芯片测试。在芯片测试中,不同的通讯协议用到的芯片引脚的数量不同,例如i2c协议使用芯片的两个引脚、spi协议使用芯片的4个引脚。

3、在相关方案中,为了满足芯片测试的需求,通常会选择在芯片上设置多个引脚,但是此种方式会导致芯片的引脚过多,造成芯片体积较大,对芯片的小型化造成了阻碍。

技术实现思路

1、本申请实施例提供了一种芯片测试方法、系统、设备及存储介质,可以解决如何利用更少的芯片引脚来进行芯片测试的技术问题。

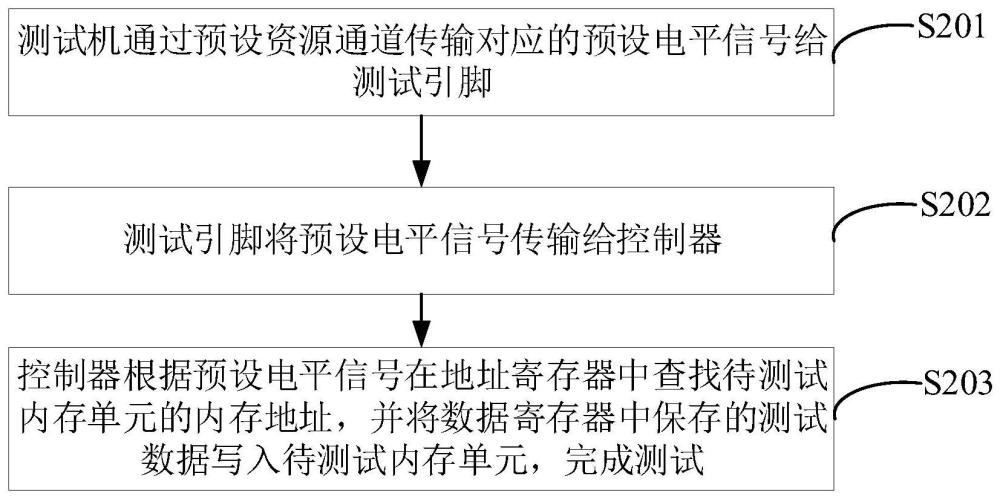

2、第一方面,本申请实施例提供了一种芯片测试方法,包括芯片和测试机,芯片与测试机相连,芯片包括:测试引脚、控制器、地址寄存器和数据寄存器,其中,

3、测试机通过预设资源通道传输对应的预设电平信号给测试引脚,测试引脚与预设资源通道短接,测试引脚为单个一次性可编程引脚,预设资源通道包括:第一资源通道、第二资源通道和第三资源通道,预设电平信号用于指示芯片进行数据读写操作。也就是说,通过将测试引脚与三个不同的资源通道短接,可以在芯片测试的过程中只占用一个引脚就能实现多种电平信号的接收,并使芯片中的控制器根据接收到的电平信号控制各寄存器来进行相关的数据读写操作,减少了测试引脚的个数,优化了测试流程。

4、测试引脚将预设电平信号传输给控制器。

5、控制器根据预设电平信号在地址寄存器中查找待测试内存单元的内存地址,并将数据寄存器中保存的测试数据写入待测试内存单元,完成测试。

6、在一个实施例中,测试机通过预设资源通道传输对应的预设电平信号给测试引脚,包括:

7、测试机通过第一资源通道传输第一电平信号,第一电平信号用于指示地址寄存器进行自加。该步骤可以确定待测试内存单元对应的内存地址。

8、在一个实施例中,测试机通过预设资源通道传输对应的预设电平信号给测试引脚,包括:

9、测试机通过第二资源通道传输第二电平信号,第二电平信号用于指示数据寄存器进行自加。该步骤可以确定需要在待检测内存单元中保存的测试数据。

10、在一个实施例中,测试机通过预设资源通道传输对应的预设电平信号给测试引脚,包括:

11、测试机通过第三资源通道传输第三电平信号,第三电平信号用于指示控制器将测试数据写入待测试内存单元。

12、在一个实施例中,测试机根据预设传输策略确定预设资源通道传输预设电平信号的传输顺序。

13、预设资源通道按照传输顺序依次向测试引脚传输预设电平信号。

14、第二方面,本申请实施例提供了一种芯片测试系统,该系统具有实现第一方面或其任意可能的实现方式中的方法的功能。具体地,该系统包括实现第一方面或其任意可能的实现方式中的方法的单元。

15、在其中的一个实施例中,该系统包括:

16、芯片和测试机,芯片与测试机相连,其中,

17、芯片包括:测试引脚、控制器、地址寄存器和数据寄存器,测试引脚用于接收测试机传输的测试信息,控制器用于控制芯片的读写操作,地址寄存器用于存储待测试内存单元的地址,数据寄存器用于存储待测试数据。

18、测试机包括:第一资源通道、第二资源通道和第三资源通道。

19、第一资源通道用于传输选择待测试内存单元的地址对应的预设电平信号,第二资源通道用于传输选择待测试数据对应的预设电平信号,第三资源通道用于传输将待测试数据写入待测试内存单元对应的预设电平信号。

20、在一个实施例中,测试引脚的个数为单个。

21、在一个实施例中,测试引脚与第一资源通道、第二资源通道和第三资源通道短接。

22、第三方面,本申请实施例提供了一种计算机设备,包括存储器、处理器以及存储在所述存储器中并可在所述处理器上运行的计算机程序,该处理器执行计算机程序时,使得计算机设备实现上述第一方面任意一种实现方式的方法。

23、第四方面,本申请实施例提供了一种计算机可读存储介质,计算机可读存储介质存储有计算机程序,计算机程序被计算机设备执行时,使得计算机设备实现上述第一方面任意一种实现方式的方法。

24、第五方面,本申请实施例提供了一种计算机程序产品,当计算机程序产品在计算机设备上运行时,使得计算机设备执行上述第一方面任意一种实现方式的方法。

25、本申请实施例与现有技术相比存在的有益效果是:在芯片测试的过程中,利用一个一次性可编程引脚同时与测试机的三个资源通道短接来进行通信,也就是说,只使用一个引脚就能接收测试机中三个不同的资源通道中传输的各种高低不一的电平信号,芯片中的控制器根据接收到的电平信号控制各寄存器来高效便捷地执行芯片测试中的相关数据读写操作,相比于采用多个测试引脚来进行芯片测试,此种方式可以大幅度减少芯片测试中使用的测试引脚的个数,提升了芯片测试的效率,降低了芯片测试的复杂度,也有利于芯片小型化。

技术特征:

1.一种芯片测试方法,其特征在于,包括芯片和测试机,所述芯片与所述测试机相连,所述芯片包括:测试引脚、控制器、地址寄存器和数据寄存器,其中,

2.根据权利要求1所述的方法,其特征在于,所述测试机通过所述预设资源通道传输对应的预设电平信号给所述测试引脚,包括:

3.根据权利要求1所述的方法,其特征在于,所述测试机通过所述预设资源通道传输对应的预设电平信号给所述测试引脚,包括:

4.根据权利要求1所述的方法,其特征在于,所述测试机通过所述预设资源通道传输对应的预设电平信号给所述测试引脚,包括:

5.根据权利要求2-4中任一项所述的方法,其特征在于,所述方法还包括:

6.一种芯片测试系统,其特征在于,包括芯片和测试机,所述芯片与所述测试机相连,其中,

7.根据权利要求6所述的芯片测试系统,其特征在于,所述测试引脚的个数为单个。

8.根据权利要求7所述的芯片测试系统,其特征在于,所述测试引脚与所述第一资源通道、第二资源通道和所述第三资源通道短接。

9.一种计算机设备,其特征在于,包括存储器、处理器以及存储在所述存储器中并可在所述处理器上运行的计算机程序,所述处理器执行所述计算机程序时,使得所述计算机设备实现如权利要求1至5中任一项所述的方法。

10.一种计算机可读存储介质,其特征在于,所述计算机可读存储介质存储有计算机程序,所述计算机程序被计算机设备执行时实现如权利要求1至5中任一项所述的方法。

技术总结

本申请适用于芯片技术领域,提供了一种芯片测试方法、系统、设备及存储介质,该方法包括:包括芯片和测试机,测试机通过预设资源通道传输对应的预设电平信号给测试引脚,测试引脚与预设资源通道短接,测试引脚为单个一次性可编程引脚,预设资源通道包括:第一资源通道、第二资源通道和第三资源通道,测试引脚将预设电平信号传输给控制器;控制器根据预设电平信号在地址寄存器中查找待测试内存单元的内存地址,并将数据寄存器中保存的测试数据写入待测试内存单元。该方案通过使用一个引脚接收测试机中三个不同的资源通道中传输的高低不一的电平信号,有效地减少了测试引脚的数量,优化了芯片测试过程。

技术研发人员:陈志祥,孔晓琳,王健,云星

受保护的技术使用者:珠海芯试界半导体科技有限公司

技术研发日:

技术公布日:2024/6/11

- 还没有人留言评论。精彩留言会获得点赞!