一种单总线设备及其控制方法与流程

本发明属于单总线通信,更具体的说,本发明涉及一种单总线设备及其控制方法。

背景技术:

1、单总线即one-wire总线,是美国dallas公司推出的外围扩展总线技术。与spi、i2c串行数据通信方式不同,它采用单根信号线,即传输时钟又传输数据,而且数据传输是双向的,具有节省i/o口(输入/输出接口)资源、资源结构简单、成本低廉、便于总线扩展和维护等诸多优点。

2、目前单总线的使用方式仅于单主机系统,即一个主机(master)能够控制一个或多个从器件(slave)。传统单总线的应用场景如图4所示。单总线的从器件主要有数字温度传感器(如ds18b20)、dht11、a/d转换器(如ds2450)、单总线控制器(如ds1wm)等,且读取这些器件的数据,往往具有固定的周期。单总线的数据传输速率一般为16.3kbit/s,最大可达142kbit/s,通常情况下采用100kbit/s以下的速率传输数据。

3、单总线设计之初就是应用于单主机系统,即一个主机对多个从器件,并不能用于两个主机控制到一个从器件的应用场景,即二个主机对一个从器件,但在一些产品上往往有二个主机对一个从器件的需求。如果不将单主机的应用方案进行升级,将无法满足这些应用场景。

技术实现思路

1、本发明的一个目的是解决至少上述问题和/或缺陷,并提供至少后面将说明的优点。

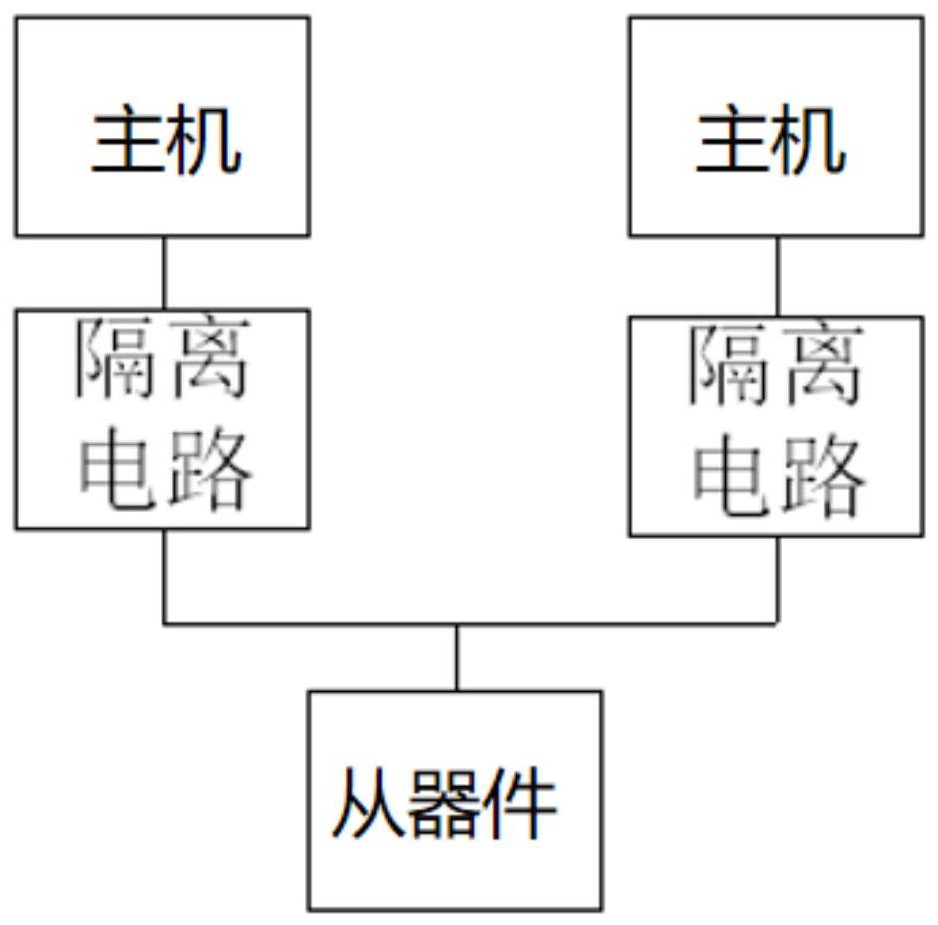

2、为了实现本发明的这些目的和其它优点,提供了一种单总线设备,包括从器件;

3、两个单总线隔离电路,其一端分别与所述从器件通信连接;

4、用于时分交替工作的两个主机,其分别具有处理器,且两个所述主机分别与两个所述单总线隔离电路电连接,两个所述处理器分别与两个所述单总线隔离电路的另一端通信连接。

5、优选的是,其中,所述单总线隔离电路包括:

6、场效应晶体管,其1脚与所述主机的电源vcc连接,所述场效应晶体管的2脚通过单总线ⅰ与所述处理器通信连接,所述场效应晶体管的3脚通过单总线ⅱ与所述从器件通信连接;

7、上拉电阻,其一端与所述主机的电源vcc连接,所述上拉电阻的另一端与所述单总线ⅰ连接。

8、优选的是,其中,所述处理器设置为cpu、mcu中的任意一种。

9、一种单总线设备的控制方法,包括以下步骤:

10、s1、确认两个主机的单总线对从器件的单次读写时间t;

11、s2、根据s1中的单次读写时间t,交替设置两个主机中a主机和b主机对从器件的间隔读写时间;

12、s3、根据从器件的波动误差范围,设定a主机和b主机的误差范围门限值,并根据a主机间隔读写时间与b主机间隔读写时间的最小公倍数,设定容错机制;

13、s4、设定读取数据不成功的告警门限。

14、优选的是,其中,s2中交替设置a主机和b主机对从器件的间隔读写时间的方法为:

15、设定a主机对从器件的间隔读写时间为mt,b主机对从器件的间隔读写时间为nt;

16、且m、n为大于4的正整数,m、n不相等且不能互相整除。

17、优选的是,其中,s3中设定容错机制的方法为:

18、a主机或b主机连续3~5次读取数据的误差不超过误差范围门限值,则认定读取的数据值稳定且有效,上报a主机或b主机的应用层;否则数据无效,丢弃数据。

19、优选的是,其中,s4中告警门限的范围为10~50次。

20、本发明至少包括以下有益效果:

21、本发明,通过两个主机时分交替工作对从器件进行数据读取,并通过单总线隔离电路隔绝任一主机关机时,对另一主机与从设备的通信影响,满足了二个主机对一个从器件的应用场景需求。

22、本发明的其它优点、目标和特征将部分通过下面的说明体现,部分还将通过对本发明的研究和实践而为本领域的技术人员所理解。

技术特征:

1.一种单总线设备,包括从器件,其特征在于:

2.根据权利要求1所述的单总线设备,其特征在于,所述单总线隔离电路包括:

3.根据权利要求1所述的单总线设备,其特征在于,所述处理器设置为cpu、mcu中的任意一种。

4.一种根据权利要求1~3任一项所述的单总线设备的控制方法,其特征在于,包括以下步骤:

5.根据权利要求4所述的单总线设备的控制方法,其特征在于,s2中交替设置a主机和b主机对从器件的间隔读写时间的方法为:

6.根据权利要求4所述的单总线设备的控制方法,其特征在于,s3中设定容错机制的方法为:

7.根据权利要求4所述的单总线设备的控制方法,其特征在于,s4中告警门限的范围为10~50次。

技术总结

本发明公开了一种单总线设备及其控制方法,包括从器件,两个单总线隔离电路,其一端分别与所述从器件通信连接;用于时分交替工作的两个主机,其分别具有处理器,且两个所述主机分别与两个所述单总线隔离电路电连接,两个所述处理器分别与两个所述单总线隔离电路的另一端通信连接。本发明,通过两个主机时分交替工作对从器件进行数据读取,并通过单总线隔离电路隔绝任一主机关机时,对另一主机与从设备的通信影响,满足了二个主机对一个从器件的应用场景需求。

技术研发人员:廖鹏,赵全鑫,薛俊层,包兴富,杜仕刚,王沛君,陈家根

受保护的技术使用者:四川灵通电讯有限公司

技术研发日:

技术公布日:2024/3/5

- 还没有人留言评论。精彩留言会获得点赞!