存算一体芯片架构、封装方法以及装置与流程

本公开涉及存算一体芯片,尤其涉及存算一体芯片架构、存算一体芯片的封装方法以及装置。

背景技术:

1、通常计算机运行的冯诺依曼体系结构包括分离的存储器和处理器两部分。执行指令时,需要将数据写入存储器,并经由处理器按照顺序从存储器中读取指令和数据,最终将执行结果写回存储器中。相应地,数据在处理器与存储器之间频繁传输。如果存储器的传输速度无法匹配处理器的运行速度,则会导致处理器的计算能力受到限制。例如,处理器执行一个指令所需时间为1ns,而从存储器读取并传输该指令所需时间为10ns,这将大幅降低处理器的运行速度,进而降低了整个计算系统的性能。

2、在此部分中描述的方法不一定是之前已经设想到或采用的方法。除非另有指明,否则不应假定此部分中描述的任何方法仅因其包括在此部分中就被认为是现有技术。类似地,除非另有指明,否则此部分中提及的问题不应认为在任何现有技术中已被公认。

技术实现思路

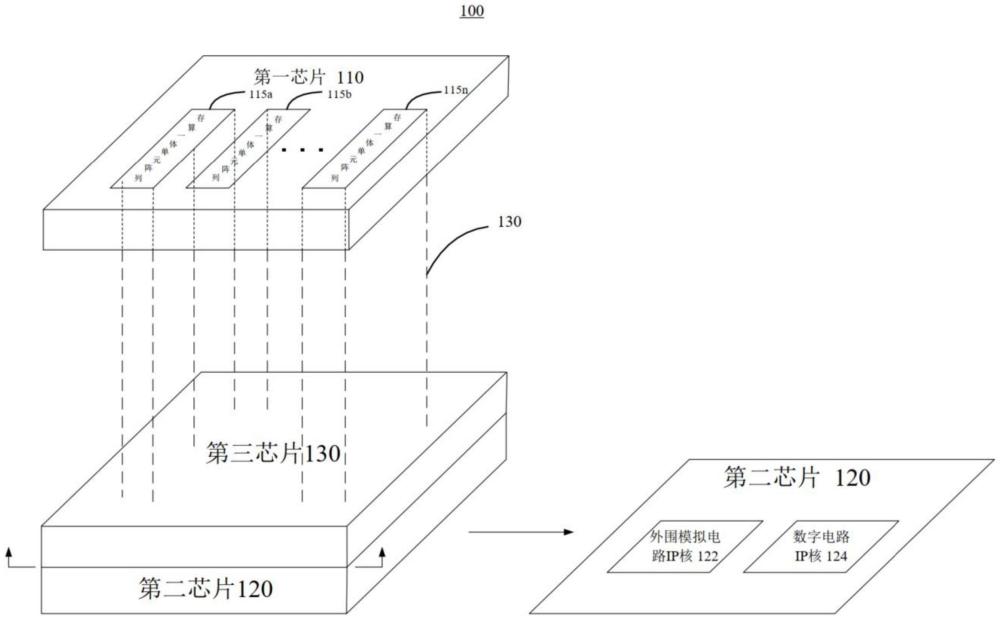

1、根据本公开的第一方面,提供了一种存算一体芯片架构,包括:一个或多个第一芯片,该一个或多个第一芯片中的每个第一芯片上集成有存算一体芯片的一个或多个存算一体单元阵列,该一个或多个存算一体单元阵列用于对接收到的数据进行计算;第二芯片,该第二芯片上集成有存算一体芯片的外围模拟电路ip核与数字电路ip核;第三芯片,该第三芯片位于该一个或多个第一芯片与该第二芯片之间,并且该第三芯片上集成有动态随机存取存储器dram;以及接口模块,接口模块被配置为通信地耦接该一个或多个第一芯片、第二芯片和第三芯片,以使得一个或多个第一芯片和第二芯片能够分别访问该dram存储的数据。

2、根据本公开的第二方面,提供了一种存算一体芯片的封装方法,包括:将存算一体芯片的一个或多个存算一体单元阵列集成于一个或多个第一芯片上,该一个或多个存算一体单元阵列用于对接收到的数据进行计算;将存算一体芯片的外围模拟电路ip核与数字电路ip核集成于第二芯片上;将动态随机存取存储器dram集成于第三芯片上,该第三芯片位于一个或多个第一芯片与第二芯片之间;以及封装该一个或多个第一芯片、第二芯片和第三芯片,其中,该一个或多个第一芯片与第二芯片能够分别访问该dram存储的数据。

3、根据本公开的第三方面,提供了一种装置,包括上述存算一体芯片架构。

4、根据本公开的一个或多个实施例,通过在存算一体单元阵列与外围模拟电路ip核和数字电路ip核之间设置动态随机存取存储器dram,可以有效缓解存算一体单元阵列计算数据量过大(例如,尤其在第一芯片数量较多的情况下)而与逻辑芯片(即第二芯片)通信速率较低的情况,有利于实现芯片之间数据的高速传输。

5、根据本公开的另外一个或多个实施例,由于不同芯片的生产工艺和良率可能不同,通过将存算一体芯片的存算一体单元阵列、外围模拟电路ip核与数字电路ip核、以及dram分别集成于不同的芯片上,有利于提高存算一体芯片封装的良率以及故障检测。

6、根据在下文中所描述的实施例,本公开的这些和其它方面将是清楚明白的,并且将参考在下文中所描述的实施例而被阐明。

技术特征:

1.一种存算一体芯片架构,包括:

2.根据权利要求1所述的存算一体芯片架构,其中,所述接口模块包括硅通孔tsv结构。

3.根据权利要求1或2所述的存算一体芯片架构,其中,所述外围模拟电路ip核包括以下中的一个或多个:

4.根据权利要求1或2所述的存算一体芯片架构,其中,所述外围模拟电路ip核包括一个或多个模块,并且

5.根据权利要求3所述的存算一体芯片架构,其中,所述数字电路ip核包括以下中的一个或多个:

6.根据权利要求1或5所述的存算一体芯片架构,其中,所述数字电路ip核包括一个或多个模块,并且

7.一种存算一体芯片的封装方法,包括:

8.根据权利要求7所述的封装方法,其中,所述一个或多个第一芯片中的每个第一芯片、所述第二芯片以及所述第三芯片之间经由硅通孔tsv结构通信地耦接。

9.根据权利要求7所述的封装方法,其中,将所述存算一体芯片的一个或多个存算一体单元阵列集成于所述一个或多个第一芯片上包括:通过第一工艺节点将所述一个或多个存算一体单元阵列分别集成于所述一个或多个第一芯片中的每个第一芯片上,

10.一种装置,包括根据权利要求1-6中任一项所述的存算一体芯片架构。

技术总结

本公开涉及存算一体芯片技术领域,尤其涉及存算一体芯片架构、存算一体芯片的封装方法以及装置。该存算一体芯片架构包括:一个或多个第一芯片,该一个或多个第一芯片中的每个第一芯片上集成有存算一体芯片的一个或多个存算一体单元阵列,该一个或多个存算一体单元阵列用于对接收到的数据进行计算;第二芯片,该第二芯片上集成有存算一体芯片的外围模拟电路IP核与数字电路IP核;第三芯片,该第三芯片位于该一个或多个第一芯片与该第二芯片之间,并且该第三芯片上集成有动态随机存取存储器DRAM;以及接口模块,接口模块被配置为通信地耦接该一个或多个第一芯片、第二芯片和第三芯片,以使得一个或多个第一芯片和第二芯片能够分别访问该DRAM存储的数据。

技术研发人员:田豫,郭昕婕,孙旭光

受保护的技术使用者:北京知存科技有限公司

技术研发日:

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!