内存速率提高装置、方法、设备和存储介质与流程

本申请涉及内存,特别是涉及一种内存速率提高装置、方法、设备和存储介质。

背景技术:

1、内存是计算机的重要部件,也称内存储器和主存储器,它用于暂时存放cpu(central processing unit,中央处理器)中的运算数据,以及与硬盘等外部存储器交换的数据。bios是计算机系统的基本输入输出系统,它是固化在计算机主板上的一段软件代码。在计算机启动时,bios负责初始化硬件设备,并加载操作系统到内存中,bios会将操作系统和其他必要的软件从辅助存储器加载到内存中,并在程序执行期间持续存储程序需要的数据和指令,最后将控制权交给操作系统。

2、dram是内存颗粒,也被称为dram芯片,是存储数据位的微小硅片。内存颗粒是随机存储器的核心组成部分,它们提供了额外的存储空间以支持计算机中的各种应用程序和进程。随着计算机科技的不断发展,内存颗粒的存储容量和速度也不断提高。内存控制器(memory controller)是计算机系统内部控制内存并且通过内存控制器使内存与cpu之间交换数据的重要组成部分。内存控制器决定了计算机系统所能使用的最大内存容量、内存bank数、内存类型和速度、内存颗粒数据深度和数据宽度等等重要参数。

3、然而,dram颗粒数据速率一般会低于cpu memory control数据传输速率。因而dram颗粒数据速率限制了整个ddr(double data rate,双倍速率)通道速率。现有技术中通过内存条中dram颗粒数据pin脚直接与主板上内存条slot槽位相连。其缺点在于因为其连接的dram颗粒数有限,一般dram颗粒数与颗粒位数相乘应与总线位数相等,所以容量较低。因此亟需一种方法可以在dram颗粒数据速率不变的情况下,提高整个ddr通道速率,使内存数据传输速率提高。

技术实现思路

1、基于此,本申请提供了一种内存速率提高装置、方法、设备和存储介质,以解决现有技术中存在的问题。

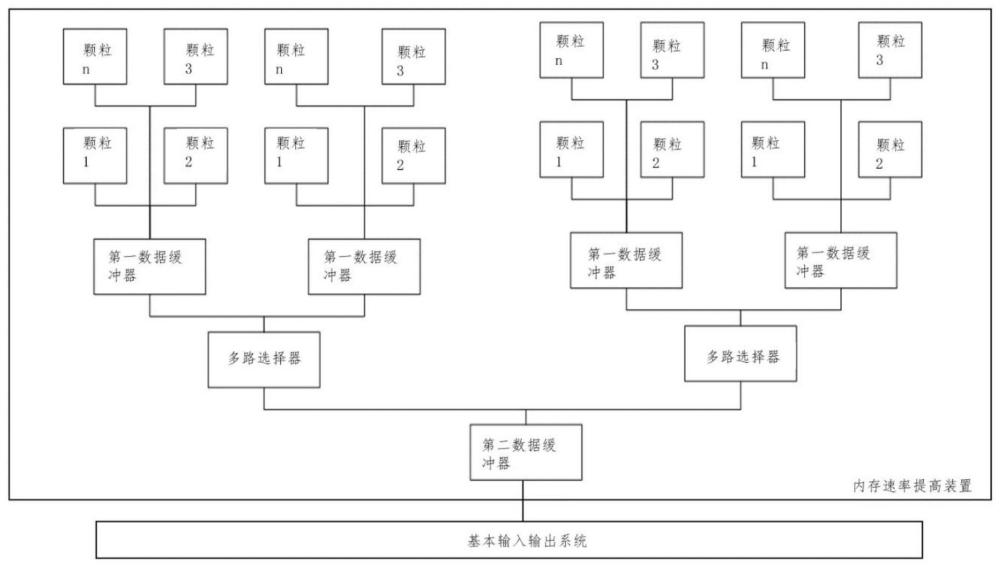

2、第一方面,提供一种内存速率提高装置,该装置包括:第一数据缓冲器、第二数据缓冲器、多路选择器和多个内存颗粒;

3、所述第一数据缓冲器连接多个所述内存颗粒;

4、所述多路选择器连接两个所述第一数据缓冲器,其中,每一个所述第一数据缓冲器连接多个内存颗粒;

5、所述第二数据缓冲器的一端连接两个所述多路选择器,其中,每一个所述多路选择器连接两个所述第一数据缓冲器,每一个所述第一数据缓冲器连接多个内存颗粒;所述第二数据缓冲器的另一端连接基本输入输出系统。

6、根据本申请实施例中一种可实现的方式,所述装置还包括:第一切换开关;

7、所述第一切换开关的一端连接多个所述第二数据缓冲器,其中,多个所述第二数据缓冲器之间并联连接,每一个所述第二数据缓冲器连接两个所述多路选择器,每一个所述多路选择器连接两个所述第一数据缓冲器,每一个所述第一数据缓冲器连接多个内存颗粒;

8、所述第一切换开关的另一端连接基本输入输出系统。

9、根据本申请实施例中一种可实现的方式,所述装置还包括:第二切换开关;

10、所述第二切换开关的一端连接多个所述第一切换开关,其中,多个所述第一切换开关之间并联连接;

11、所述第二切换开关的另一端连接基本输入输出系统。

12、根据本申请实施例中一种可实现的方式,所述第二切换开关的另一端连接基本输入输出系统,包括:

13、所述第二切换开关与rcd芯片串联连接;

14、所述rcd芯片与中央处理器通信连接。

15、根据本申请实施例中一种可实现的方式,所述第一切换开关和所述第二切换开关为switch选通芯片。

16、根据本申请实施例中一种可实现的方式,所述第一数据缓冲器和所述第二数据缓冲器遵循bcom总线协议,所述rcd芯片遵循bcom总线协议。

17、第二方面,提供了一种内存速率提高方法,该方法包括:

18、通过第一数据缓冲器连接多个所述内存颗粒;

19、通过多路选择器连接两个所述第一数据缓冲器,其中,每一个所述第一数据缓冲器连接多个内存颗粒;

20、通过第二数据缓冲器连接两个所述多路选择器,其中,每一个所述多路选择器连接两个所述第一数据缓冲器,每一个所述第一数据缓冲器连接多个内存颗粒;

21、通过第二数据缓冲器连接基本输入输出系统执行数据传递。

22、根据本申请实施例中一种可实现的方式,所述通过第二数据缓冲器连接基本输入输出系统执行数据传递,包括:

23、通过第一切换开关连接多个所述第二数据缓冲器,其中,多个所述第二数据缓冲器之间并联连接,每一个所述第二数据缓冲器连接两个所述多路选择器,每一个所述多路选择器连接两个所述第一数据缓冲器,每一个所述第一数据缓冲器连接多个内存颗粒;

24、通过第一切换开关连接基本输入输出系统执行数据传递。

25、第三方面,提供了一种计算机设备,包括:

26、至少一个处理器;以及

27、与所述至少一个处理器通信连接的存储器;其中,

28、所述存储器存储有可被所述至少一个处理器执行的计算机指令,所述计算机指令被所述至少一个处理器执行,以使所述至少一个处理器能够执行上述第一方面中涉及的装置。

29、第四方面,提供了一种计算机可读存储介质,其上存储有计算机指令,其特征在于,所述计算机指令用于使计算机执行上述第一方面中涉及的装置。

30、根据本申请实施例所提供的技术内容,本申请通过第一数据缓冲器连接多个内存颗粒;多路选择器连接两个第一数据缓冲器,其中,每一个第一数据缓冲器连接多个内存颗粒;第二数据缓冲器的一端连接两个多路选择器,其中,每一个多路选择器连接两个第一数据缓冲器,每一个第一数据缓冲器连接多个内存颗粒;第二数据缓冲器的另一端连接基本输入输出系统。本申请可以传输双倍的数据量,提高内存的速率。同时可以在通道数量不变的情况下,增加颗粒的数量来提高内存量。

技术特征:

1.一种内存速率提高装置,其特征在于,该装置包括:第一数据缓冲器、第二数据缓冲器、多路选择器和多个内存颗粒;

2.根据权利要求1所述的内存速率提高装置,其特征在于,所述装置还包括:第一切换开关;

3.根据权利要求2所述的内存速率提高装置,其特征在于,所述装置还包括:第二切换开关;

4.根据权利要求3所述的内存速率提高装置,其特征在于,所述第二切换开关的另一端连接基本输入输出系统,包括:

5.根据权利要求3所述的内存速率提高装置,其特征在于,所述第一切换开关和所述第二切换开关为switch选通芯片。

6.根据权利要求1所述的内存速率提高装置,其特征在于,所述第一数据缓冲器和所述第二数据缓冲器遵循bcom总线协议,所述rcd芯片遵循bcom总线协议。

7.一种基于权利要求1所述内存速率提高装置的内存速率提高方法,其特征在于,该方法包括:

8.根据权利要求1所述的内存速率提高方法,其特征在于,所述通过第二数据缓冲器连接基本输入输出系统执行数据传递,包括:

9.一种计算机设备,包括:

10.一种计算机可读存储介质,其上存储有计算机指令,其特征在于,所述计算机指令用于使计算机执行权利要求7至8中任一项所述的装置。

技术总结

本申请涉及一种内存速率提高装置、方法、设备和存储介质,该装置包括:第一数据缓冲器、第二数据缓冲器、多路选择器和多个内存颗粒;所述第一数据缓冲器连接多个所述内存颗粒;所述多路选择器连接两个所述第一数据缓冲器,其中,每一个所述第一数据缓冲器连接多个内存颗粒;所述第二数据缓冲器的一端连接两个所述多路选择器,其中,每一个所述多路选择器连接两个所述第一数据缓冲器,每一个所述第一数据缓冲器连接多个内存颗粒;所述第二数据缓冲器的另一端连接基本输入输出系统。本申请可以提高内存速率。

技术研发人员:金霞,王晓,刘波,孙秀强

受保护的技术使用者:苏州元脑智能科技有限公司

技术研发日:

技术公布日:2024/3/21

- 还没有人留言评论。精彩留言会获得点赞!