用于提高并行测试通道速率的被测芯片、方法、电子设备及存储介质与流程

本发明涉及芯片电路结构设计及测试。尤其是涉及一种用于提高并行测试通道速率的被测芯片、方法、电子设备及存储介质。

背景技术:

1、随着集成电路制造工艺的进步,芯片集成度不断提高,芯片管脚数目剧增。传统的dut(被测设备,这里指被测芯片)电路结构中存在并行测试管脚数目过多、测试频率难以提高等问题。

2、比如,传统测试方法是用一个时钟带一组测试数据并行输入到被测试芯片。这组并行测试数据管脚数目可能高达数百甚至上千。这些并行测试管脚需要同步接收时钟信号,但是由于工艺和布线等因素,不同测试管脚之间存在时序偏移(skew),制约芯片并行测试通道的整体工作频率。

技术实现思路

1、有鉴于此,本发明实施例提供一种用于提高并行测试通道速率的被测芯片、方法、电子设备及存储介质,能够改善或克服不同测试通道的io管脚之间存在的时序偏移问题,进而便于提高并行测试通道整体工作频率。

2、为达到上述发明目的,采用如下技术方案:

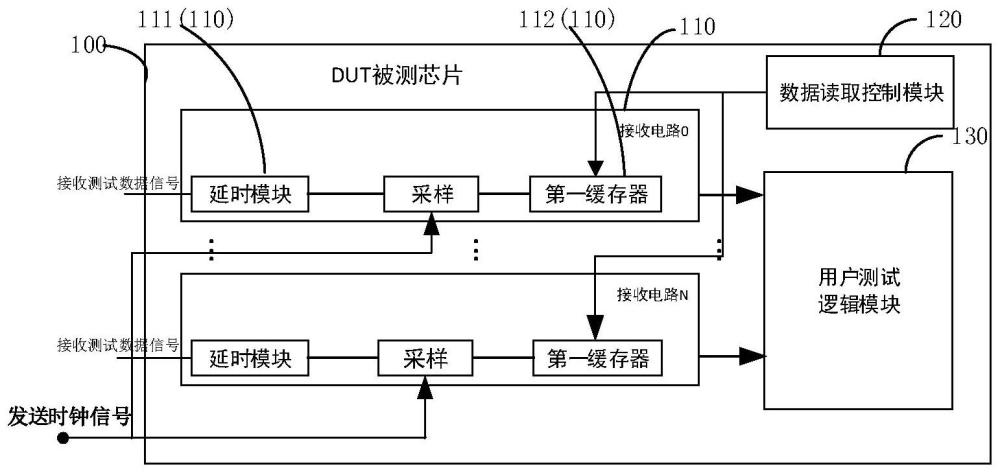

3、本申请实施例提供一种芯片,所述芯片包括:

4、多个接收电路,每个接收电路包括:

5、延时模块,用于接收测试数据,并调整对应接收电路的数据延时,以使所述测试数据到达采样点时位于数据采样窗口内;

6、第一缓存器,与所述延时模块连接,并用于缓存有效数据,所述有效数据来自所述采样窗口内的测试数据;以及,

7、数据读取控制模块,用于在多个接收电路的第一缓存器存入有效数据后,控制读取多个所述第一缓存器的有效数据的操作。

8、根据本申请实施例的一种具体实现方式,每个接收电路还包括::

9、数据采样模块,用于在所述采样点根据测试时钟对经由所述延时模块的数据采样;

10、数据检测模块,用于检测来自所述数据采样模块的数据是否为所述测试数据,以判断所述延时模块的数据延时是否需要调整。

11、根据本申请实施例的一种具体实现方式,所述数据检测模块,还用于当检测到来自所述数据采样模块的数据是所述测试数据时,则判断所述延时模块的数据延时不需要调整;以及,

12、用于当检测到来自所述数据采样模块的数据不是所述测试数据时,则判断所述延时模块的数据延时需要调整。

13、根据本申请实施例的一种具体实现方式,所述数据检测模块,还用于若判断所述延时模块的数据延时需要调整,则以当前确定的所述数据延时为基准,进行前后移动调整;

14、每次调整后,重复进行测试码采样和数据检测,得到每次调整后的数据检测结果;

15、比对每次调整后的数据检测结果,直至找到一个采样宽度最大的采样窗口。

16、根据本申请实施例的一种具体实现方式,所述芯片还包括:解码模块,位于所述数据采样模块之后,并位于所述第一缓存器之前,用于在对经由所述延时模块的数据采样之后,解码所述采样的数据,并将解码后的有效数据发送至所述第一缓存器;

17、缓存读取控制模块,用于根据预设条件控制是否将缓存的测试数据读取发送。

18、根据本申请实施例的一种具体实现方式,所述解码模块,具体用于在解码所述采样的数据之后,判断解码得到的内容的类型;

19、如果所述内容的类型为有效数据,则发送至所述第一缓存器;

20、如果所述内容的类型为同步头标志符,则丢弃。

21、根据本申请实施例的一种具体实现方式,所述缓存读取控制模块,具体用于在多个所述接收电路的第一缓存器都不为空时,则从每个所述接收电路的第一缓存器执行读取一个有效数据的操作。

22、根据本申请实施例的一种具体实现方式,所述芯片还包括:多个发送电路,每个发送电路包括:

23、第二缓存器,用于接收并存储需要发送的测试数据;

24、编码模块,与所述第二缓存器的输出端连接,用于对从第二缓存器输出的测试数据进行编码,并将编码后的测试数据发送。

25、根据本申请实施例的一种具体实现方式,所述发送电路还包括:数据发送模块,用于在与测试设备进行数据训练时,向测试设备发送测试数据,以确认发送通道链路是否正常;

26、所述数据发送模块和编码模块的输出端还设有数据发送切换开关。

27、第二方面,本发明还实施例提供一种芯片测试方法,包括:

28、接收测试设备发送的测试数据,并调整对应接收电路的数据延时,以使所述测试数据到达采样点时位于数据采样窗口内;

29、缓存有效数据,所述有效数据来自所述采样窗口内的测试数据;以及,

30、监测到每个接收电路存入有效数据后,控制读取所述每个接收电路缓存的有效数据的操作。

31、根据本申请实施例的一种具体实现方式,在接收测试设备发送的测试数据,并调整对应接收电路的数据延时,以使所述测试数据到达采样点时位于数据采样窗口内之后,所述方法还包括:在所述采样点根据测试时钟对所述数据采样;

32、检测来自所述数据采样模块的数据是否为所述测试数据,以判断对应的每个接收电路的数据延时是否需要调整。

33、根据本申请实施例的一种具体实现方式,所述检测来自所述数据采样模块的数据是否为所述测试数据,以判断对应的每个接收电路的数据延时是否需要调整,包括:若检测到来自所述数据采样模块的数据是所述测试数据时,则判断所述延时模块的数据延时不需要调整;以及,

34、若检测到来自所述数据采样模块的数据不是所述测试数据时,则判断所述延时模块的数据延时需要调整。

35、根据本申请实施例的一种具体实现方式,在判断所述延时模块的数据延时需要调整之后,所述方法还包括:以当前确定的所述数据延时为基准,进行前后移动调整;

36、每次调整后,重复进行测试码采样和数据检测,得到每次调整后的数据检测结果;

37、比对每次调整后的数据检测结果,直至找到一个采样宽度最大的采样窗口。

38、第三方面,本申请还实施例提供一种电子设备,包括:

39、一个或者多个处理器;存储器;

40、所述存储器中存储有一个或者多个可执行程序代码,所述一个或者多个处理器读取存储器中存储的可执行程序代码,来运行与可执行程序代码对应的程序,以用于执行第二方面任一所述的方法。

41、第四方面,本申请还实施例提供一种计算机可读存储介质,所述计算机可读存储介质存储有一个或者多个程序,所述一个或者多个程序可被一个或者多个处理器执行,以用于实现第二方面任一所述的方法。

技术特征:

1.一种芯片,其特征在于,所述芯片包括:

2.根据权利要求1所述的芯片,其特征在于,每个接收电路还包括::

3.根据权利要求2所述的芯片,其特征在于,所述数据检测模块,还用于当检测到来自所述数据采样模块的数据是所述测试数据时,则判断所述延时模块的数据延时不需要调整;以及,

4.根据权利要求3所述的芯片,其特征在于,所述数据检测模块,还用于若判断所述延时模块的数据延时需要调整,则以当前确定的所述数据延时为基准,进行前后移动调整;

5.根据权利要求1所述的芯片,其特征在于,所述芯片还包括:解码模块,位于所述数据采样模块之后,并位于所述第一缓存器之前,用于在对经由所述延时模块的数据采样之后,解码所述采样的数据,并将解码后的有效数据发送至所述第一缓存器;

6.根据权利要求5所述的芯片,其特征在于,所述解码模块,具体用于在解码所述采样的数据之后,判断解码得到的内容的类型;

7.根据权利要求5所述的芯片,其特征在于,所述缓存读取控制模块,具体用于在多个所述接收电路的第一缓存器都不为空时,则从每个所述接收电路的第一缓存器执行读取一个有效数据的操作。

8.根据权利要求1所述的芯片,其特征在于,所述芯片还包括:多个发送电路,每个发送电路包括:

9.根据权利要求8所述的芯片,其特征在于,所述发送电路还包括:数据发送模块,用于在与测试设备进行数据训练时,向测试设备发送测试数据,以确认发送通道链路是否正常;

10.一种芯片测试方法,其特征在于,包括:

11.根据权利要求10所述的芯片测试方法,其特征在于,在接收测试设备发送的测试数据,并调整对应接收电路的数据延时,以使所述测试数据到达采样点时位于数据采样窗口内之后,所述方法还包括:在所述采样点根据测试时钟对所述数据采样;

12.根据权利要求11所述的芯片测试方法,其特征在于,所述检测来自所述数据采样模块的数据是否为所述测试数据,以判断对应的每个接收电路的数据延时是否需要调整,包括:若检测到来自所述数据采样模块的数据是所述测试数据时,则判断所述延时模块的数据延时不需要调整;以及,

13.根据权利要求12所述的芯片测试方法,其特征在于,在判断所述延时模块的数据延时需要调整之后,所述方法还包括:以当前确定的所述数据延时为基准,进行前后移动调整;

14.一种电子设备,其特征在于,包括:

15.一种计算机可读存储介质,其特征在于,所述计算机可读存储介质存储有一个或者多个程序,所述一个或者多个程序可被一个或者多个处理器执行,以用于实现权利要求10至13任一所述芯片测试方法。

技术总结

本发明实施例公开的用于提高并行测试通道速率的被测芯片、方法、电子设备及存储介质,涉及芯片电路结构设计及测试技术领域,芯片包括:多个接收电路,每个接收电路包括:延时模块,用于接收测试数据,并调整对应接收电路的数据延时,以使所述测试数据到达采样点时位于数据采样窗口内;第一缓存器,与所述延时模块连接,并用于缓存有效数据,所述有效数据来自所述采样窗口内的测试数据;以及,数据读取控制模块,用于在多个接收电路的第一缓存器存入有效数据后,控制读取多个所述第一缓存器的有效数据的操作。本发明能够改善或克服不同测试通道的IO管脚之间存在的时序偏移问题,进而便于提高并行测试通道整体工作频率,适用于芯片测试场景中。

技术研发人员:张国

受保护的技术使用者:成都海光集成电路设计有限公司

技术研发日:

技术公布日:2024/3/24

- 还没有人留言评论。精彩留言会获得点赞!