一种接口扩展装置的制作方法

本技术涉及通信,尤其涉及一种接口扩展装置。

背景技术:

1、对于计算机而言,通用的可扩展接口为pcie插槽,而m.2接口受限于空间在计算机主板数量通常不多于两个。m.2设备相对于pcie设备对于计算机机箱的利用率高很多。在一些场合下扩展m.2设备需要用到pcie转m.2的转接设备。

2、如图1所示,为现有技术中接口扩展电路示意图,采用pcie桥将pcie接口和m.2连接,pcie桥是pcie扩展的芯片,一个输入网口可以输出多个网口,如一个x4的输入然后转出两个x4的接口,所有的pcie扩展均是通过pcie桥来扩展;在不使用pcie桥的情况下一个pcie x8的槽能转成一个m.2(pcie x4)的槽位,此时会有一个pcie x4的资源浪费,而在使用pcie桥来转接成两个m.2(pcie x4)的槽位时虽然功能实现,但是实现复杂,而且会增加很多成本,如何既可以实现接口的扩展,还可以节省成本,是目前急需解决的问题。

技术实现思路

1、针对上述技术问题,本实用新型实施例提供了一种接口扩展装置。

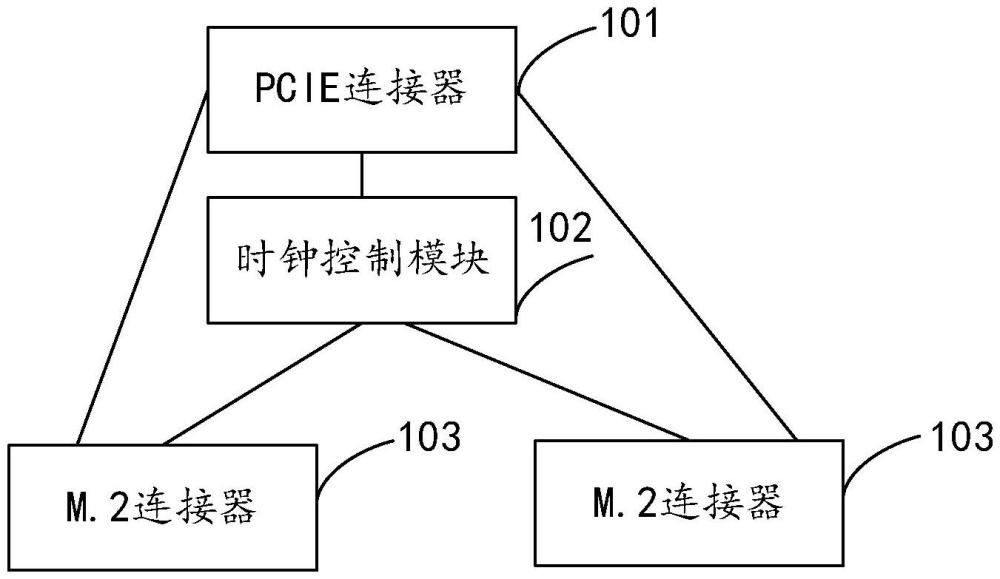

2、本实用新型实施例提供一种接口扩展装置,所述接口扩展装置至少包括pcie连接器、时钟控制模块和多个m.2连接器,其中,所述pcie连接器通过所述时钟控制模块分别与所述多个m.2连接器相连;

3、所述pcie连接器的数据线分别与所述多个m.2连接器相连;

4、所述pcie连接器时钟信号与所述时钟控制模块的输入时钟信号相连;所述时钟控制模块的多个输出时钟信号分别与所述多个m.2连接器相连。

5、可选地,所述m.2连接器的数量为两个。

6、可选地,所述pcie连接器的第一数据线、第二数据线、第三数据线和第四数据线分别与第一m.2连接器相连。

7、可选地,所述pcie连接器的第四数据线、第五数据线、第六数据线和第七数据线分别与第二m.2连接器相连。

8、可选地,所述时钟控制模块包括四个输出时钟信号。

9、可选地,所述时钟控制模块的第一输出时钟信号与第一m.2连接器相连。

10、可选地,所述时钟控制模块的第二输出时钟信号与第二m.2连接器相连。

11、可选地,所述时钟控制模块为clb53156芯片。

12、可选地,所述时钟控制模块为si53156芯片。

13、可选地,所述接口扩展装置还包括供电接口,所述供电接口用于连接电源电路。

14、本实用新型实施例提供的技术方案中,接口扩展装置至少包括pcie连接器、时钟控制模块和多个m.2连接器,其中,pcie连接器通过时钟控制模块分别与多个m.2连接器相连;pcie连接器的数据线分别与多个m.2连接器相连;pcie连接器时钟信号与时钟控制模块的输入时钟信号相连;时钟控制模块的多个输出时钟信号分别与多个m.2连接器相连,本实用新型实施例不使用pcie桥的方式实现一个pcie x8的槽能转成两个m.2(pcie x4)的槽位,结构简单、低成本、高扩展性及高密度设计。

技术特征:

1.一种接口扩展装置,其特征在于:所述接口扩展装置至少包括pcie连接器、时钟控制模块和多个m.2连接器,其中,所述pcie连接器通过所述时钟控制模块分别与所述多个m.2连接器相连;

2.根据权利要求1所述的接口扩展装置,其特征在于,所述m.2连接器的数量为两个。

3.根据权利要求2所述的接口扩展装置,其特征在于,所述pcie连接器的第一数据线、第二数据线、第三数据线和第四数据线分别与第一m.2连接器相连。

4.根据权利要求3所述的接口扩展装置,其特征在于,所述pcie连接器的第四数据线、第五数据线、第六数据线和第七数据线分别与第二m.2连接器相连。

5.根据权利要求4所述的接口扩展装置,其特征在于,所述时钟控制模块包括四个输出时钟信号。

6.根据权利要求5所述的接口扩展装置,其特征在于,所述时钟控制模块的第一输出时钟信号与第一m.2连接器相连。

7.根据权利要求6所述的接口扩展装置,其特征在于,所述时钟控制模块的第二输出时钟信号与第二m.2连接器相连。

8.根据权利要求1所述的接口扩展装置,其特征在于,所述时钟控制模块为clb53156芯片。

9.根据权利要求1所述的接口扩展装置,其特征在于,所述时钟控制模块为si53156芯片。

10.根据权利要求1所述的接口扩展装置,其特征在于,所述接口扩展装置还包括供电接口,所述供电接口用于连接电源电路。

技术总结

本技术实施例公开了一种接口扩展装置,接口扩展装置至少包括PCIE连接器、时钟控制模块和多个M.2连接器,其中,PCIE连接器通过时钟控制模块分别与多个M.2连接器相连;PCIE连接器的数据线分别与多个M.2连接器相连;PCIE连接器时钟信号与时钟控制模块的输入时钟信号相连;时钟控制模块的多个输出时钟信号分别与多个M.2连接器相连,本技术实施例不使用PCIE桥的方式实现一个PCIE X8的槽能转成两个M.2(PCIE X4)的槽位,结构简单、低成本、高扩展性及高密度设计。

技术研发人员:黄振华,张艳平

受保护的技术使用者:珠海世宁达科技有限公司

技术研发日:20230731

技术公布日:2024/2/6

- 还没有人留言评论。精彩留言会获得点赞!