人工智能加速器装置的制作方法

本新型实施例是有关于人工智能加速器装置,且特别是有关于执行乘法累加运算的人工智能加速器装置。

背景技术:

1、人工智能(ai)加速器装置是一类专用硬件,其可用于加速机器学习工作负载,而这些工作负载通常被建模为涉及大规模存储器存取和高度并行计算的神经网络。ai加速器装置可以在一或多种类型的硬件中实现,例如中央处理器(cpu)、图形处理单元(gpu)、现场可编程逻辑闸阵列(fpga)和/或特殊应用集成电路(asic)等例子。

技术实现思路

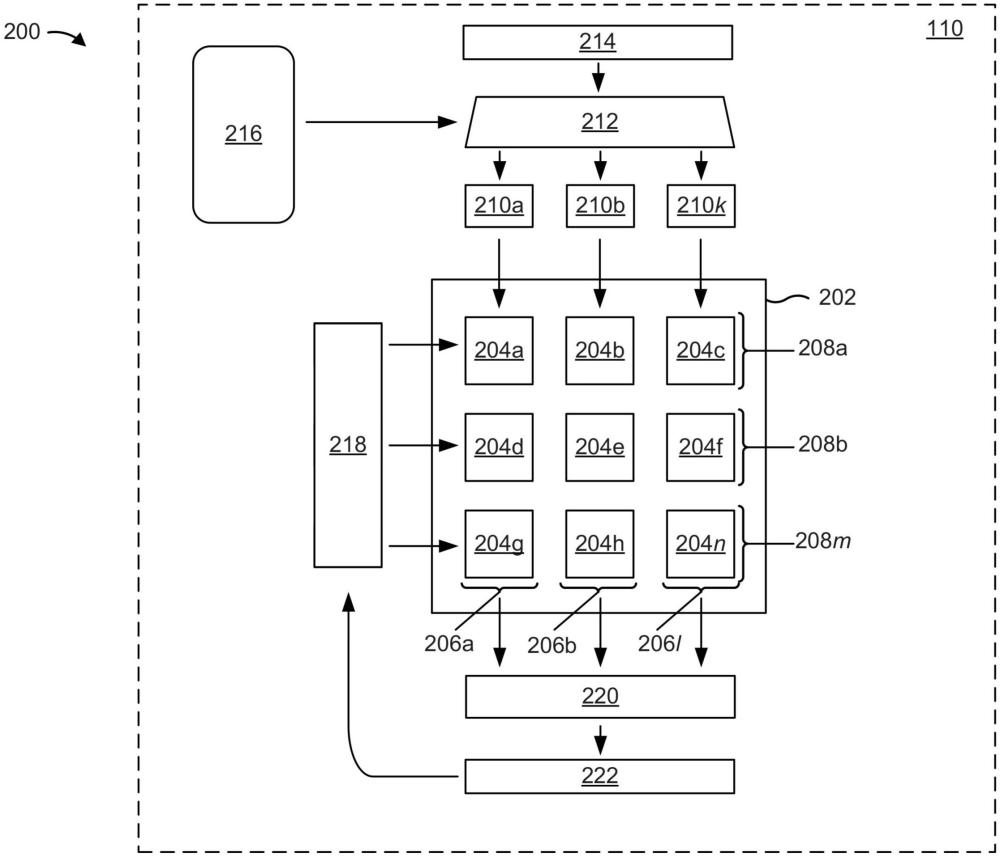

1、本新型实施例提供一种人工智能加速器装置。人工智能加速器装置包括一处理元件阵列以及相关联于处理元件阵列的多个权重缓冲器。处理元件阵列包括设置在多个行以及多个列的多个处理元件电路。权重缓冲器是相关联于处理元件阵列的处理元件电路的行的个别子集的行。

2、优选地,所述人工智能加速器装置更包括:一存储器装置;以及一权重缓冲器多工器电路,其中该存储器装置是经由该权重缓冲器多工器电路而耦接于所述多个权重缓冲器。

3、优选地,所述人工智能加速器装置更包括:多个活化缓冲器,相关联于该处理元件阵列,其中所述多个活化缓冲器是相关联于该处理元件阵列的所述多个处理元件电路的所述多个列的个别子集的列。

4、优选地,所述人工智能加速器装置更包括:一活化缓冲器多工器电路,耦接于该等活化缓冲器;以及一分配器电路,耦接于该活化缓冲器多工器电路。

5、优选地,所述人工智能加速器装置更包括:多个累加器缓冲器,相关联于该处理元件阵列,其中所述多个累加器缓冲器是相关联于该处理元件阵列的所述多个处理元件电路的所述多个行的一个别子集的行。

6、再者,本新型实施例提供一种人工智能加速器装置。人工智能加速器装置包括一处理元件阵列以及相关联于处理元件阵列的多个活化缓冲器。处理元件阵列包括设置在多个行以及多个列的多个处理元件电路。活化缓冲器是相关联于处理元件阵列的处理元件电路的列的一个别子集的列。

7、优选地,每一该活化缓冲器是相关联于该处理元件阵列的所述多个处理元件电路的所述多个列的一单一个别的列。

8、优选地,所述人工智能加速器装置更包括:一活化缓冲器多工器电路,耦接于所述多个活化缓冲器;一分配器电路,耦接于该活化缓冲器多工器电路;以及多个累加器缓冲器,相关联于该处理元件阵列,其中所述多个累加器缓冲器是相关联于该处理元件阵列的所述多个处理元件电路的所述多个行的一个别子集的行。

9、优选地,该人工智能加速器装置配置为执行一输入静态数据流,以及其中所述多个累加器缓冲器的数量是大于所述多个活化缓冲器的数量。

10、优选地,该人工智能加速器装置配置为执行一输出静态数据流,以及其中该人工智能加速器装置包括一单片累加器缓冲器。

技术特征:

1.一种人工智能加速器装置,其特征在于,包括:

2.如权利要求1所述的人工智能加速器装置,其特征在于,更包括:

3.如权利要求1所述的人工智能加速器装置,其特征在于,更包括:

4.如权利要求3所述的人工智能加速器装置,其特征在于,更包括:

5.如权利要求4所述的人工智能加速器装置,其特征在于,更包括:

6.一种人工智能加速器装置,其特征在于,包括:

7.如权利要求6所述的人工智能加速器装置,其特征在于,每一该活化缓冲器是相关联于该处理元件阵列的所述多个处理元件电路的所述多个列的一单一个别的列。

8.如权利要求6所述的人工智能加速器装置,其特征在于,更包括:

9.如权利要求8所述的人工智能加速器装置,其特征在于,该人工智能加速器装置配置为执行一输入静态数据流,以及其中所述多个累加器缓冲器的数量是大于所述多个活化缓冲器的数量。

10.如权利要求6所述的人工智能加速器装置,其特征在于,该人工智能加速器装置配置为执行一输出静态数据流,以及其中该人工智能加速器装置包括一单片累加器缓冲器。

技术总结

提供一种人工智能加速器装置。人工智能加速器装置包括一处理元件阵列以及相关联于处理元件阵列的多个权重缓冲器。处理元件阵列包括设置在多个行以及多个列的多个处理元件电路。权重缓冲器是相关联于处理元件阵列的处理元件电路的行的个别子集的行。

技术研发人员:孙晓宇,彭晓晨,穆拉特·凯雷姆·阿卡尔瓦达尔

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:20230822

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!