具有重叠连接的模块化量子芯片设计的制作方法

本公开一般涉及量子计算,并且更具体地,涉及量子计算芯片设计。

背景技术:

1、超导量子计算是在超导电子电路中的量子计算机的一种实现方式。量子计算研究了量子现象在信息处理和通信中的应用。存在量子计算的各种模型,并且最受欢迎的模型包括量子位和量子门的概念。量子位是具有两种可能状态、但是可以处于两种状态的量子叠加中的位的一般化。量子门是逻辑门的一般化,然而,量子门描述了在给定量子位的初始状态下,在门被应用于它们之后一个或多个量子位将经历的变换。可以在不同的热隔离阶段中操作的各种部件,诸如低噪声放大器,可以用于与量子位通信。许多量子现象,诸如叠加和纠缠,在经典计算世界中不具有类似性,因此可能涉及特殊的结构、技术和材料。

2、量子计算将涉及大量的量子位以实现本领域技术人员已经提出的潜力。目前,大多数现有的硅基器件是原始较小器件的越来越大的版本,例如,所有量子位都制造在单个芯片上。一旦量子位计数超过大约一千的数量级,制造这种单片器件变得困难或不可能,这既是因为所需的晶片尺寸,也是因为实际的考虑,诸如工具可用性或产量问题。因此,模块化制造方法是值得关注的,其关注点在于紧密封装的芯片以促进维持模块之间的高质量总线连接。

技术实现思路

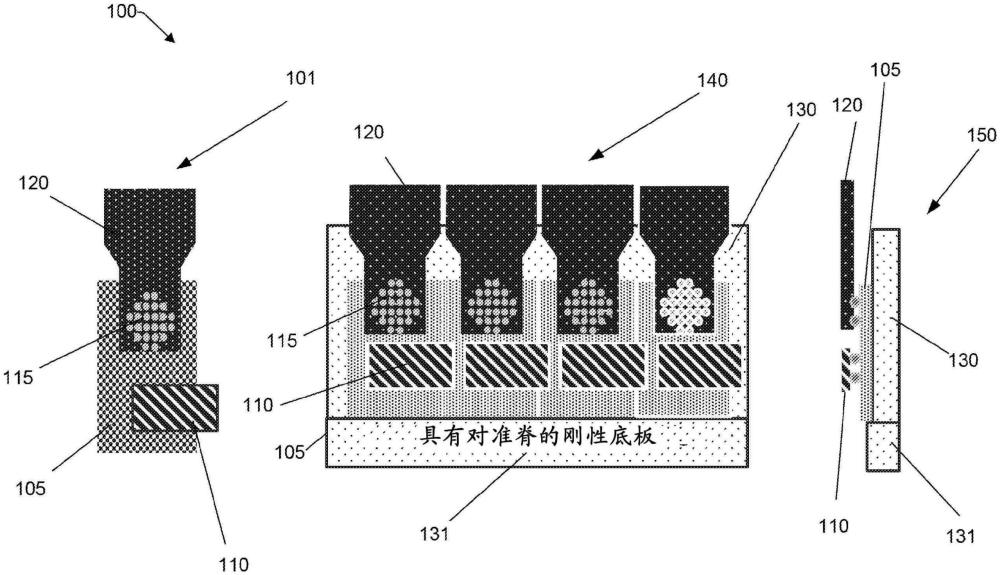

1、根据一个实施例,量子计算(qc)芯片模块包括具有封装(footprint)的中介层芯片。量子位芯片凸点键合到所述中介层芯片并且被布置成使得所述量子位芯片延伸超过所述中介层芯片的封装。所述中介层芯片延伸超过所述量子位芯片的边缘,并且线束连接到所述中介层芯片。该构造使得所述量子位芯片从所述中介层伸出,以在相邻量子位芯片之间形成电容耦合总线。

2、在一个实施例中,所述线束包括超导柔性电缆。所述量子位芯片由所述超导柔性电缆中的电信号控制和读取。使用所述超导电缆最小化热和电信号的损失。

3、根据一个实施例,量子计算(qc)芯片模块组件包括多个连接为一行的qc芯片模块。每个qc芯片模块包括具有封装的中介层芯片。量子位芯片由凸点键合到所述中介层芯片并且被布置成使得所述量子位芯片延伸超过所述中介层芯片的封装。所述中介层芯片延伸超过所述量子位芯片的边缘。线束连接到中介层芯片,所述线束包括超导柔性电缆。所述量子位芯片由所述超导柔性电缆中的电信号控制和读取。该组件通过使用所述中介层的边缘来相对于彼此定位模块而提供增强的尺寸精度。

4、在一个实施例中,所述多个qc模块包括布置成l形几何形状的量子位芯片、中介层芯片和线束。所述l形几何形状允许所述量子位芯片的布置伸出到相邻模块上,以便于相邻量子位芯片之间电容耦合总线。

5、在一个实施例中,在每个qc模块中,所述线束附接在所述中介层芯片的两个区域上,以与布置在所述中介层芯片上的所述量子位芯片形成t形几何形状。由于所述线束在所述中介层芯片的两个区域上的连接,可以在中介层上布置增加数量的量子位。

6、在一个实施例中,所述量子位芯片与所述中介层芯片之间的间隙由将所述量子位芯片连接到所述中介层芯片的所述凸点键合的最终凸点高度限定,并且与多个qc芯片模块中的任何模块内的所述量子位芯片与所述中介层间隙之间的间隙相同。具有“相同”凸点高度提供了所述qc模块的部件的更精确的构造。

7、根据一个实施例,一种构造量子计算(qc)芯片模块组件的方法包括以下操作:将多个qc芯片模块连接成一排。每个qc芯片模块包括具有封装的中介层芯片、量子位芯片,该量子位芯片凸点键合到所述中介层芯片并被布置成使得所述量子位芯片延伸超过所述中介层芯片的封装。所述中介层芯片延伸超过所述量子位芯片的边缘。线束连接到中介层芯片,所述线束包括超导柔性电缆。所述量子位芯片由所述超导柔性电缆中的电信号控制和读取。所述方法允许所述量子位芯片伸出到相邻模块上并且创建与相邻qc模块的电容耦合。

8、在一个实施例中,所述方法还包括将所述量子位芯片、所述中介层芯片和所述线束布置成l形几何形状。所述l形几何形状便于将多个qc模块布置在一起并创建电容耦合总线。

9、在一个实施例中,在每个qc模块中,所述线束附接在所述中介层芯片的两个区域上,以与布置在所述中介层芯片上的所述量子位芯片形成t形几何形状。t形几何形状使可以连接到所述中介层的量子位的数量加倍及以上,从而允许更大且更密集的电路。

10、在一个实施例中,所述方法还包括通过将所述量子位芯片连接到所述中介层芯片的凸点键合的最终凸点高度来限定所述量子位芯片与所述中介层芯片之间的间隙。所述限定的间隙与所述多个qc模块中的任何模块内的所述量子位芯片与所述中介层间隙之间的间隙相同。所述方法提供了更均匀和尺寸精确的结构。

11、从以下结合附图阅读的说明性实施例的详细描述中,这些和其它特征将变得显而易见。

技术特征:

1.一种量子计算(qc)芯片模块,包括:

2.根据权利要求1所述的qc芯片模块,其中:

3.根据权利要求2所述的qc芯片模块,其中,所述量子位芯片与所述中介层芯片之间的间隙由将所述量子位芯片连接到所述中介层芯片的所述凸点键合的最终凸点高度限定。

4.根据权利要求3所述的qc芯片模块,其中:

5.一种量子计算(qc)芯片模块组件,包括:

6.根据权利要求5所述的qc芯片模块组件,其中所述多个qc模块具有以l形几何形状布置的所述量子位芯片、所述中介层芯片和所述线束。

7.根据前述权利要求5至6中的任一项所述的qc芯片模块组件,其中,在每个qc芯片模块中,所述线束附接在所述中介层芯片的两个区域上,以与布置在所述中介层芯片上的所述量子位芯片形成t形几何形状。

8.根据前述权利要求5至7中的任一项所述的qc芯片模块组件,其中,所述量子位芯片与所述中介层芯片之间的间隙由将所述量子位芯片连接到所述中介层芯片的所述凸点键合的最终凸点高度限定,并且与所述多个qc芯片模块中的任何模块内的所述量子位芯片与所述中介层间隙之间的间隙的尺寸相同。

9.根据前述权利要求5至8中的任一项所述的qc芯片模块组件,其中,所述多个qc芯片模块以平铺的形式布置,以在第一qc芯片模块的所述量子位芯片与相邻qc芯片模块的所述中介层芯片之间形成气隙连接。

10.根据前述权利要求5至9中的任一项所述的qc芯片模块组件,其中,所述多个qc芯片模块布置在刚性底板上。

11.根据权利要求10所述的qc芯片模块组件,其中所述刚性底板包括对准脊,以便于所述多个qc芯片模块的平面内对准。

12.根据权利要求10所述的qc芯片模块组件,其中,所述刚性底板包括阶梯,以使每个随后布置的qc芯片模块相比于先前布置的模块升高固定高度。

13.根据权利要求10所述的qc芯片模块组件,其中,所述中介层芯片包括内置间隔件,以在所述多个qc芯片模块的第一qc芯片模块的所述中介层芯片与相邻qc模块的所述量子位芯片之间保持基本恒定的间隙。

14.根据权利要求10所述的qc芯片模块组件,其中:

15.根据权利要求10所述的qc芯片模块组件,其中,相邻qc模块上的量子位芯片之间的耦合包括跨过所述相邻qc模块之间的气隙的电容耦合。

16.根据权利要求10所述的qc芯片模块组件,其中,相邻qc模块上的量子位芯片之间的耦合包括所述相邻qc模块之间的电感耦合。

17.一种构造量子计算(qc)芯片模块组件的方法,包括:

18.根据权利要求17所述的方法,还包括将所述量子位芯片、所述中介层芯片和所述线束布置成l形几何形状。

19.根据前述权利要求17至18中的任一项所述的方法,其中在每个qc模块中,所述线束附接在所述中介层芯片的两个区域上,以与布置在所述中介层芯片上的所述量子位芯片形成t形几何形状。

20.根据前述权利要求17至19中任一项所述的方法,还包括通过将所述量子位芯片连接到所述中介层芯片的所述凸点键合的最终凸点高度来限定所述量子位芯片与所述中介层芯片之间的间隙,其中所限定的间隙与所述多个qc模块中的任何模块内的所述量子位芯片与所述中介层之间的间隙相同。

21.根据前述权利要求17至20中的任一项所述的方法,还包括以平铺形式布置所述多个qc模块,以在第一qc芯片模块的所述量子位芯片与相邻qc芯片模块的所述中介层芯片之间形成气隙连接。

22.根据前述权利要求17至21中的任一项所述的方法,还包括将所述多个qc芯片模块布置在刚性底板上。

23.根据权利要求22所述的方法,还包括在所述刚性底板上的对准脊,以便于所述多个qc芯片模块的平面内对准。

24.根据权利要求22所述的方法,还包括在所述刚性底板中的阶梯,以使每个随后布置的qc模块相比于先前布置的qc模块升高固定高度。

25.根据权利要求24所述的方法,还包括:

技术总结

一种量子计算(QC)芯片模块,包括具有封装的中介层芯片。量子位芯片凸点键合到中介层芯片并且被布置成使得量子位芯片延伸超过中介层芯片的封装。中介层芯片延伸超过量子位芯片的边缘。线束连接到中介层芯片。

技术研发人员:D·亚伯拉罕,J·库特,M·库马夫

受保护的技术使用者:国际商业机器公司

技术研发日:

技术公布日:2024/12/19

- 还没有人留言评论。精彩留言会获得点赞!