基于RISC-V指令集的中断控制架构及控制方法与流程

本发明涉及处理器中断处理,特别涉及一种基于risc-v指令集的中断控制架构及控制方法。

背景技术:

1、随着芯片的性能越来越高,芯片的算力已经成为衡量一款处理器优劣的重要指标。而随着芯片的功能越来越复杂,芯片上所集成的知识产权(intellectual property,ip)也越来越繁杂。一般来说芯片的ip越多,其内核所需要处理的中断事件也就越频繁。

2、相关技术中,当有多个中断发生的时候,需要处理器能够实现中断的嵌套。传统的中断处理系统都是要借助软件实现中断嵌套时的现场保护以及现场恢复(即采用store/load这类指令来保存/恢复中断前/后的处理器寄存器状态)。

3、相关技术中的中断处理实际上会消耗极多的指令数与时钟周期,来将内核中的寄存器数据搬运到系统堆栈中。

技术实现思路

1、本发明的目的在于克服已有技术中存在的不足,从而提供中断保护与恢复现场的架构及控制方法,以减少指令数和时钟周期的消耗,提高处理器运行中断程序的效率。该技术方案如下:

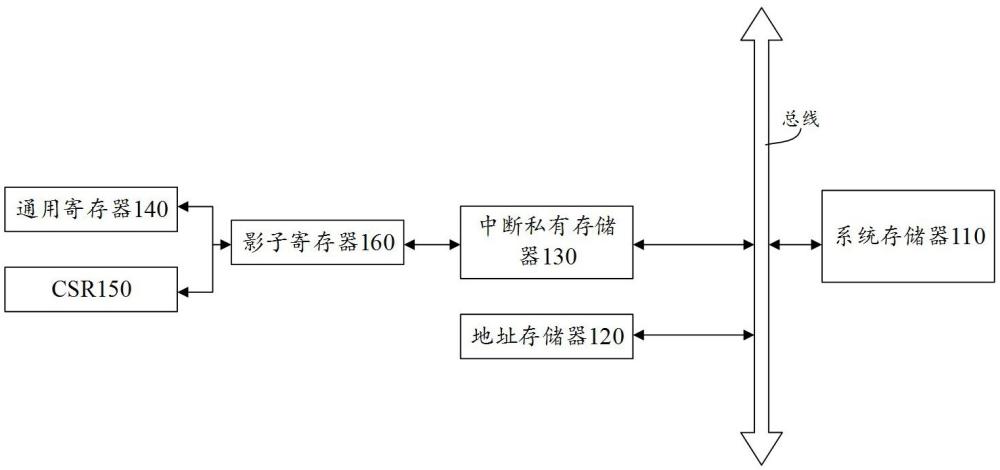

2、一方面,提供了一种基于risc-v指令集的中断控制架构及控制方法,该架构包括系统存储器、地址存储器、中断私有存储器、通用寄存器、控制与状态寄存器(control andstatus register,csr)以及影子寄存器;

3、通用寄存器以及csr分别与影子寄存器连接;

4、影子寄存器与中断私有存储器连接;

5、中断私有存储器以及地址存储器通过总线与系统存储器连接;

6、影子寄存器用于存储通用寄存器数据以及csr数据,csr数据来源于csr,通用寄存器数据来源于通用寄存器;

7、当架构处于中断压栈状态时,中断私有存储器接收影子寄存器发送的通用寄存器数据以及csr数据;

8、当架构处于中断出栈状态时,中断私有存储器向通用寄存器以及csr发送覆盖数据;

9、中断压栈状态基于中断信号触发;

10、中断出栈状态基于恢复信号触发。

11、在一个可选地实施例中,影子寄存器包括影子通用子寄存器以及影子csr子寄存器;

12、影子通用子寄存器与通用寄存器连接;

13、影子csr子寄存器与csr连接。

14、在一个可选地实施例中,影子寄存器包括通用数据存储空间以及控制和状态存储空间;

15、通用数据存储空间与通用寄存器的数据格式对应;

16、控制和状态存储空间与csr的数据格式对应。

17、在一个可选地实施例中,影子寄存器实现为d触发器。

18、另一方面,一种中断保护与恢复现场的方法,该方法应用于如上任一的中断保护与恢复现场的架构中,该方法包括:

19、中断私有存储器响应于接收到中断压栈指令,从影子寄存器中获取通用寄存器数据以及csr数据并存储,中断压栈指令与中断压栈状态对应,且基于中断信号触发;

20、和/或,

21、中断私有存储器响应于接收到中断出栈指令,基于通用寄存器数据以及csr数据生成覆盖数据;向通用寄存器以及csr发送覆盖数据,中断出栈指令与中断出栈状态对应,且基于恢复信号触发。

22、在一个可选地实施例中,中断私有存储器响应于接收到中断压栈指令,从影子寄存器中获取通用寄存器数据以及csr数据并存储之前,包括:

23、通用寄存器复制通用寄存器数据,并存储至影子寄存器中;

24、csr复制csr数据,并存储至影子寄存器中。

25、在一个可选地实施例中,中断私有存储器响应于接收到中断压栈指令,从影子寄存器中获取通用寄存器数据以及csr数据并存储之前,包括:

26、影子寄存器在一个时钟周期内从通用寄存器中获取通用寄存器数据,并在同时钟周期内从csr中获取csr数据。

27、在一个可选地实施例中,中断私有存储器中存储有历史数据;

28、该方法还包括:

29、中断私有存储器响应于接收到中断压栈指令,且中断私有存储器的存储空间达到存储阈值,从地址存储器中获取与历史数据对应的数据转移地址;

30、基于数据转移地址向系统存储器发送历史数据。

31、在一个可选地实施例中,该方法还包括:

32、中断私有存储器响应于接收到中断出栈指令,确定地址存储器中的数据转移地址的存在性;

33、中断私有存储器响应于存在数据转移地址,基于数据转移地址从系统存储器中获取历史数据并存储。

34、在一个可选地实施例中,中断压栈指令以及中断出栈指令基于risc-v指令集生成。

35、本发明提供的技术方案带来的有益效果至少包括:

36、通过在常规的系统存储器以及地址存储器的架构之外增设中断私有存储器,并对应通用寄存器与csr建立影子寄存器,作为进程中断过程中的数据缓冲寄存区,在进程中断那个过程中,架构将存在中断压栈状态与中断出栈状态,使得中断进程前寄存器中处理的数据经过影子寄存器和中断私有存储器以堆栈形式进行临时存储,并在处理器进程恢复后重新返回至对应的寄存器,在架构简单的情况下,提高处理器运行中断程序的效率。

技术特征:

1.一种基于risc-v指令集的中断控制架构,其特征在于,所述架构包括系统存储器、地址存储器、中断私有存储器、通用寄存器、控制与状态寄存器csr以及影子寄存器;

2.根据权利要求1所述的基于risc-v指令集的中断控制架构,其特征在于,所述影子寄存器包括影子通用子寄存器以及影子csr子寄存器;

3.根据权利要求1所述的基于risc-v指令集的中断控制架构,其特征在于,所述影子寄存器包括通用数据存储空间以及控制和状态存储空间;

4.根据权利要求1所述的基于risc-v指令集的中断控制架构,其特征在于,所述影子寄存器实现为d触发器。

5.一种基于risc-v指令集的中断控制架构的控制方法,其特征在于,所述方法应用于如权利要求1至4任一所述的基于risc-v指令集的中断控制架构中,所述方法包括:

6.根据权利要求5所述的基于risc-v指令集的中断控制架构的控制方法,其特征在于,所述中断私有存储器响应于接收到中断压栈指令,从所述影子寄存器中获取通用寄存器数据以及csr数据并存储之前,包括:

7.根据权利要求5所述的基于risc-v指令集的中断控制架构的控制方法,其特征在于,所述中断私有存储器响应于接收到中断压栈指令,从所述影子寄存器中获取通用寄存器数据以及csr数据并存储之前,包括:

8.根据权利要求5所述的基于risc-v指令集的中断控制架构的控制方法,其特征在于,所述中断私有存储器中存储有历史数据;

9.根据权利要求8所述的基于risc-v指令集的中断控制架构的控制方法,其特征在于,所述方法还包括:

10.根据权利要求5所述的基于risc-v指令集的中断控制架构的控制方法,其特征在于,所述中断压栈指令以及所述中断出栈指令基于所述risc-v指令集生成。

技术总结

本发明关于基于RISC‑V指令集的中断控制架构及控制方法,涉及处理器中断处理技术领域。该方法包括:中断私有存储器响应于接收到中断压栈指令,从影子寄存器中获取通用寄存器数据以及CSR数据并存储,中断压栈指令与中断压栈状态对应,且基于中断信号触发;和/或,中断私有存储器响应于接收到中断出栈指令,基于通用寄存器数据以及CSR数据生成覆盖数据;向通用寄存器以及CSR发送覆盖数据,中断出栈指令与中断出栈状态对应,且基于恢复信号触发。中断进程前寄存器中处理的数据经过影子寄存器和中断私有存储器以堆栈形式进行临时存储,并在处理器进程恢复后重新返回至对应的寄存器,在架构简单的情况下,提高处理器运行中断程序效率。

技术研发人员:于典,肖时茂

受保护的技术使用者:南京中科微电子有限公司

技术研发日:

技术公布日:2024/2/19

- 还没有人留言评论。精彩留言会获得点赞!