一种基于FPGA的多流并发资源优化方法与流程

本发明属于网络通信领域,具体涉及一种基于fpga的多流并发资源优化方法。

背景技术:

1、高带宽数据处理中,为了提高cpu以及其他asic芯片数据处理能力,将大带宽,高速率的数据业务通过高速接口传输到fpga内,由fpga完成高并发的数据处理,以卸载cpu高耗时的数据处理能力,提高数据吞吐率。然而,现有的fpga的处理方式资源占用率太高。

技术实现思路

1、(一)要解决的技术问题

2、本发明要解决的技术问题是如何提供一种基于fpga的多流并发资源优化方法,以解决现有的fpga的处理方式资源占用率太高的问题。

3、(二)技术方案

4、为了解决上述技术问题,本发明提出一种基于fpga的多流并发资源优化方法,该方法包括:fpga包括:业务分发模块和业务汇聚模块;

5、业务分发模块分三级分发模块进行分发,令一级分发模块分发i组,二级分发模块分发j组,三级分发模块分发k组;

6、令总接口带宽为dk;

7、令一级分发模块输出数据位宽为dw1,时钟为tclk1,分发i组;

8、令二级分发模块输出数据位宽为dw2,时钟为tclk2,分发j组;

9、令三级分发模块输出数据位宽为dw3,时钟为tclk3,分发k组;

10、则业务分发模块的处理带宽能力需满足如下公式:

11、dk≤i*dw1*tclk1≤i*j*dw2*tclk2≤i*j*k*dw3*tclk3;

12、业务汇聚模块分三级汇聚模块进行汇聚,令三级汇聚模块汇聚k组,二级汇聚模块汇聚j组,一级汇聚模块汇聚i组;

13、令三级汇聚模块输入数据位宽为dw3,时钟为tclk3,汇聚k组;

14、令二级汇聚模块输入数据位宽为dw2,时钟为tclk2,汇聚j组;

15、令一级汇聚模块输入数据位宽为dw1,时钟为tclk1,汇聚i组;

16、令总接口带宽为dk;

17、则业务汇聚模块的处理带宽能力需满足如下公式:

18、dk≥i*dw1*tclk1≥i*j*dw2*tclk2≥i*j*k*dw3*tclk3。

19、进一步地,一级分发模块输出数据位宽为512bit,共i=4组;二级分发模块输出数据位宽为512/i bit,共j=4组;三级分发模块输出数据位宽为512/i/j bit,共k=4组。

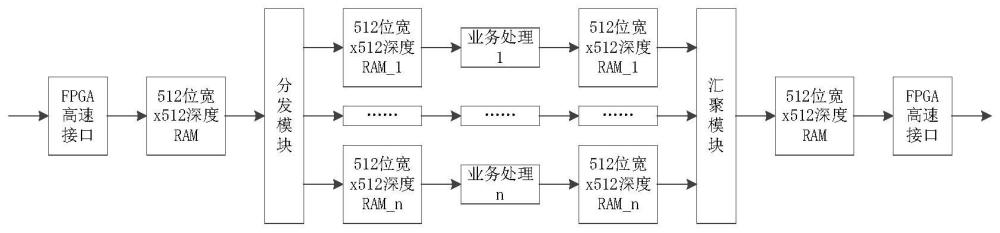

20、进一步地,一级汇聚模块输出数据位宽为512bit,共i=4组;二级汇聚模块输出数据位宽为512/i bit,共j=4组;三级汇聚模块输出数据位宽为512/i/j bit,共k=4组。

21、进一步地,fpga高速接口速率带宽为100gbps。

22、进一步地,fpga高速接口速率带宽为40gbps。

23、进一步地,业务分发模块设计包括:

24、业务数据经fpga高速接口进入fpga,通过512位宽*512深度的ram后到达一级分发模块;

25、一级分发模块将业务数据分发到512位宽*512深度的ram_1至512位宽*512深度的ram_i;

26、ram_1将业务数据传输到二级分发模块,二级分发模块将业务数据分发到512/i位宽*512深度的ram_1_1至512/i位宽*512深度的ram_1_j;ram_2至ram_i同样通过二级分发模块将业务数据分发到j组;

27、ram_1_1将业务数据传输到三级分发模块,三级分发模块将业务数据分发到512/i/j位宽*512深度的ram_1_1_1至512/i/j位宽*512深度的ram_1_1_k;ram_1_2至ram_1_j以及ram_2至ram_i对应的j组同样通过三级分发模块将业务数据分发到k组;

28、fpga对512/i/j位宽*512深度的ram_1_1_1至512/i/j位宽*512深度的ram_1_1_k中的业务数据进行业务处理。

29、进一步地,业务汇聚模块设计包括:

30、fpga内的业务数据通过512/i/j位宽*512深度的ram_1_1_1至512/i/j位宽*512深度的ram_1_1_k到达三级汇聚模块;

31、j个三级汇聚模块处理后的数据分别通过512/i位宽*512深度的ram_1_1至512/i位宽*512深度的ram_1_j到达二级汇聚模块;

32、i个二级汇聚模块处理后的数据分别通过512位宽*512深度的ram_1至512位宽*512深度的ram_i到达一级汇聚模块;

33、一级汇聚模块处理后的数据经过512位宽*512深度的ram后通过fpga高速接口发出。

34、进一步地,fpga的业务数据为基于pcie_gen2的业务数据。

35、进一步地,fpga的业务数据为基于pcie_gen3的业务数据。

36、进一步地,业务处理为对业务数据采用sm3做hash运算。

37、(三)有益效果

38、本发明提出一种基于fpga的多流并发资源优化方法,与现有技术相比,本发明提出的技术方案通过多级报文分发的方式,降低fpga的ram资源占用,降低每个业务处理模块的带宽需求以及资源占用,所以本发明具有一定的工程实用价值。

技术特征:

1.一种基于fpga的多流并发资源优化方法,其特征在于,该方法包括:fpga包括:业务分发模块和业务汇聚模块;

2.如权利要求1所述的基于fpga的多流并发资源优化方法,其特征在于,一级分发模块输出数据位宽为512bit,共i=4组;二级分发模块输出数据位宽为512/i bit,共j=4组;三级分发模块输出数据位宽为512/i/j bit,共k=4组。

3.如权利要求1所述的基于fpga的多流并发资源优化方法,其特征在于,一级汇聚模块输出数据位宽为512bit,共i=4组;二级汇聚模块输出数据位宽为512/i bit,共j=4组;三级汇聚模块输出数据位宽为512/i/j bit,共k=4组。

4.如权利要求1所述的基于fpga的多流并发资源优化方法,其特征在于,fpga高速接口速率带宽为100gbps。

5.如权利要求1所述的基于fpga的多流并发资源优化方法,其特征在于,fpga高速接口速率带宽为40gbps。

6.如权利要求1-5任一项所述的基于fpga的多流并发资源优化方法,其特征在于,业务分发模块设计包括:

7.如权利要求6所述的基于fpga的多流并发资源优化方法,其特征在于,业务汇聚模块设计包括:

8.如权利要求7所述的基于fpga的多流并发资源优化方法,其特征在于,fpga的业务数据为基于pcie_gen2的业务数据。

9.如权利要求7所述的基于fpga的多流并发资源优化方法,其特征在于,fpga的业务数据为基于pcie_gen3的业务数据。

10.如权利要求7所述的基于fpga的多流并发资源优化方法,其特征在于,业务处理为对业务数据采用sm3做hash运算。

技术总结

本发明涉及一种基于FPGA的多流并发资源优化方法,属于网络通信领域。本发明针对现有的FPGA的处理方式资源占用率太高的问题,将大带宽,高速率的数据业务通过FPGA高速接口转换为低速率,高数据位宽的数据,以优化FPGA的时钟;通过多级报文分发模块,实现高数据位宽的数据降低为低位宽的数据,以降低FPGA的RAM、LUT、FF等资源占用;通过多级报文汇聚模块,实现数据的还原,并通过FPGA高速接口输出。本发明通过多级报文分发的方式,降低了FPGA的RAM资源占用,降低了每个业务处理模块的带宽需求以及资源占用。

技术研发人员:陈俊来

受保护的技术使用者:北京左江科技股份有限公司

技术研发日:

技术公布日:2024/4/29

- 还没有人留言评论。精彩留言会获得点赞!