一种数据解串处理装置、处理方法及芯粒集成系统与流程

本发明属于电子电路,特别涉及一种数据解串处理装置、处理方法及芯粒集成系统。

背景技术:

1、随着高性能计算对算力要求的不断提高,需要采用芯粒(chiplet)集成的系统来满足高性能的计算需求。在芯粒集成的系统中,不同芯粒之间需要进行高频次的数据交互以完成相关计算。但芯粒集成的系统工作时钟频率会远小于芯粒高速数据接口的数据传输速率,故在接收到数据后,需要对数据进行解串。且由于系统工作时钟和高速串行时钟不同步,还需要对数据进行同步处理。

2、但是在对数据同步过程中需要花费额外的时钟周期,这一开销将显著增加数据在传输通路上的延时,难以满足芯粒间高速数据传输的低延时要求。同时在进行数据跨时钟域处理时会增加芯粒的复杂度和成本,牺牲系统的性能。

技术实现思路

1、本发明的目的在于提供数据解串处理装置、处理方法及芯粒集成系统,可节省硬件资源,提高系统的性能,且满足芯粒之间数据传输的低延时需求。

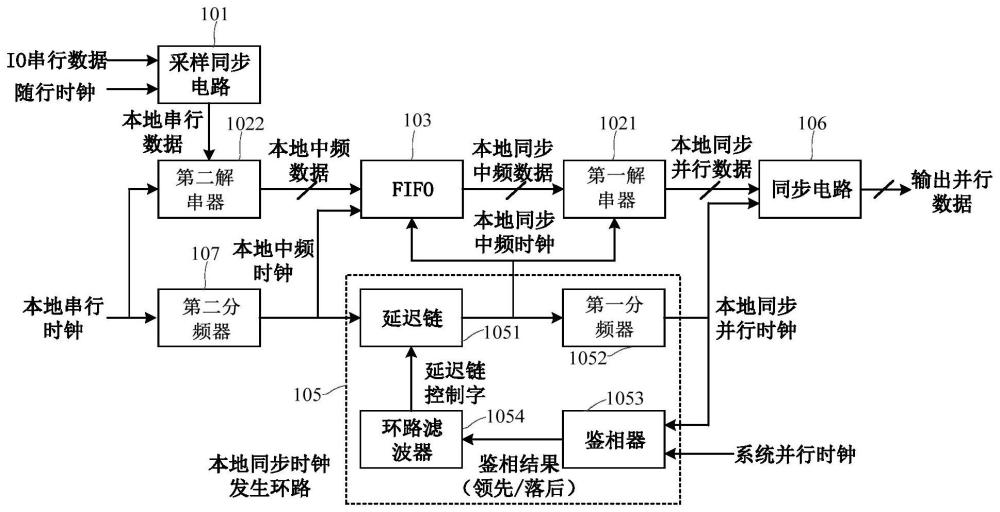

2、为实现上述目的,本发明提供了的数据解串处理装置,至少包括:

3、本地同步时钟发生环路,依据本地串行时钟和系统并行时钟,形成本地同步时钟和本地同步并行时钟,且所述本地同步时钟、所述本地同步并行时钟与所述系统并行时钟同步;

4、先入先出堆栈,输入串行数据或本地中频数据,并将所述本地同步时钟作为数据输出时钟,完成输入数据的跨时钟域处理,形成本地同步数据;

5、第一解串器,依据所述本地同步时钟,将所述本地同步数据转换为本地同步并行数据;以及

6、同步电路,在所述本地同步并行时钟下,将所述本地同步并行数据转换为并行数据。

7、在本发明一实施例中,所述本地同步时钟环路包括延迟链,所述本地串行时钟输入所述延迟链,获得所述本地同步时钟,所述本地同步时钟为本地同步串行时钟。

8、在本发明一实施例中,所述本地同步时钟环路包括第一分频器,所述本地同步时钟进入所述第一分频器产生所述本地同步并行时钟。

9、在本发明一实施例中,所述本地同步时钟环路包括鉴相器,所述鉴相器将所述本地同步并行时钟与所述系统时钟进行相位比较,并依据比较结果进行鉴相输出。

10、在本发明一实施例中,所述本地同步时钟环路包括环路滤波器,所述环路滤波器依据所述鉴相输出,输出延迟链控制字,控制所述延迟链的延迟时间。

11、在本发明一实施例中,所述数据解串处理装置包括第二分频器,所述串行时钟进入所述第二分频器产生所述本地中频时钟,并将所述本地中频时钟输入所述延迟链,获取所述本地同步时钟,所述本地同步时钟为本地同步中频时钟。

12、在本发明一实施例中,所述数据解串处理装置包括采样同步电路,所述采样同步电路采样所述串行数据,形成本地串行数据。

13、在本发明一实施例中,所述数据解串处理装置包括第二解串器,所述第二解串器在所述本地串行时钟下,将所述本地串行数据解串为所述本地中频数据。

14、本发明还包括一种数据解串处理方法,包括以下步骤:

15、依据本地串行时钟和系统并行时钟,形成本地同步时钟和本地同步并行时钟,且所述本地同步时钟、所述本地同步并行时钟与所述系统并行时钟同步;

16、将所述本地同步时钟作为数据输出时钟,完成输入串行数据或本地中频数据的跨时钟域处理,形成本地同步数据;

17、依据所述本地同步时钟,将所述本地同步数据转换为本地同步并行数据;以及

18、在所述本地同步并行时钟下,将所述本地同步并行数据转换为并行数据。

19、本发明还提供一种芯粒集成系统,包括多个芯粒,且芯粒之间通过高速数据接口传输数据,如权利要求上任意一项所述数据解串处理装置集设置在所述芯粒的电气物理层中。

20、综上所述,本发明提供的数据解串处理装置、处理方法及芯粒集成系统,采用的跨时钟域处理方法是在解串器之前进行跨时钟域处理,是在串行时钟(快时钟)的工作频率上做跨时钟域处理,由此产生的延时开销相比现有技术显著降低,能够很好地满足芯粒间数据传输的低延时需求。对串行数据进行跨时钟域处理,所需的硬件资源相比现有技术显著降低,具有较好的成本优势。对串行数据进行跨时钟域处理,减少了物理层内部的信号线数量,有利于芯片布局布线,提高芯片性能。在电气物理层内部插入先入先出堆栈,在逻辑层和电气物理层之间无需额外的先入先出堆栈控制信号,简化了逻辑层和电气物理层之间的接口定义,有利于实现高性能的逻辑层设计。本发明提供数据解串处理装置、处理方法及芯粒集成系统还可以灵活地选取跨时钟域操作的工作频率,有利于合理地处理性能和硬件开销的折中,为高速数据接口的整体方案提供更大的设计空间。不同于现有技术将输出数据直接同步到系统并行时钟,本发明将输出数据同步到与系统时钟同步后的本地并行时钟,在确保与系统时钟同步的基础上保留了微调时钟相位的空间,从而更有利于逻辑层的时序控制。

技术特征:

1.一种数据解串处理装置,其特征在于,至少包括:

2.根据权利要求1所述的一种数据解串处理装置,其特征在于,所述本地同步时钟环路包括延迟链,所述本地串行时钟输入所述延迟链,获得所述本地同步时钟,所述本地同步时钟为本地同步串行时钟。

3.根据权利要求1所述的一种数据解串处理装置,其特征在于,所述本地同步时钟环路包括第一分频器,所述本地同步时钟进入所述第一分频器产生所述本地同步并行时钟。

4.根据权利要求3所述的一种数据解串处理装置,其特征在于,所述本地同步时钟环路包括鉴相器,所述鉴相器将所述本地同步并行时钟与所述系统时钟进行相位比较,并依据比较结果进行鉴相输出。

5.根据权利要求4所述的一种数据解串处理装置,其特征在于,所述本地同步时钟环路包括环路滤波器,所述环路滤波器依据所述鉴相输出,输出延迟链控制字,控制所述延迟链的延迟时间。

6.根据权利要求2所述的一种数据解串处理装置,其特征在于,所述数据解串处理装置包括第二分频器,所述串行时钟进入所述第二分频器产生所述本地中频时钟,并将所述本地中频时钟输入所述延迟链,获取所述本地同步时钟,所述本地同步时钟为本地同步中频时钟。

7.根据权利要求1所述的一种数据解串处理装置,其特征在于,所述数据解串处理装置包括采样同步电路,所述采样同步电路采样所述串行数据,形成本地串行数据。

8.根据权利要求7所述的一种数据解串处理装置,其特征在于,所述数据解串处理装置包括第二解串器,所述第二解串器在所述本地串行时钟下,将所述本地串行数据解串为所述本地中频数据。

9.一种数据解串处理方法,其特征在于,包括以下步骤:

10.一种芯粒集成系统,其特征在于,包括多个芯粒,且芯粒之间通过高速数据接口传输数据,如权利要求1至8任意一项所述数据解串处理装置设置在所述芯粒的电气物理层中。

技术总结

本发明提供一种数据解串处理装置、处理方法及芯粒集成系统,且所述数据解串处理装置包括:本地同步时钟发生环路,依据本地串行时钟和系统并行时钟,形成本地同步时钟和本地同步并行时钟;先入先出堆栈,输入串行数据或本地中频数据,并将所述本地同步时钟作为数据输出时钟,完成输入数据的跨时钟域处理,形成本地同步数据;第一解串器,依据所述本地同步时钟,将所述本地同步数据转换为本地同步并行数据;以及同步电路,在所述本地同步并行时钟下,将所述本地同步并行数据转换为并行数据。通过本发明提供的一种数据解串处理装置、处理方法及芯粒集成系统,可节省硬件资源,提高系统的性能,且满足芯粒之间数据传输的低延时需求。

技术研发人员:王彧,田陌晨,温德鑫

受保护的技术使用者:奇异摩尔(上海)集成电路设计有限公司

技术研发日:

技术公布日:2024/5/8

- 还没有人留言评论。精彩留言会获得点赞!