考虑时延的可布线性驱动轨道分配方法

本发明属于超大规模集成电路计算机辅助设计,具体涉及考虑时延的可布线性驱动轨道分配方法。

背景技术:

1、布线是超大规模集成电路(very large scale integration,vlsi)设计中最关键和最耗时的环节之一,其结果直接影响芯片的性能、可靠性和良品率。该设计环节通常分为两个阶段:分别为总体布线和详细布线。可布线性作为布线环节中最关键的设计目标之一,对其实现有效的优化是至关重要的。然而,在现代vlsi设计中,电路复杂度地不断提高以及芯片尺寸地不断缩小,导致可用的布线区域越来越有限,可布线性优化也相应地变得更加具有挑战性。具体而言,随着详细布线的复杂性不断上升以及网络密度的不断增加,将总体布线的结果与详细布线要求的结果相匹配变得越来越困难。为了缓解详细布线的压力,同时实现有效的可布线性估计,技术人员引入了轨道分配阶段,以更好地匹配总体布线和详细布线。

2、总体布线阶段确定所有线网的布线方案,该方案在保证集成电路设计的可布线性基础上最小化互连成本。轨道分配阶段将总体布线器提供的布线方案中的导线分配至轨道。在多层布线问题中,同一层内部的布线方向是一致的(水平或垂直方向),相邻层之间的布线方向是相交的。

3、随着集成电路规模的不断扩大,芯片上的元器件数量以及器件之间的互连关系变得越来越复杂。复杂的互连关系使得线网中信号传输的总长度显著增加,导致电路信号传输的总时延也相应增加。此外,互连线网之间的交叉耦合电容通过线网传输的信号产生显著的噪声,从而严重影响了电路性能和可靠性,因此,互连时延也是评价布线方案可布线性的指标之一。由于时延的增大会降低数据传输的准确性且增加芯片的功率消耗。因此在轨道分配阶段如何有效降低信号的传输时延以进一步提高可布线性,从而优化芯片的性能和可靠性同样是至关重要的。

技术实现思路

1、针对现有技术的缺陷和不足,本发明提供一种考虑时延的可布线性轨道分配方法,旨在同时减少线长成本、障碍成本和重叠成本。首先,提出了一种考虑时延的可布线性驱动轨道分配的整数线性规划(integer linear programming,ilp)模型,并给出了相应的数学表达,以便找到最佳的轨道分配方案。其次,提出了一种关键导线控制策略,该策略考虑了在一个线网中影响时延的两个主要因素,从而在模型的优化过程中减少时延。最后,通过对ilp模型进行求解以获得优质的轨道分配方案。

2、本发明解决其技术问题具体采用的技术方案是:

3、一种考虑时延的可布线性驱动轨道分配方法,其特征在于:

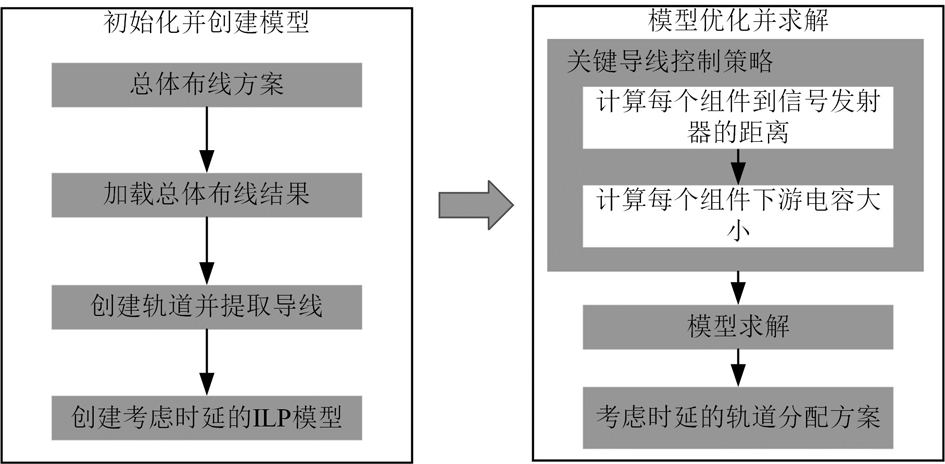

4、包括初始化并创建模型阶段和模型优化并求解阶段;输入为总体布线方案,输出为一个考虑时延的轨道分配方案:

5、在所述初始化并创建模型阶段,首先初始化轨道分配环境,根据每层导线的宽度和导线之间的最小间距要求为每个布线带创建轨道,并从全局线网和局部线网中为每个布线带提取导线;接着,以布线带为单位创建考虑时延的整数线性规划模型;

6、在模型优化并求解阶段,采用关键导线控制策略,并进行求解;以输出考虑时延的轨道分配方案。

7、进一步地,采用elmore时延计算模型评估线网的时延性能。

8、进一步地,以一个布线带为单位对考虑时延的轨道分配问题建模,获得考虑时延的整数线性规划模型的目标函数如公式(a)-(e)所示,其中(b)是障碍成本,(c)是重叠成本,(d)是线长成本,(e)是时延;约束如公式(f)-(i)所示,其中(f)是排他性约束,(g)是分段计算重叠数量,(h)是重叠数量合法性约束,(i)限制了决策变量是一个二进制变量,olen(i,b)表示ip集合中iroute i与bt集合中障碍物b之间的重叠长度;slentk表示轨道t的第k段的段长;distance(xit,pin,j)表示iroute i放在轨道t上与i所在线网内其他组件的最短距离,i,j,pin同属于i所在的线网ni;

9、

10、进一步地,所述关键导线控制策略具体在优化线网时延时考虑以下两个条件:

11、(1)该线网中,所有导线与信号发射器的距离;

12、(2)该线网中,所有导线具有的下游电容的大小。

13、进一步地,在模型优化过程中,针对一个线网n,使用以下式子对线网中的所有组件计算时延成本;通过对每个组件进行时延成本的计算,以了解整个线网的时延状况,进而针对性地进行优化调整;

14、delay(com)=distance(s,com)+down(ir)

15、其中,distance(s,com)表示组件com到信号发射器s的距离;down(ir)表示导线ir的下游电容。

16、进一步地,在模型优化过程中,在计算时延成本的同时,还需要综合考虑其他因素,使用四个成本的加权和进行评估,评估函数如下式所示;

17、eva(ir)=α×olpcostir+β×blkcostir+χ×wlcost+δ×delayir

18、其中,α、β、χ和δ为用户自定义参数;olpcost是重叠成本;blkcost是障碍成本;wlcost是线长成本;delay是时延。

19、相比于现有技术,本发明及其优选方案有效降低信号的传输时延以进一步提高可布线性,从而优化芯片的性能和可靠性。

技术特征:

1.一种考虑时延的可布线性驱动轨道分配方法,其特征在于:

2.根据权利要求1所述的考虑时延的可布线性驱动轨道分配方法,其特征在于:采用elmore时延计算模型评估线网的时延性能。

3.根据权利要求2所述的考虑时延的可布线性驱动轨道分配方法,其特征在于:

4.根据权利要求2所述的考虑时延的可布线性驱动轨道分配方法,其特征在于:

5.根据权利要求4所述的考虑时延的可布线性驱动轨道分配方法,其特征在于:

6.根据权利要求4所述的考虑时延的可布线性驱动轨道分配方法,其特征在于:

技术总结

本发明提供一种考虑时延的可布线性驱动轨道分配方法,旨在同时减少线长成本、障碍成本和重叠成本。首先,提出了一种考虑时延的可布线性驱动轨道分配的整数线性规划(Integer Linear Programming,ILP)模型,并给出了相应的数学表达,以便找到最佳的轨道分配方案。其次,提出了一种关键导线控制策略,该策略考虑了在一个线网中影响时延的两个主要因素,从而在模型的优化过程中减少时延。最后,通过对ILP模型进行求解以获得优质的轨道分配方案。

技术研发人员:刘耿耿,陈子阳,蔡华洋

受保护的技术使用者:福州大学

技术研发日:

技术公布日:2024/5/16

- 还没有人留言评论。精彩留言会获得点赞!