基于FPGA的原型验证平台的高频差分系统的制作方法

本申请涉及仿真验证,特别是涉及基于fpga的原型验证平台的高频差分系统。

背景技术:

1、risc-v处理器整系统仿真验证,通常在完成模块级和系统级仿真测试后,会进行基于fpga的原型验证。fpga的主频一般在100mhz左右,不过高性能处理器的fpga原型验证中,由于处理器的逻辑和存储资源占用较大,以及fpga外围通信接口影响,fpga实际能运行高性能处理器的频率大概在50mhz。假设在fpga平台上的处理器内核运行一万亿指令数的spec跑分测试程序,且处理器ipc为1,那么只需要5.5h即可完成原型验证,时间成本完全可以接受。不过,在fpga上运行开发的处理器内核时,一般只通过串口将信息上传到上位机进行显示,若发现打印出错,那么必须通过导出波形去定位问题。新的难点在于,在基于fpga的内核上跑应用程序时,最终的打印错误可能来自于很久以前的累积错误,这就导致需要追查的时间线不可控,从而使用fpga的探针技术去抓取波形定位问题时,无法预知需要抓哪个时间段的波形,只能一次次迭代逼近问题根源,从而定位问题速度很慢。

2、不同fpga的资源不同,导致所能保存的探针信号长度和信号个数都不一样,这也大大限制了fpga平台上定位高性能处理器运行复杂应用时的问题。

技术实现思路

1、本申请提供了基于fpga的原型验证平台、服务器及差分测试系统,能够减少传输流量,提高服务器的差分测试效率。

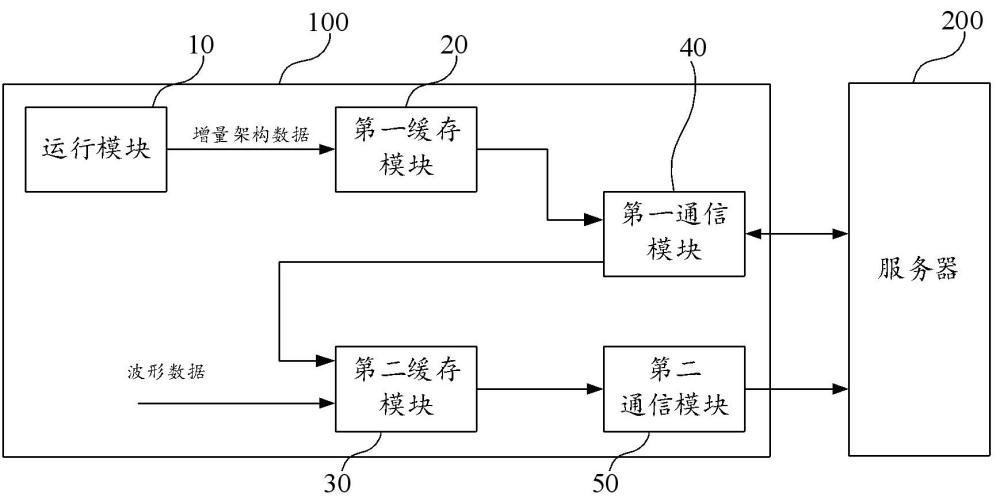

2、第一方面,本申请提供一种基于fpga的原型验证平台,该原型验证平台包括:运行模块,用于运行被测处理器内核;第一缓存模块,耦接运行模块,用于接收运行模块发送的运行被测处理器内核产生的增量架构数据;第二缓存模块,用于缓存被测处理器内核运行过程中作为探针信号的目标信号的波形数据;第一通信模块,耦接第一缓存模块、第二缓存模块和服务器,用于将增量架构数据发送至服务器,以使服务器根据增量架构数据进行差分测试;第一通信模块还用于接收服务器发送的触发信号;触发信号由服务器在差分测试结果异常时产生;第二缓存模块响应于触发信号,通过第二通信模块将目标信号的波形数据导出至服务器。

3、其中,运行模块用于在被测处理器内核指令退休时,将因本周期指令组退休而导致变化的逻辑寄存器值、控制状态寄存器、提交指令数作为增量架构数据发送至第一缓存模块。

4、其中,第一缓存模块的读端口设置预设数量个读数据缓冲条目,每一读数据缓冲条目用于预读缓存相应的增量架构数据的数据;第一通信模块用于从预设数量个读数据缓冲条目中将增量架构数据的数据并行读出发送至服务器。

5、其中,响应于尾指针与头指针的差值大于第一预设值,第一通信模块以头指针的位置开始,并行读出预设数量组数据发送至服务器,并更新头指针。

6、其中,在读指针和写指针一致,且预设周期内运行模块未发送新的增量架构数据时,第一通信模块响应于尾指针与头指针的差值大于第二预设值,第一通信模块读出头指针的位置至尾指针前一位置之间的数据发送至服务器,并将尾指针更新为头指针。

7、其中,第一通信模块采用udp协议传输数据。

8、其中,第一通信模块为万兆网卡。

9、其中,第二缓存模块按照时间顺序循环缓存目标信号的波形数据。

10、其中,第二缓存模块的最小容量由数据读写时间、上下行网络延时、报文打包时间、服务器差分测试时间和fpga单个周期所有要保存的信号总位宽决定。

11、其中,目标信号包括被测处理器内核中的分支预测、取指、解码、重命名、分派、执行、访存、虚拟内存管理、三级缓存对应的信号。

12、其中,被测处理器内核基于risc-v指令集构建。

13、第二方面,本申请提供一种服务器,该服务器包括:第三通信模块,用于与如第一方面提供的基于fpga的原型验证平台的第一通信模块通信连接,用于接收原型验证平台发送的增量架构数据;指令集模拟器,与第三通信模块通信连接,用于根据增量架构数据进行差分测试;第三通信模块还用于在差分测试结果异常时产生触发信号并发送至原型验证平台,以使原型验证平台响应于触发信号,通过第二通信模块将第二缓存模块中缓存的被测处理器内核运行过程中作为探针信号的目标信号的波形数据导出至服务器。

14、第三方面,本申请提供一种基于fpga的原型验证平台的差分测试系统,该差分测试系统包括:基于fpga的原型验证平台和服务器;基于fpga的原型验证平台如第一方面提供的基于fpga的原型验证平台,服务器如第二方面提供的服务器。

15、本申请的有益效果是:区别于现有技术的情况,本申请提供的基于fpga的原型验证平台、服务器及差分测试系统,该原型验证平台利用第一缓存模块缓存运行模块发送的运行被测处理器内核产生的增量架构数据,并将该增量架构数据通过第一通信模块发送至服务器中进行差分测试,以此减少传输流量,提高服务器的差分测试效率,且利用第二缓存模块缓存被测处理器内核运行过程中作为探针信号的目标信号的波形数据,以便于在服务器差分测试结果异常时,向服务器及时发送目标信号的波形数据,使服务器能够快速定位,节省定位异常时间。

技术特征:

1.一种基于fpga的原型验证平台,其特征在于,所述原型验证平台包括:

2.根据权利要求1所述的原型验证平台,其特征在于,所述运行模块用于在所述被测处理器内核指令退休时,将因本周期指令组退休而导致变化的逻辑寄存器值、控制状态寄存器、提交指令数作为所述增量架构数据发送至所述第一缓存模块。

3.根据权利要求1所述的原型验证平台,其特征在于,所述第一缓存模块的读端口设置预设数量个读数据缓冲条目,每一读数据缓冲条目用于预读缓存相应的增量架构数据的数据;

4.根据权利要求3所述的原型验证平台,其特征在于,响应于尾指针与头指针的差值大于第一预设值,所述第一通信模块以所述头指针的位置开始,并行读出预设数量组数据发送至所述服务器,并更新所述头指针。

5.根据权利要求3所述的原型验证平台,其特征在于,在读指针和写指针一致,且预设周期内所述运行模块未发送新的增量架构数据时,所述第一通信模块响应于尾指针与头指针的差值大于第二预设值,所述第一通信模块读出头指针的位置至尾指针前一位置之间的数据发送至所述服务器,并将所述尾指针更新为所述头指针。

6.根据权利要求1所述的原型验证平台,其特征在于,所述第二缓存模块的最小容量由数据读写时间、上下行网络延时、报文打包时间、服务器差分测试时间和fpga单个周期所有要保存的信号总位宽决定。

7.根据权利要求1-6任一项所述的原型验证平台,其特征在于,所述目标信号包括所述被测处理器内核中的分支预测、取指、解码、重命名、分派、执行、访存、虚拟内存管理、三级缓存对应的信号。

8.根据权利要求1-6任一项所述的原型验证平台,其特征在于,所述被测处理器内核基于risc-v指令集构建。

9.一种服务器,其特征在于,所述服务器包括:

10.一种基于fpga的原型验证平台的差分测试系统,其特征在于,所述差分测试系统包括:基于fpga的原型验证平台和服务器;所述基于fpga的原型验证平台如权利要求1-8任一项所述的基于fpga的原型验证平台,所述服务器如权利要求9所述的服务器。

技术总结

本申请公开了基于FPGA的原型验证平台、服务器及差分测试系统。该原型验证平台包括:运行模块用于运行被测处理器内核;第一缓存模块用于接收运行模块发送的运行被测处理器内核产生的增量架构数据;第二缓存模块用于缓存被测处理器内核运行过程中作为探针信号的目标信号的波形数据;第一通信模块用于将增量架构数据发送至服务器,以使服务器根据增量架构数据进行差分测试;第一通信模块还用于接收服务器发送的触发信号;触发信号由服务器在差分测试结果异常时产生;第二缓存模块响应于触发信号,通过第二通信模块将目标信号的波形数据导出至服务器。通过上述方式,能够减少传输流量,提高服务器的差分测试效率。

技术研发人员:廖述京

受保护的技术使用者:广东省新一代通信与网络创新研究院

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!