一种适用于细窄型floorplan的IP级联的帧级通信方法和通信装置与流程

本发明属于半导体显示驱动与图像处理领域,尤其涉及一种适用于细窄型floorplan的ip级联的帧级通信方法和通信装置。

背景技术:

1、随着智能终端(如智能手机)以及可穿戴设备(如vr眼镜)的大规模普及,为了满足电子产品轻薄性、便携性的使用特点,对电子产品内部所使用的芯片也提出了越来越严苛的物理尺寸要求。比如现在的电子产品多数带有led屏幕或oled屏幕,而驱动屏幕显示的显示驱动芯片(ddic,display drive ic)由于位置要求以及需要驱动整个显示面板的像素显示电路,往往设计成呈现细窄型物理尺寸的芯片结构。

2、在这种特定尺寸布局的芯片中往往需要多个ispip级联进行视频图像处理,多个ip(intellectual property)之间也需要经常传输大量帧级数据,在这种特定floorplan的约束下,ip之间传输数据采用点对点直接传输或者按照普通总线协议进行传输,都存在着通信速率低、ip之间走线过多、布局布线难度高等缺点,最后导致芯片产品难以释放全部性能,或因面积原因增大芯片设计尺寸,或因功耗原因而影响产品的续航能力,从而降低芯片的性能和性价比,并最终严重影响用户使用体验。

3、因此,如何在细窄型floorplan布局的物理约束下和ip级联的逻辑约束下,设计出一种能够满足按帧传递数据的总线协议,并兼顾面积、功耗和通信速率的要求,是一个亟待解决的问题。

技术实现思路

1、有鉴于此,本发明提供一种适用于细窄型floorplan的ip级联的帧级通信方法和通信装置,以此解决在芯片细窄型floorplan物理布局以及ip级联场景下的总线通信难以兼顾面积、功耗、通信速率和后端物理设计的问题。

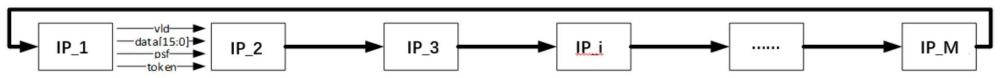

2、为实现上述目的,本发明提供了一种适用于细窄型floorplan的ip级联的帧级通信方法,所述细窄型floorplan由ip_1、ip_2、……、ip_i级联而成,其中,1≤i≤m,m为正整数,包括以下步骤:

3、步骤(1),通信编码:对所述细窄型floorplan中数据链路的各级ip及各级ip需要通信的数据包进行编码,以形成i个数据包集,记为n_1、n_2、……、n_i;

4、步骤(2),总线通信:根据帧级信号和通信开始信号启动总线通信,总线在通信过程中呈现分布式控制;

5、其中,在通信过程中,所述ip_i按照总线协议将数据包集n_i传输给后级ip_i+1,所述ip_i+1按照总线协议将数据包集n_i+1传输至再后一级ip_i+2。

6、进一步的,在所述步骤(2)中,所述ip_i+1对所述数据包集n_i中本级ip接收的数据包进行校验并截留。

7、进一步的,在所述步骤(2)中,所述ip_i+1在所述数据包集n_i的基础上截留和/或插入所述ip_i+1需要发送的数据包以形成所述新的数据包集n_i+1。

8、进一步的,所述ip_i为asic、fpga或eda任一种工具中的ip。

9、进一步的,所述ip_i为自行设计的ip。

10、进一步的,所述ip_1、ip_2、……、ip_i为菊花链串行连接形式,或,环形连接形式。

11、进一步的,所述帧级信号为视频图像处理(isp)中的场同步信号,或,需要进行周期性数据处理的周期性同步信号。

12、进一步的,所述帧级信号为仅上电时需要处理的同步信号。

13、进一步的,所述总线通信为asic/fpga芯片内部数字设计中ip之间的总线通信。

14、进一步的,所述总线通信为半双工通信。

15、进一步的,所述总线协议包含总线控制信号和总线数据信号。

16、进一步的,所述校验的算法为错误纠正码ecc或循环冗余校验码crc。

17、同时,本发明还提供一种采用上述通信方法的通信装置,所述细窄型floorplan由ip_1、ip_2、……、ip_i级联而成,其中,1≤i≤m,m为正整数。

18、进一步的,所述ip_1、ip_2、……、ip_i为菊花链串行连接形式,或,环形连接形式。

19、与现有技术相比,本发明具有以下有益效果:

20、本发明在细窄型floorplan布局的芯片中,ip之间需要按帧或定时进行大量数据通信的场景下,可以显著降低不同ip之间的连线数量,减少placeand route绕线时的数量,降低绕线的难度,从而降低芯片后端physical design工作的难度;同时该通信方法在硬件上可对主从数量,数据传输的长度和类别进行配置,具有总线数量少、协议简洁等优点。

技术特征:

1.一种适用于细窄型floorplan的ip级联的帧级通信方法,所述细窄型floorplan由ip_1、ip_2、……、ip_i级联而成,其中,1≤i≤m,m为正整数,其特征在于,包括以下步骤:

2.如权利要求1所述的方法,其特征在于,在所述步骤(2)中,所述ip_i+1对所述数据包集n_i中本级ip接收的数据包进行校验并截留。

3.如权利要求2所述的方法,其特征在于中,在所述步骤(2)中,所述ip_i+1在所述数据包集n_i的基础上截留和/或插入所述ip_i+1需要发送的数据包以形成所述新的数据包集n_i+1。

4.如权利要求1所述的方法,其特征在于,所述ip_i为asic、fpga或eda任一种工具中的ip。

5.如权利要求1所述的方法,其特征在于,所述ip_i为自行设计的ip。

6.如权利要求1所述的方法,其特征在于,所述ip_1、ip_2、……、ip_i为菊花链串行连接形式,或,环形连接形式。

7.如权利要求1所述的方法,其特征在于,所述帧级信号为视频图像处理(isp)中的场同步信号,或,需要进行周期性数据处理的周期性同步信号。

8.如权利要求1所述的方法,其特征在于,所述帧级信号为仅上电时需要处理的同步信号。

9.如权利要求1所述的方法,其特征在于,所述总线通信为asic/fpga芯片内部数字设计中ip之间的总线通信。

10.如权利要求1所述的方法,其特征在于,所述总线通信为半双工通信。

11.如权利要求1所述的方法,其特征在于,所述总线协议包含总线控制信号和总线数据信号。

12.如权利要求2所述的方法,其特征在于,所述校验的算法为错误纠正码ecc或循环冗余校验码crc。

13.一种采用如权利要求1-12任一项所述的一种适用于细窄型floorplan的ip级联的帧级通信方法的通信装置,其特征在于,所述细窄型floorplan由ip_1、ip_2、……、ip_i级联而成,其中,1≤i≤m,m为正整数。

14.如权利要求13所述的通信装置,其特征在于,所述ip_1、ip_2、……、ip_i为菊花链串行连接形式,或,环形连接形式。

技术总结

一种适用于细窄型floorplan的IP级联的帧级通信方法和通信装置,通过通信编码和总线通信的步骤,在细窄型floorplan布局的芯片中不同IP间实现大量数据的通信,从而显著降低不同IP之间的连线数量,减少Placeand Route绕线时的数量,降低绕线的难度,从而降低芯片后端Physical Design工作的难度;同时该通信方法在硬件上可对主从数量,数据传输的长度和类别进行配置,具有总线数量少、协议简洁等优点。

技术研发人员:秦佳祥,叶选新,蔡剑,蔡杰羽,吴振锋

受保护的技术使用者:苇渡半导体(上海)有限公司

技术研发日:

技术公布日:2024/12/17

- 还没有人留言评论。精彩留言会获得点赞!